NVIDIA Jetson Nano DG-09502-001_v2.1 | 28

Chapter 7. Display

Tegra X1 Embedded designs can select from several display options including MIPI DSI and

eDP for embedded displays, and HDMI or DP for external displays. The maximum number of

simultaneous displays supported by Jetson Nano is two.

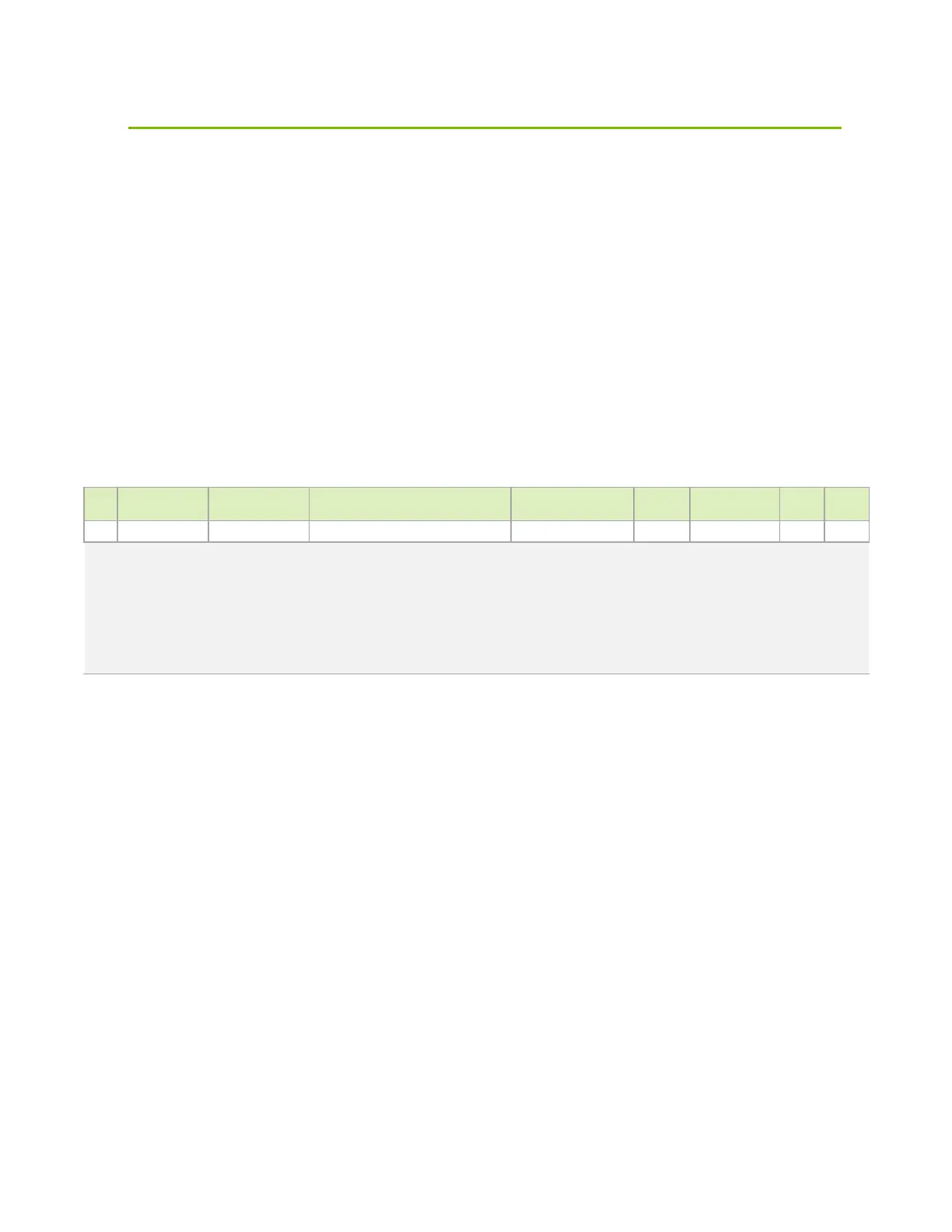

Table 7-1. Jetson Nano Display General Pin Description

Pin # Module Pin Name Tegra X1 Signal Usage/Description

Usage on NVIDIA DevKit

Carrier Board

Direction Pin Type

Code

Power-on

Reset

206 GPIO07 LCD_BL_PWM GPIO or Pulse Width Modulation signal Ex pansion header Output CMOS – 1.8V ST pd

Notes:

1. In the Type/Dir column, Output is from Jetson Nano. Input is to Jetson Nano. Bidir is for Bidirectional signals.

2. The direction of GPIO07 is true when used for this function. Otherwise as a GPIO, the direction is bidirectional.

3. The MPIO Pad Codes are described in the

Tegra X1 SoC Technical Reference Manual

“Multi-Purpose I/O Pins and Pin Multiplexing

(PinMux)” section for details.

4. The Power-on Reset State column indicates the pin state when reset is active and when it is deactivated before any changes are made by

software. “z” is tristate, pu/pd indicates internal weak pull-up/down resistor is enabled, 1/0 indicates actively driven high/low.

7.1 MIPI DSI

Tegra supports two total MIPI DSI data lanes and a single clock lane. Each data lane has a

peak bandwidth up to 1.5Gbps.

Loading...

Loading...