MIPI CSI Video Input

NVIDIA Jetson Nano DG-09502-001_v2.1 | 47

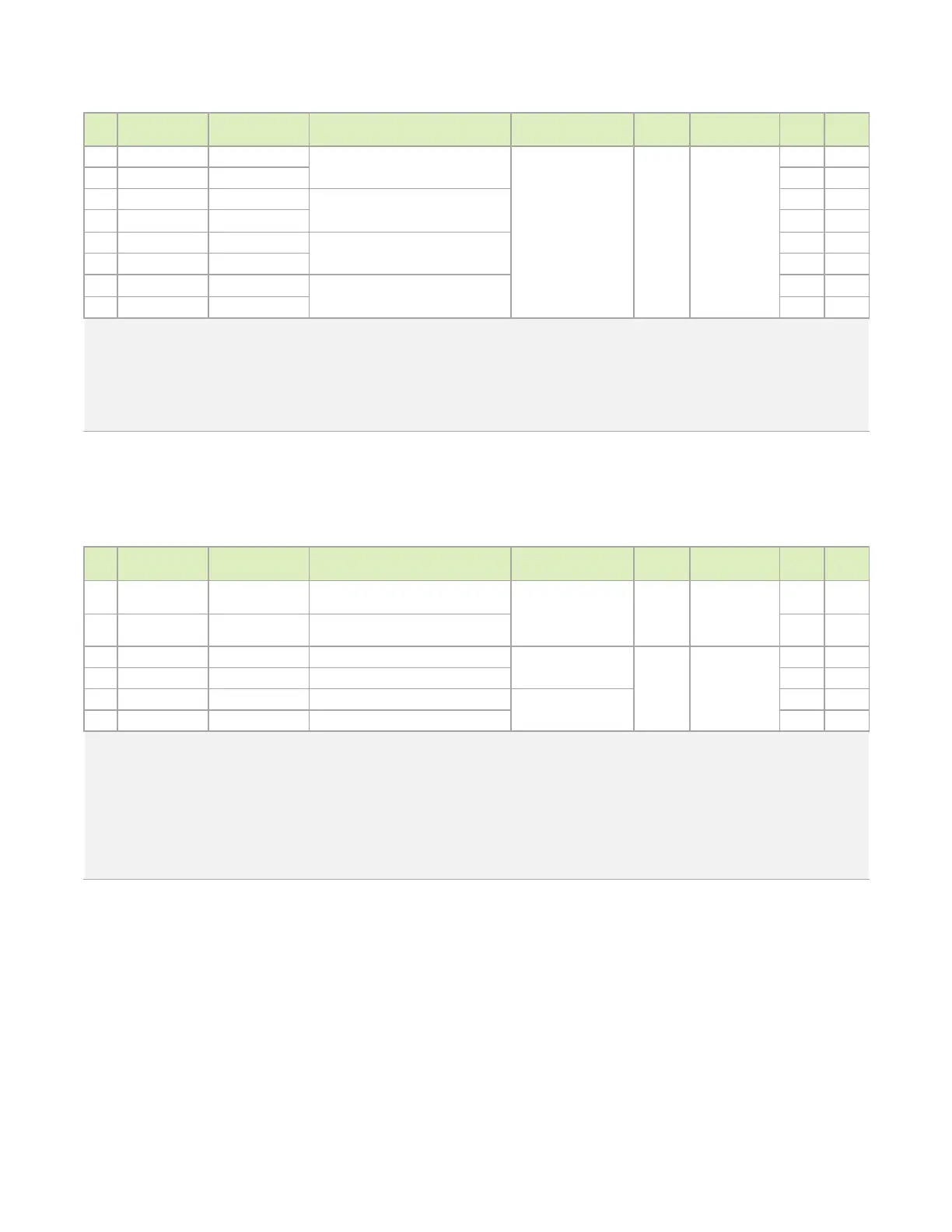

Pin # Module Pin Name Tegra X1 Signal Usage/Description

Usage on NVIDIA DevKit

Carrier Board

Direction Pin Type

Code

Power-on

Reset

46 CSI4_D0_N CSI_C_D0_N

Camera, CSI 4 Data 0

− z

48 CSI4_D0_P CSI_C_D0_P − z

58 CSI4_D1_N CSI_C_D1_N

Camera, CSI 4 Data 1

− z

60 CSI4_D1_P CSI_C_D1_P

− z

40 CSI4_D2_N CSI_D_D0_N

Camera, CSI 4 Data 2

− z

42 CSI4_D2_P CSI_D_D0_P − z

64 CSI4_D3_N CSI_D_D1_N

Camera, CSI 4 Data 3

− z

66 CSI4_D3_P CSI_D_D1_P

− z

Notes:

1. In the Type/Dir column, Output is from Jetson Nano. Input is to Jetson Nano. Bidir is for Bidirectional signals.

2. The MPIO Pad Codes are described in the

Tegra X1 SoC Technical Reference Manual

“Multi-Purpose I/O Pins and Pin Multiplexing

(PinMux)” section for details.

3. The Power-on Reset State column indicates the pin state when reset is active and when it is deactivated before any changes are made by

software. “z” is tristate, pu/pd indicates internal weak pull-up/down resistor is enabled, 1/0 indicates actively driven high/low.

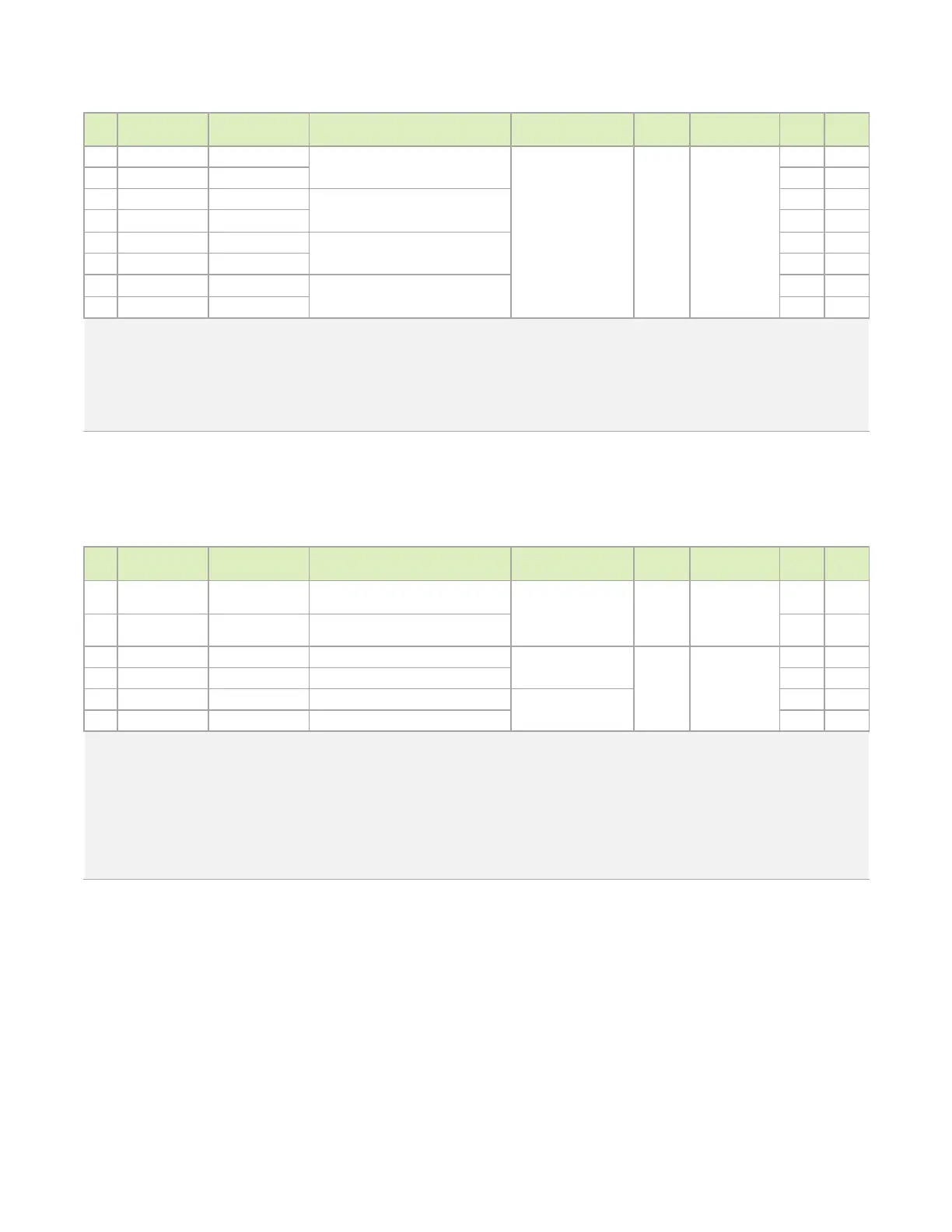

Table 8-2. Jetson Nano Camera Miscellaneous Pin Description

Pin # Module Pin Name Tegra X1 Signal Usage/Description

Usage on NVIDIA DevKit

Carrier Board

Direction Pin Type

Code

Power-on

Reset

213 CAM_I2C_SCL CAM_I2C_SCL

Camera I2C Clock. 2.2kΩ pull-up to 3.3V on the

module.

CSI Mux Bidir Open Drain – 3.3V

DD z

215 CAM_I2C_SDA CAM_I2C_SDA

Camera I2C Data. 2.2kΩ pull-up to 3.3V on the

module. DD z

114 CAM0_PWDN CAM1_PWDN Camera 0 Powerdown or GPIO

Camera Connector #1

Output CMOS – 1.8V

ST pd

116 CAM0_MCLK CAM1_MCLK Camera 0 Reference Clock ST pd

120 CAM1_PWDN CAM2_PWDN Camera 1 Powerdown or GPIO

Camera Connector #2

ST pd

122 CAM1_MCLK CAM2_MCLK Camera 1 Reference Clock ST pd

Notes:

1. In the Type/Dir column, Output is from Jetson Nano. Input is to Jetson Nano. Bidir is for Bidirectional signals.

2. The directions for CAM[1:0]_PWDN and CAM[1:0]_MCLK are true when used for these functions. Otherwise as GPIOs, the directions are

bidirectional.

3. The MPIO Pad Codes are described in the

Tegra X1 SoC Technical Reference Manual

“Multi-Purpose I/O Pins and Pin Multiplexing

(PinMux)” section for details.

4. The Power-on Reset State column indicates the pin state when reset is active and when it is deactivated before any changes are made by

software. “z” is tristate, pu/pd indicates internal weak pull-up/down resistor is enabled, 1/0 indicates actively driven high/low.

Loading...

Loading...