USB and PCI Express

NVIDIA Jetson Nano DG-09502-001_v2.1 | 23

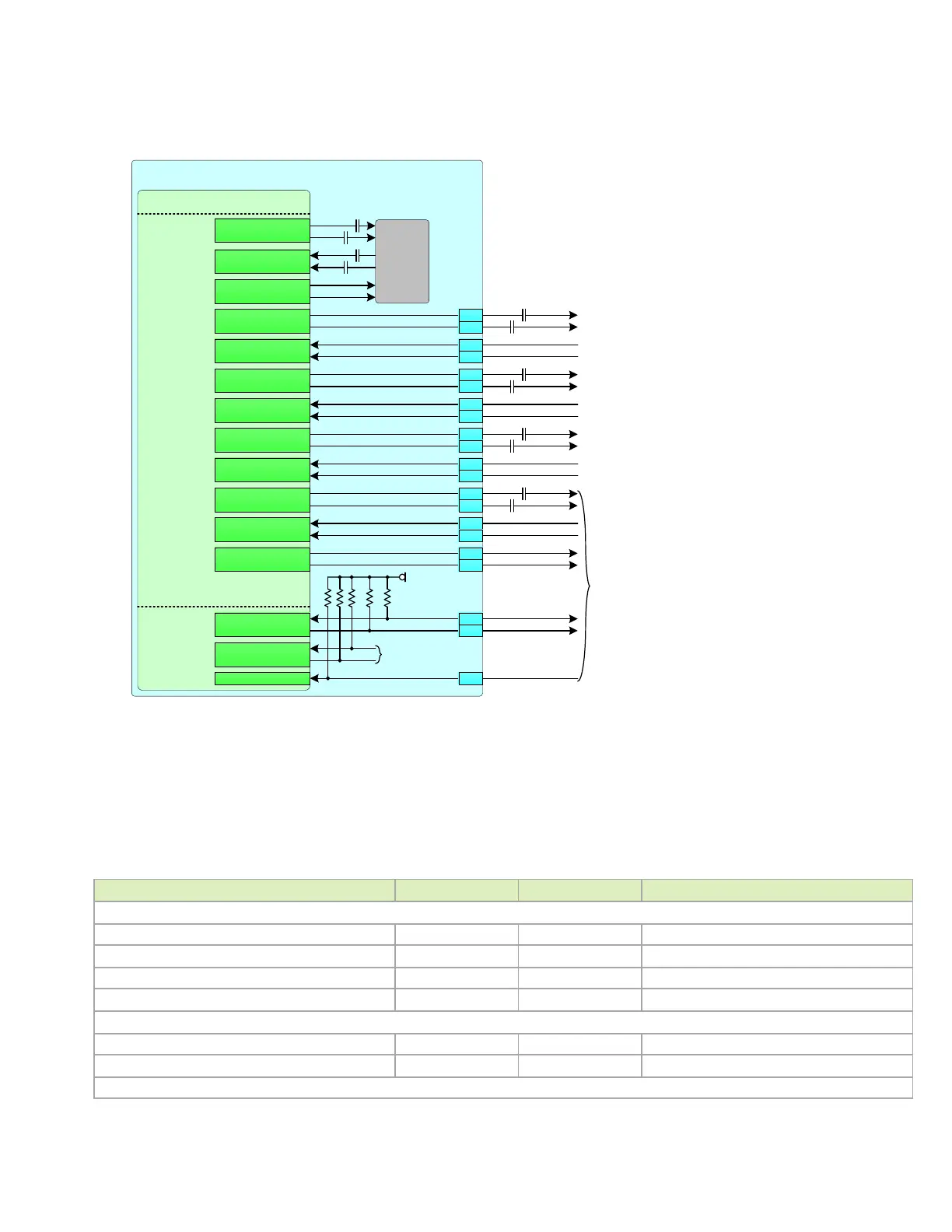

Figure 6-7. Example PCIe Connections

Jetson

Tegra - PCIe

PEX

PEX_TX0N

PEX_T

X0P

PEX_L0_CLKREQ_N

PEX_L0_RST_N

PEX_L1_CLKREQ_N

PEX_L1_RST_N

PEX_WAKE_N

PEX

Control

PEX_CLK2_ N

PEX_CLK2_ P

PEX_CLK1_ N

PEX_CLK1_ P

PEX_TX1N

PEX_TX1P

PCIe#0 Lane 3

PCIe#0 Lane 2

PCIe#0 Lane 1

PCIe#0 Lane 0

PEX

_RX0N

PEX_R

X0P

PEX_RX1N

PEX_RX1P

PEX

_TX2N

PEX_T

X2P

PEX

_RX2N

PEX_R

X2P

PEX_TX3N

PEX_TX3P

PEX_RX3N

PEX_RX3P

PEX_TX4N

PEX_TX4P

PEX_RX4N

PEX_RX4P

PCIE0_TX3_N

PCIE0_TX3_P

PCIE0_RX3_N

PCIE0_RX3_P

PCIE0_TX2_N

PCIE0_TX2_P

PCIE0_RX2_N

PCIE0_RX2_P

PCIE0_TX1_N

PCIE0_TX1_P

PCIE0_RX1_N

PCIE0_RX1_P

PCIE0_TX0_N

PCIE0_TX0_P

PCIE0_RX0_N

PCIE0_RX0_P

PCIE0_CLK_N

PCIE0_CLK_P

PCIE0_CLKREQ*

PCI E 0_ RST*

PCIE_WAKE*

VDD_3V 3_SYS

180

181

179

0. 1uF

0. 1uF

0. 1uF

0. 1uF

0. 1uF

0. 1uF

0. 1uF

0. 1uF

0. 1uF

0. 1uF

PCIe #0 – Route d to M.2 Ke y E

Connector on Carrier Board

0. 1uF

0. 1uF

Ethernet

PHY

To E thernet

PHY

100kΩ

4.7kΩ

47kΩ

156

154

155

157

148

150

149

151

140

142

137

139

134

136

131

133

160

162

6.2.1 PCIe Design Guidelines

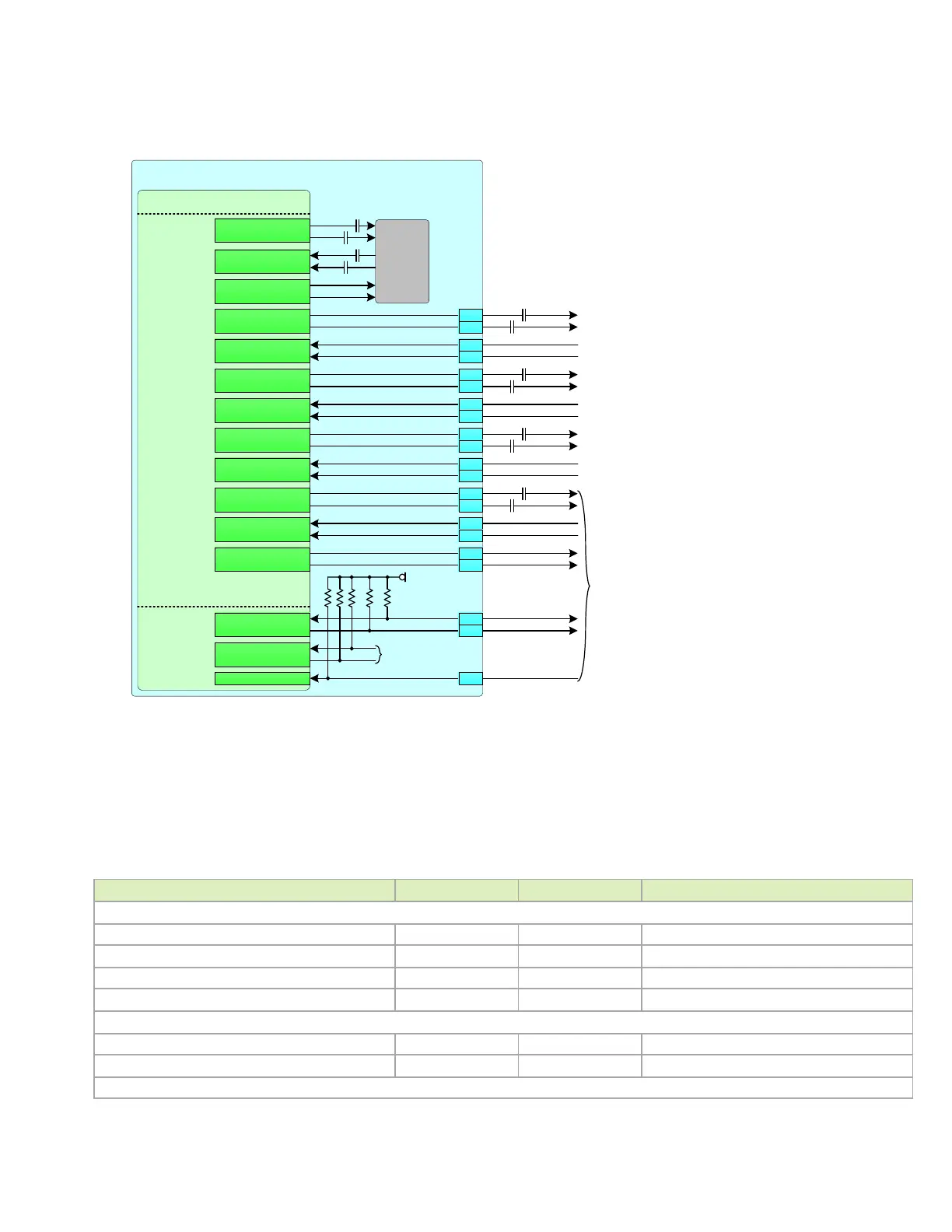

Table 6-9 and Figure 6-8 provide the signal routing requirements for the PCIe interface.

Table 6-9. PCIe Interface Signal Routing Requirements

Parameter Requirement Units Notes

Specification

Data rate / UI period 5.0 / 200 Gbps / ps 2.5GHz, half-rate architecture

Configuration / device organization 1 Load

Topology Point-point Unidirectional, differential

Termination 50 Ω To

Single Ended for P and N

Impedance

Trace Impedance diff / SE 85 / 50 Ω ±15%. See Note 1

Reference plane

Spacing

Loading...

Loading...