Display

NVIDIA Jetson Nano DG-09502-001_v2.1 | 35

The following figures show the eDP and DP interface signal routing requirements.

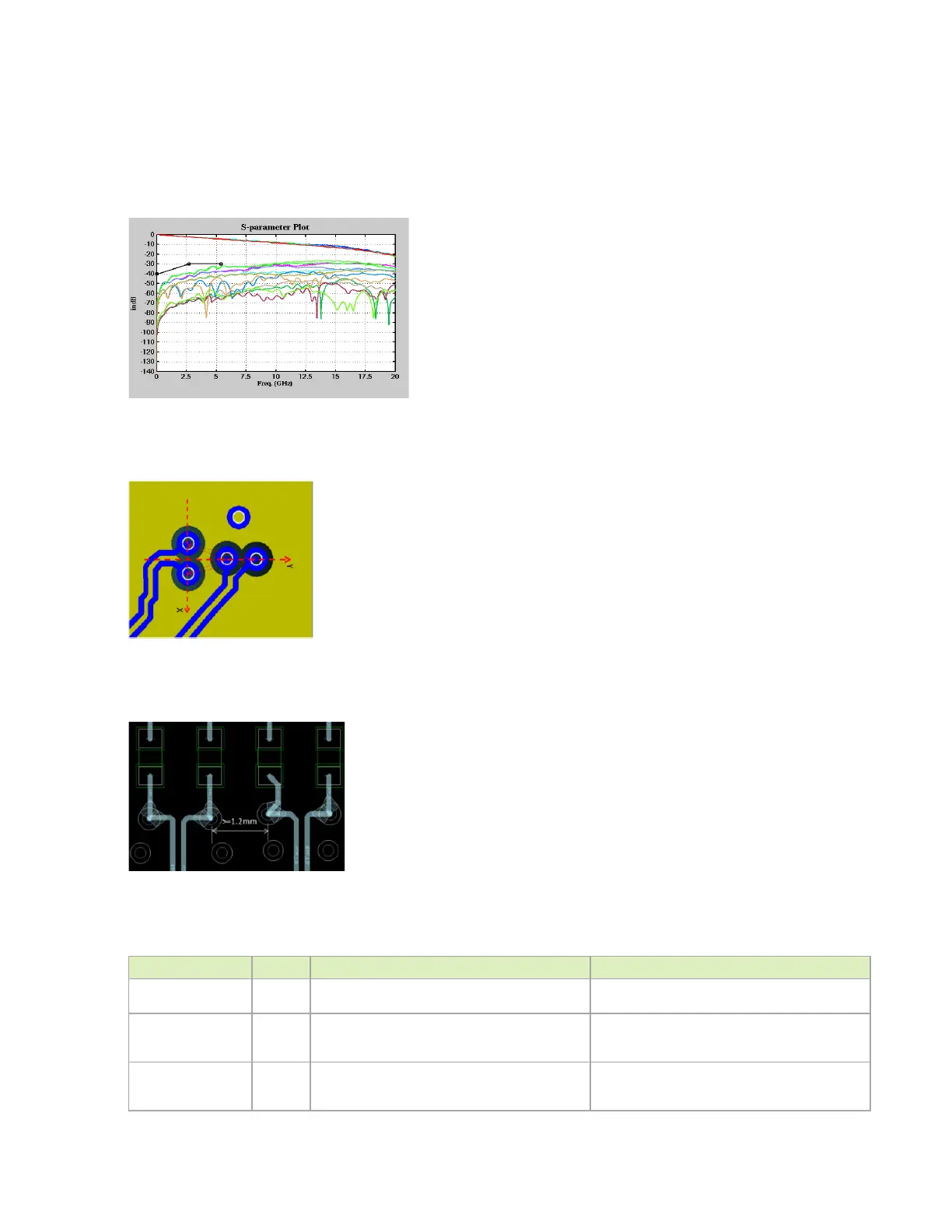

Figure 7-4. S-parameter

Figure 7-5. Via Topology #1

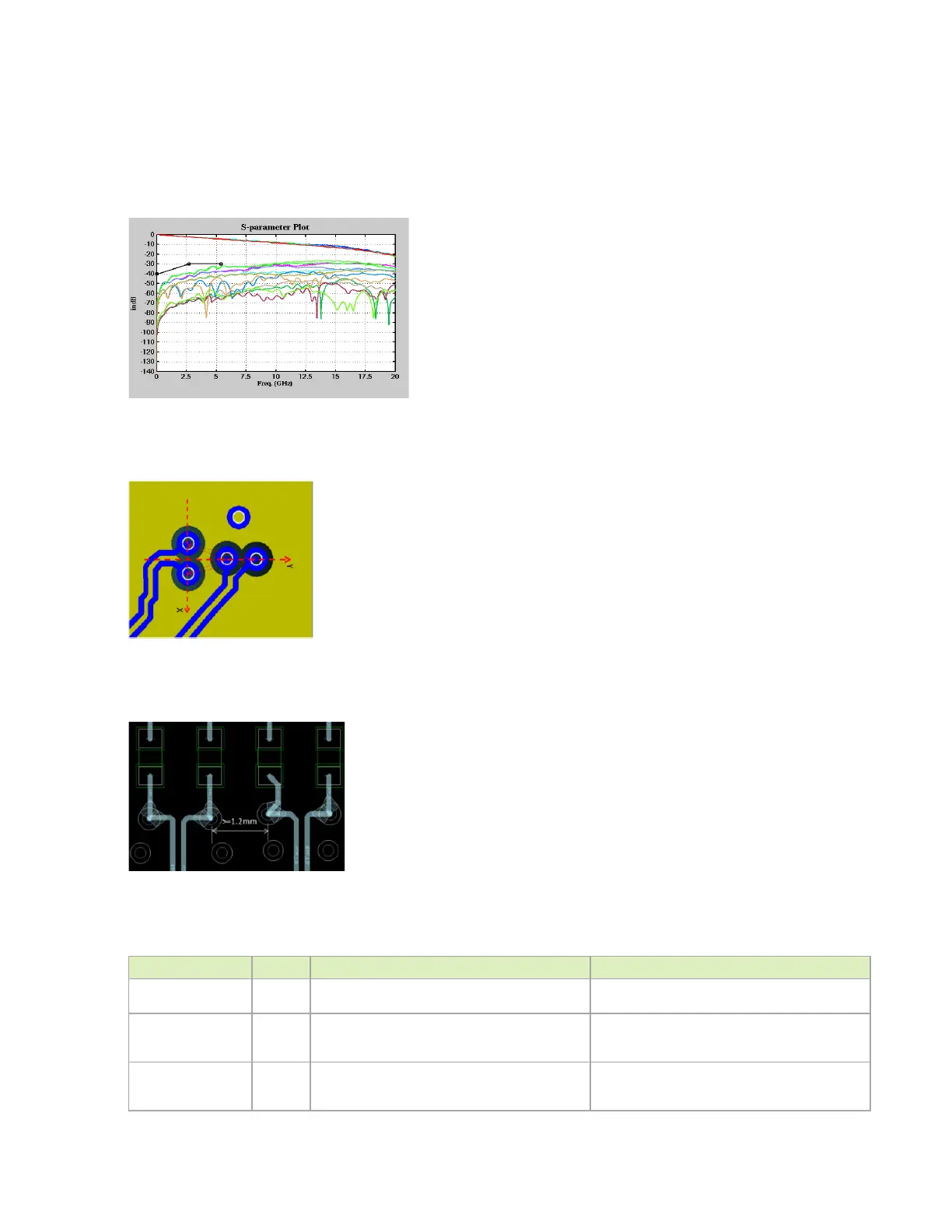

Figure 7-6. Via Topology #2

Table 7-7. eDP Signal Connections

Module Pin Name Type Termination Description

DP0_TXD[3:0]_N/P O Series 0.1uF capacitors and ESD to

on all.

eDP /DP Diffe r ential CLK/Da ta Lanes: Connect to

matching pins on display connector.

DP0_AUX_N/P I/OD

Series 0.1uF capacitors. 100kΩ pulldown on

DP0_AUX_P and 100kΩ pull-up to VDD_3 V3_SYS on

DP0_AUX_N. ESD to

on both.

eDP/DP:

: Connect to

-/+

on display connector.

DP0_HPD I

From module pin: 10kΩ pull-up to 1 .8V, l e vel shif ter

and 100kΩ pulldown on connector side of shifter and

ESD to

.

eDP/DP: Hot Plug Detect: Connect to

pin on

display connector through level shifter.

Loading...

Loading...