USB and PCI Express

NVIDIA Jetson Nano DG-09502-001_v2.1 | 20

Parameter Requirement Units Notes

General: See Chapter 15 for guidelines related to serpentine routing, routing over voids and noise coupling

Note:

1. Longer trace lengths may be possible if the total trace loss is equal to or better than the target. If the loss is greater, the max trace lengths will need to

be reduced.

2. Recommend trace length matching to <1ps before vias or any discontinuity to minimize common mode conversion.

3. Place GND vias as symmetrically as possible to data pair vias.

The following figures show the USB 3.0 interface signal routing requirements.

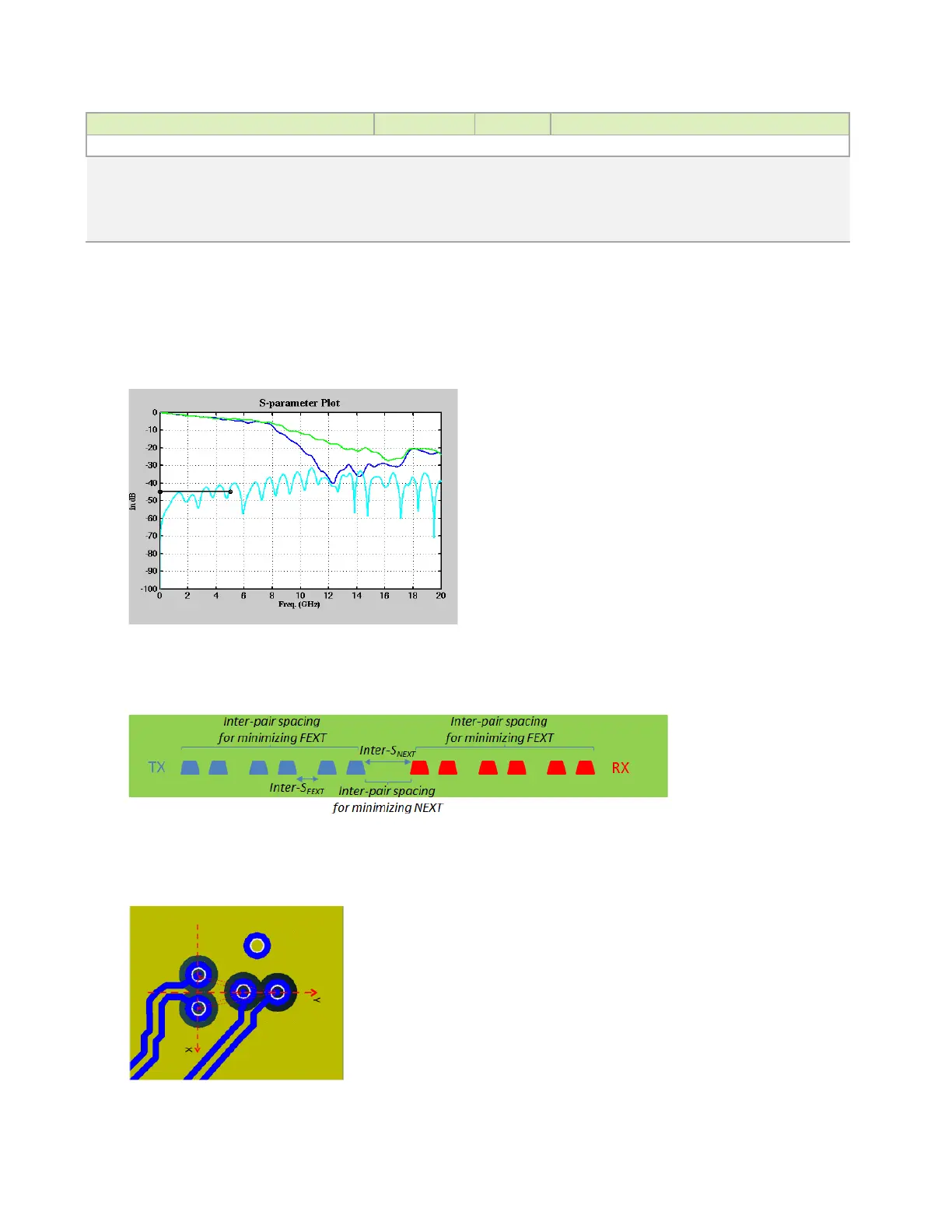

Figure 6-2. IL/NEXT Plot

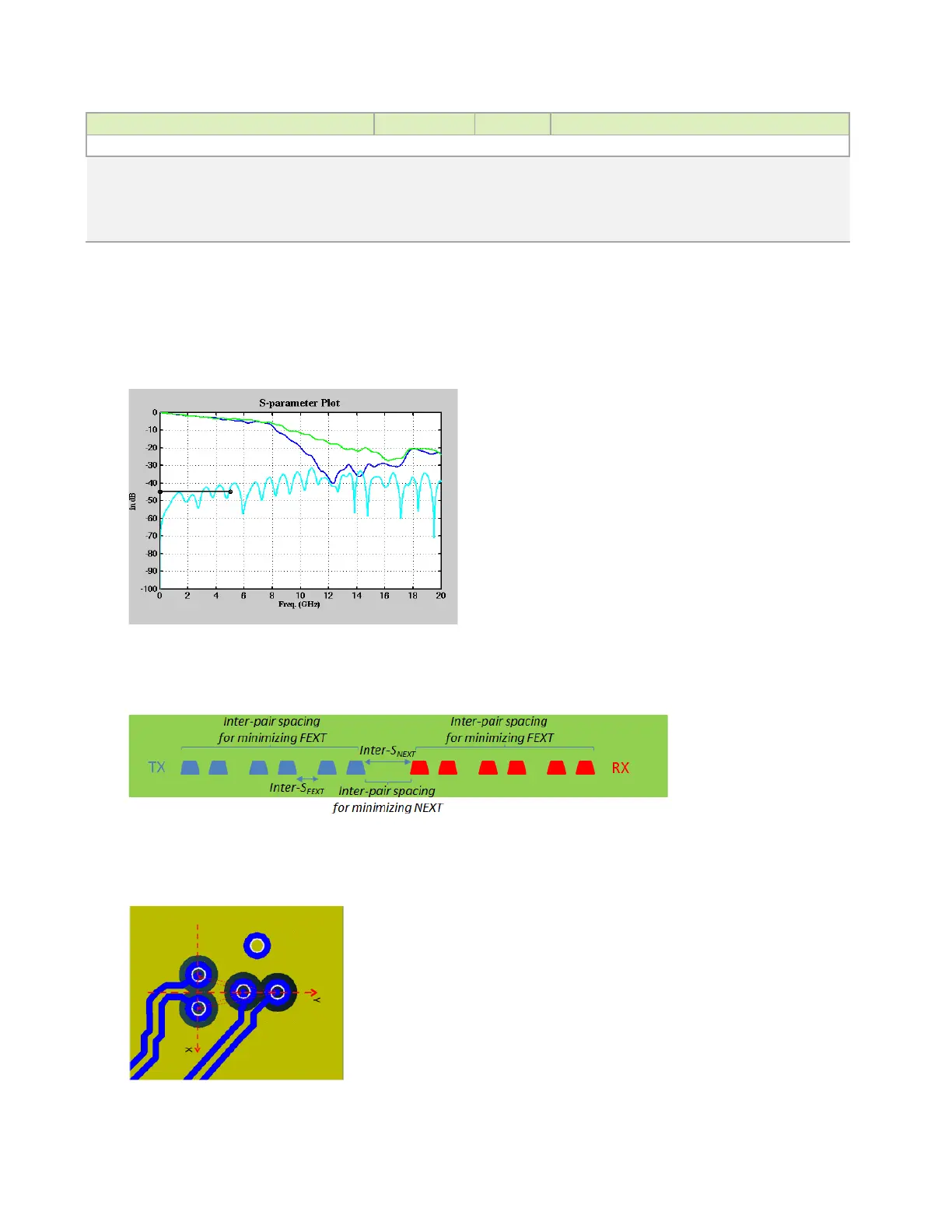

Figure 6-3. Trace Spacing for TX/RX Non-Interleaving

Figure 6-4. Via Structures

Loading...

Loading...