MIPI CSI Video Input

NVIDIA Jetson Nano DG-09502-001_v2.1 | 49

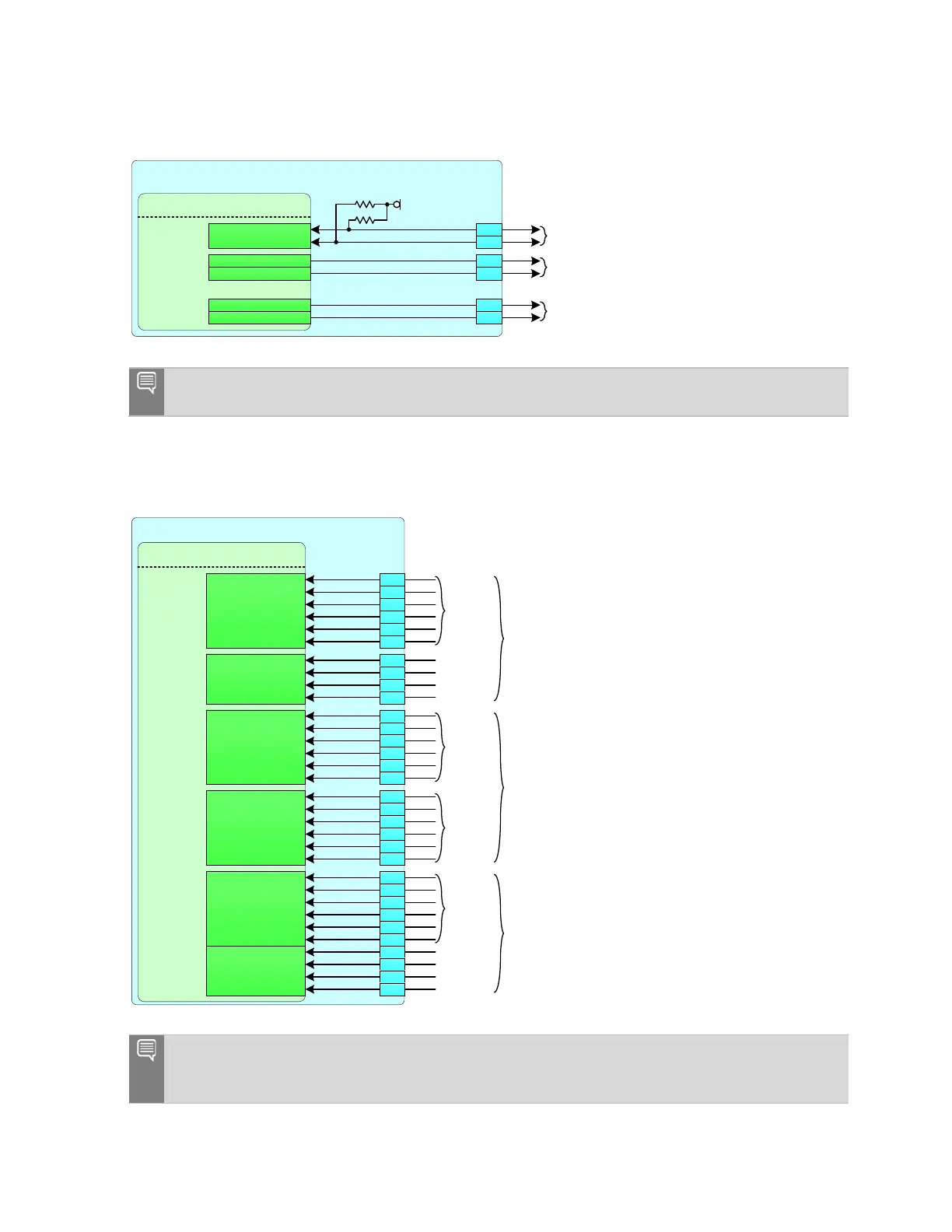

Figure 8-2. Available Cameral Control Pins

Jetson

Tegra

CAM

CAM_I2C_SCL

CAM_I2C_SDA

CAM1_MCLK

CAM2_MCLK

CAM1 _P WDN

CAM2 _P WDN

2. 2kΩ

2. 2kΩ

VDD_3V3_SY S

Camera

I2C

Camera 0

Clock/Control

Camera 1

Clock/Control

CAM_I2C_SCL

CAM_I2C_SDA

CAM0_MCLK

CAM0_PWDN

CAM1_MCLK

CAM1_PWDN

215

116

114

213

120

122

Note: The CAM_I2C interface is connected to the power monitor device on the module which

uses I2C address 7’h40.

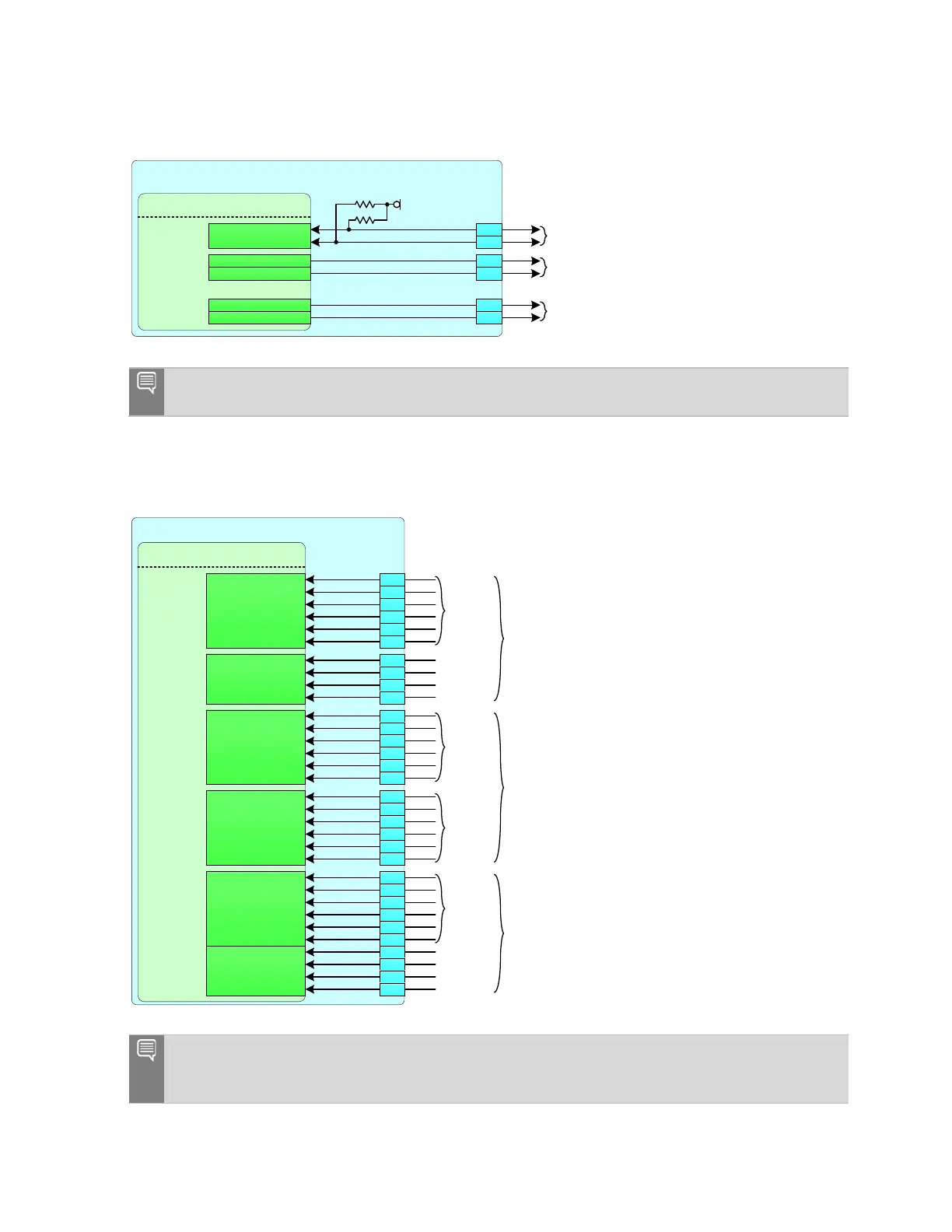

Figure 8-3. CSI Connection Options

Jetson

Tegr a

DS I/CSI

CSI_A_CLK_N

CSI_A_CLK_P

CSI_A_D0_N

CSI_A_D0_P

CSI_A_D1_N

CSI_A_D1_P

Camera 0

(2-L ane )

CSI_B_D0_N

CSI_B_D0_P

CSI_B_D1_N

CSI_B_D1_P

CSI_D_D0_N

CSI_D_D0_P

CSI_D_D1_N

CSI_D_D1_P

CSI_C_CLK_N

CSI_C_CLK_P

CSI_C_D0_N

CSI_C_D0_P

CSI_C_D1_N

CSI_C_D1_P

CSI_0_CLK_N

CSI_0_CLK_P

CSI_0_D0_N

CSI_0_D0_P

CSI_0_D1_N

CSI_0_D1_P

CSI_1_D0_N

CSI_1_D0_P

CSI_1_D1_N

CSI_1_D1_P

CSI_2_CLK_N

CSI_2_CLK_P

CSI_2_D0_N

CSI_2_D0_P

CSI_2_D1_N

CSI_2_D1_P

CSI_3_CLK_N

CSI_3_CLK_P

CSI_3_D0_N

CSI_3_D0_P

CSI_3_D1_N

CSI_3_D1_P

CSI_4_CLK_N

CSI_4_CLK_P

CSI_4_D0_N

CSI_4_D0_P

CSI_4_D1_N

CSI_4_D1_P

CSI_4_D2_N

CSI_4_D2_P

CSI_4_D3_N

CSI_4_D3_P

Camera 2

(2-L ane )

Camera 4

(2-L ane )

Camera 0/1

(4-Lane)

Only CSI 0

Clock Used

10

Camera 2/3

(4-Lane)

Only CSI 2

Clock Used

CSI_F_CLK_N

CSI_F_CLK_P

CSI_F_D0_N

CSI_F_D0_P

CSI_F_D1_N

CSI_F_D1_P

CSI_E_CLK_N

CSI_E_CLK_P

CSI_E_

D0_N

CSI_E_D0_P

CSI_E_D1_N

CSI_E_D1_P

Camera 3

(2-L ane )

Camera 4

(1, 2, or 4-Lane)

12

4

6

16

18

3

5

15

17

28

30

22

24

34

36

40

42

64

66

27

29

21

23

33

35

52

54

46

48

58

60

Note: Any EMI/ESD devices must be tuned to minimize impact to signal quality and meet the

timing and Vil/Vih requirements at the receiver and maintain signal quality and meet

requirements for the frequencies supported by the design.

Loading...

Loading...