Miscellaneous Interfaces

NVIDIA Jetson Nano DG-09502-001_v2.1 | 62

11.3 UART

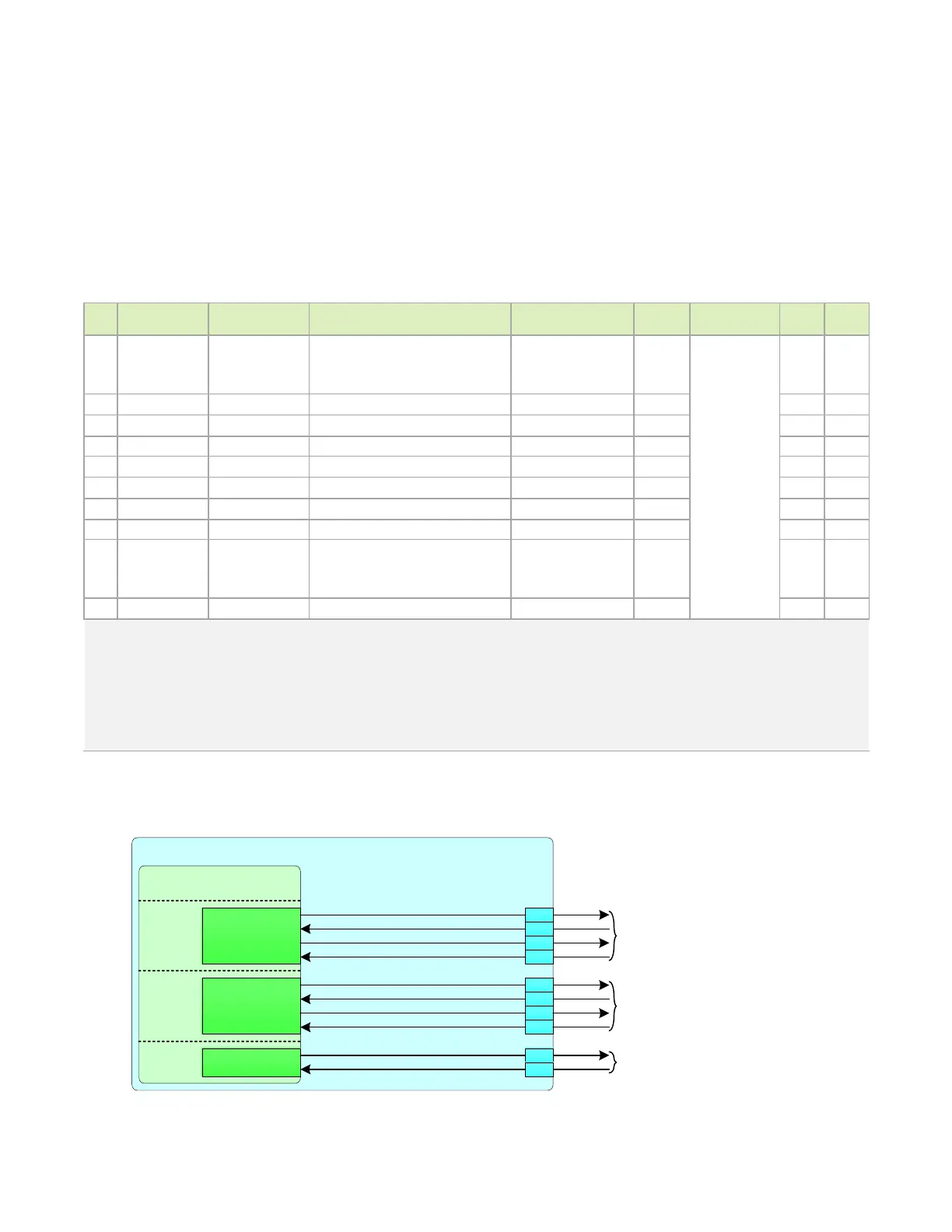

The Jetson Nano brings three UARTs out to the main connector. See Figure 11-5 for typical

assignments of the three available UARTs.

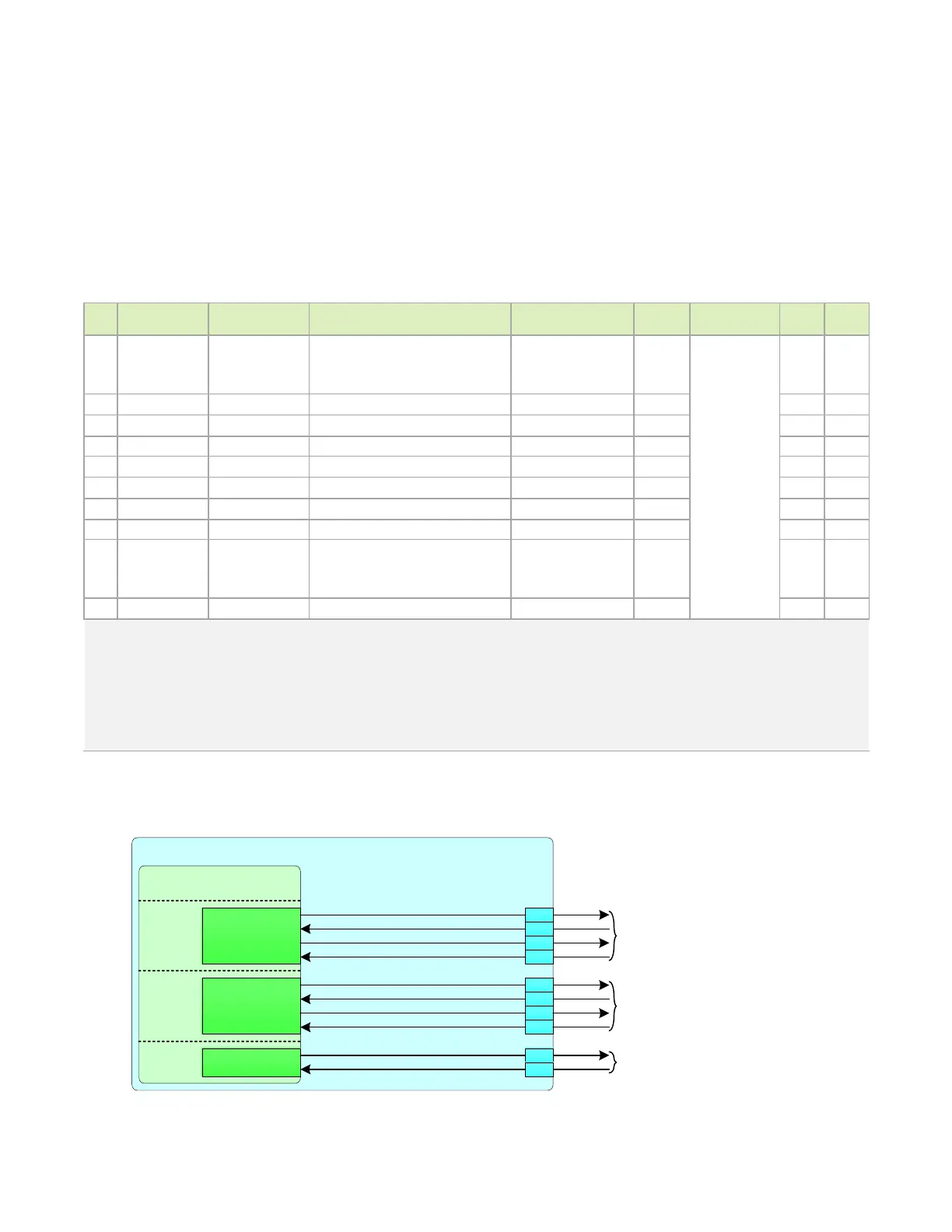

Table 11-6. Jetson Nano UART Pin Description

Pin # Module Pin Name Tegra X1 Signal Usag e/Description

Usage on NVIDIA DevKit

Carrier Board

Direction Pin Type

Code

Power-on

Reset

99 UART0_TXD UART3_TXD

UART #0 Transmit. Buffered on module to

keep connected devices from affecting state

of the pin during power-on as it is one of the

SoC strap pins.

M.2 Key E Output

CMOS – 1.8V

ST pd

101 UART0_RXD UART3_RXD UART #0 Receive M.2 Key E Input ST pd

103 UART0_RTS* UA RT3_RTS UART #0 Request to Send M.2 Key E Output ST pd

105 UART0_CTS* UART3_CTS UART #0 Clear to Send M.2 Key E Input ST pu

203 UART1_TXD UART2_TXD UART #1 Transmit Ex pansion Header Output ST pd

205 UART1_RXD UART2_RXD UART #1 Receive Expansion Header Input ST pu

207 UART1_RTS* UA RT2_RTS UART #1 Request to Send Ex pansion Header Output ST pd

209 UART1_CTS* UART2_CTS UART #1 Clear to Send Ex pansion Header Input ST pd

236 UART2_TXD UART1_TXD

UART #2 Transmit. Buffered on module to

keep connected devices from affecting state

of the pin during power-on as it is one of the

SoC strap pins.

Serial Port Output

ST pd

238 UART2_RXD UART1_RXD UART #2 Receive Serial Port Input ST pd

Notes:

1. In the Type/Dir column, Output is from Jetson Nano. Input is to Jetson Nano. Bidir is for Bidirectional signals.

2. The directions for UART[2:0]x are true when used for those functions. Otherwise as GPIOs, the direction is bidirectional.

3. The MPIO Pad Codes are described in the

Tegra X1 SoC Technical Reference Manual

“Multi-Purpose I/O Pins and Pin Multiplexing

(PinMux)” section for details.

4. The Power-on Reset State column indicates the pin state when reset is active and when it is deactivated before any changes are made

by software. “z” is tristate, pu/pd indicates internal weak pull-up/down resistor is enabled, 1/0 indicates actively driven high/low.

Figure 11-5. Jetson Nano UART Connections

Jetson

Tegra – UART

UART3_TX

UART3_RX

UART3_RTS_N

UART 3_CTS_ N

SPI

Routed to Debug

Serial Port on DevKit

UART 0_TXD

UART 0_RXD

UART 0_RTS*

UART 0_CTS*

UART 1_TXD

UART 1_RXD

UART 1_RTS*

UART 1_CTS*

UART 2_TXD

UART 2_RXD

UART1_TX

UART1_RX

DEBUG

UART2_TX

UART2_RX

UART2_RTS_N

UART 2_CTS_ N

UART

205

203

236

238

101

99

103

105

207

209

Routed to 40-pin Expansion

Header on DevKit

Routed to M.2 Key E

Connector on DevKit

Loading...

Loading...