Miscellaneous Interfaces

NVIDIA Jetson Nano DG-09502-001_v2.1 | 58

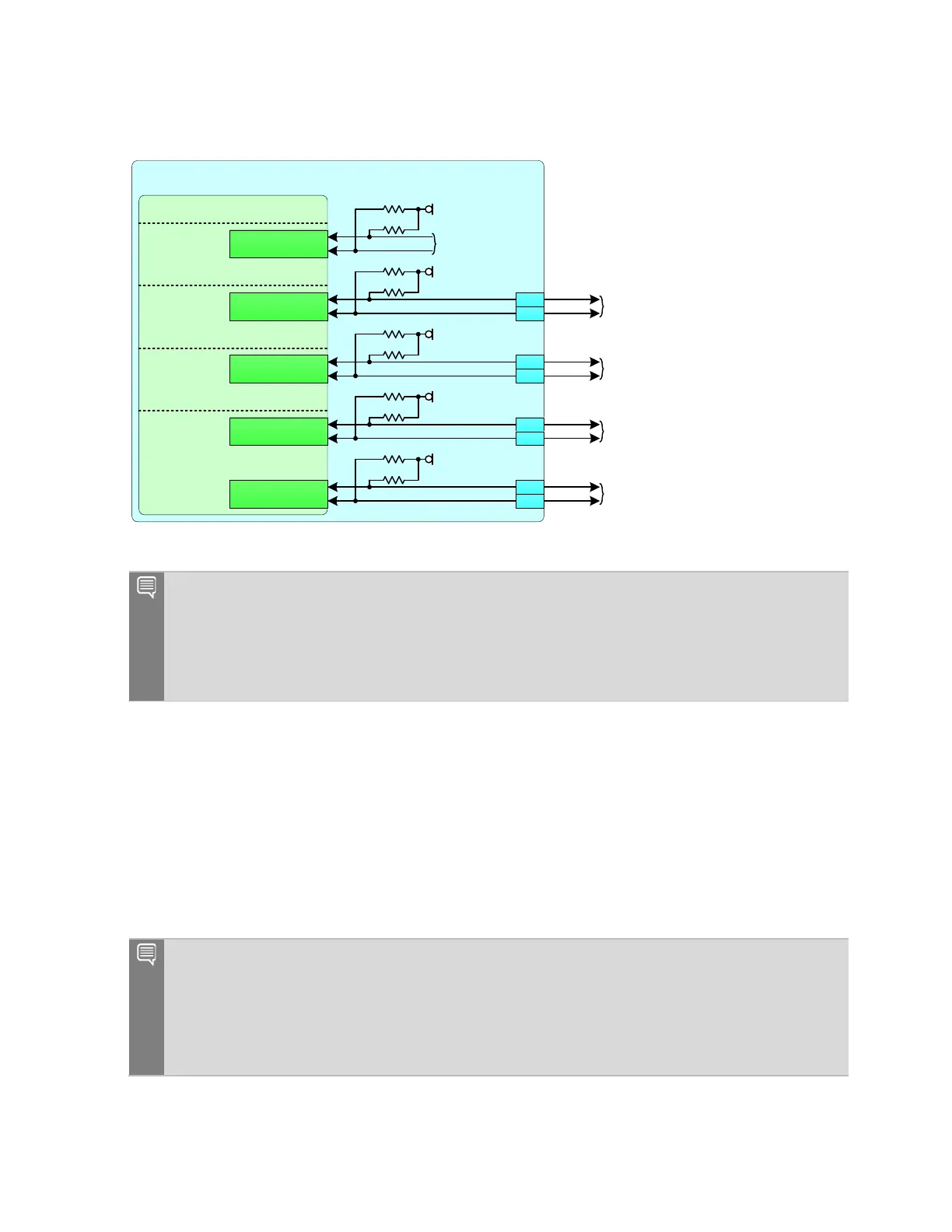

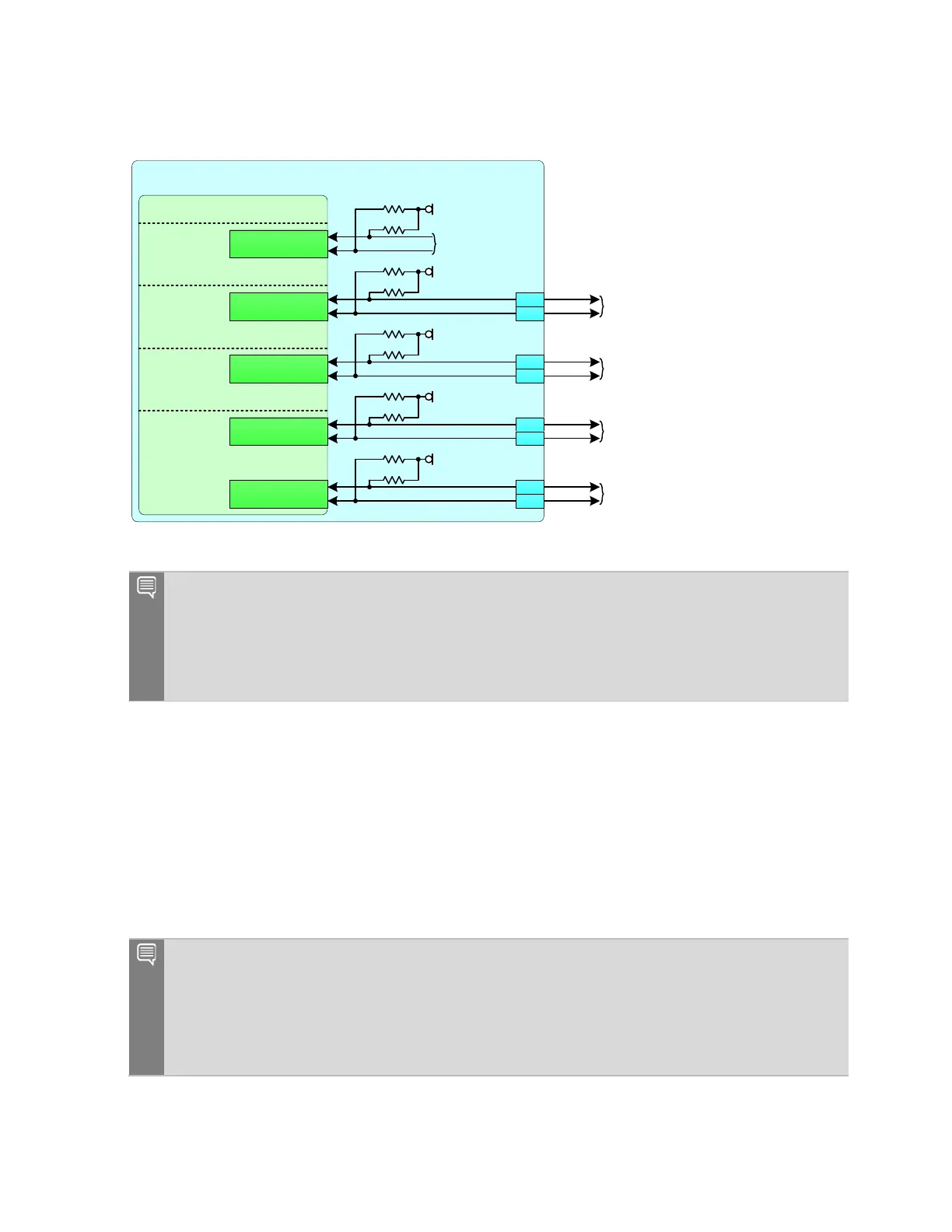

Figure 11-1. I2C Connections

Jetson

Tegra

– I2C

PWR_I2C_SCL

PWR_I2C_SDA

CAM_I2C_SCL

CAM_I2C_SDA

SYS

GEN3_I2C_SCL

GEN3_I2C_SDA

On-Module

Usage Only

VDD_1V8

CAM

DMIC

GEN1_I2C_SCL

GEN1_I2C_SDA

UART

GEN2_I2C_SCL

GEN2_I2C_SDA

VDD_3V3_SYS

2. 2kΩ

2. 2kΩ

VDD_1V8

2. 2kΩ

2. 2kΩ

VDD_3V3_SYS

2. 2kΩ

2. 2kΩ

VDD_3V3_SYS

2. 2kΩ

2. 2kΩ

Used as camera module control interface

or available for misc. 3.3V I2C devices.

CAM_I2C_SCL

CAM_I2C_SDA

I2C2_SCL

I2C2_SDA

I2C0_SCL

I2C0_SDA

I2C1_SCL

I2C1_SDA

Avai lable for misc. 1.8V I2C device s

Avai lable for misc. 3.3V I2C device s

Avai lable for misc. 3.3V I2C device s

215

213

232

234

185

187

189

191

Note: If an I2C interface is routed to an M.2 Key E or M.2 Key M socket, it is recommended that

0Ω series resistors be included on the lines. If the design will be used with WiFi modules that

require I2C then the 0Ω series resistors would be installed. However, the WiFi modules must be

fully spec compliant and not hold the I2C lines low during boot, which could interfere with

communications with other devices on this I2C bus and possibly prevent the system from

booting.

11.1.1 I2C Design Guidelines

Care must be taken to ensure I2C peripherals on same I2C bus connected to Jetson Nano do

not have duplicate addresses. Addresses can be in two forms: 7-bit, with the read/write bit

removed or 8-bit including the read/write bit. Be sure to compare I2C device addresses using

the same form (all 7-bit or all 8-bit format). The I2C2 interface is connected to an EEPROM on

the module which uses I2C address 7’h50. The CAM_I2C interface is connected to the power

monitor device on the module which uses I2C address 7’h40.

Notes:

• The Jetson Nano I2C interfaces have 2.2kΩ pull-ups on the module. Pads for additional pull-

ups are recommended in case a stronger pull-up is required due to additional loading on the

interfaces.

• The I2C pad LPMD bit is set by default for the I2C[2:0] pins, but not for the CAM_I2C pins.

These settings can be changed if necessary, to improve signal integrity.

Loading...

Loading...