RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1114

Dec 10, 2015

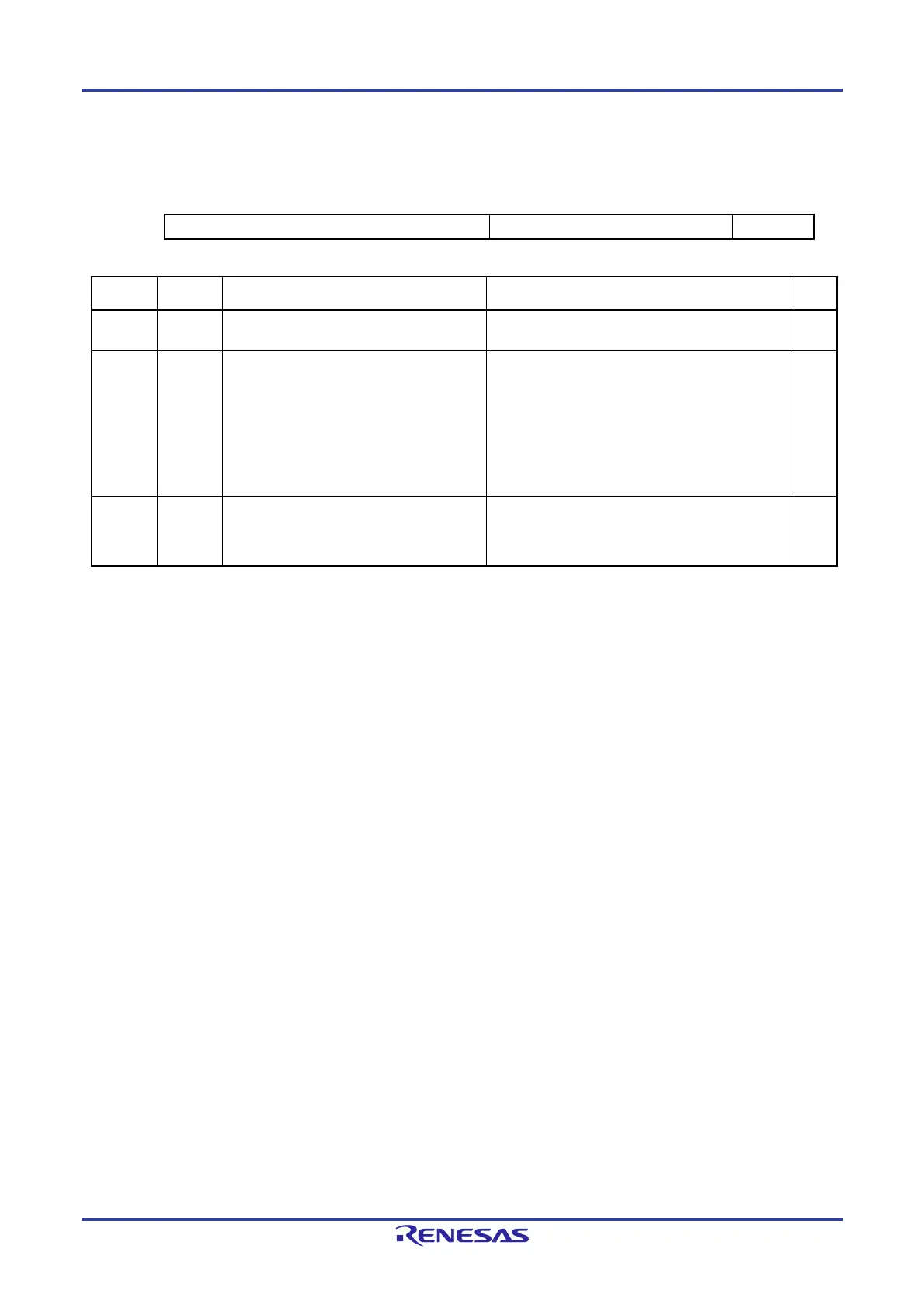

(6) LIN Wake-up Baud Rate Select Register (LWBRn)

Address: F06C1H

7 6 5 4 3 2 1 0

NSPB[3:0] LPRS[2:0] LWBR0

Value after reset:

0 0 0 0 0 0 0 0

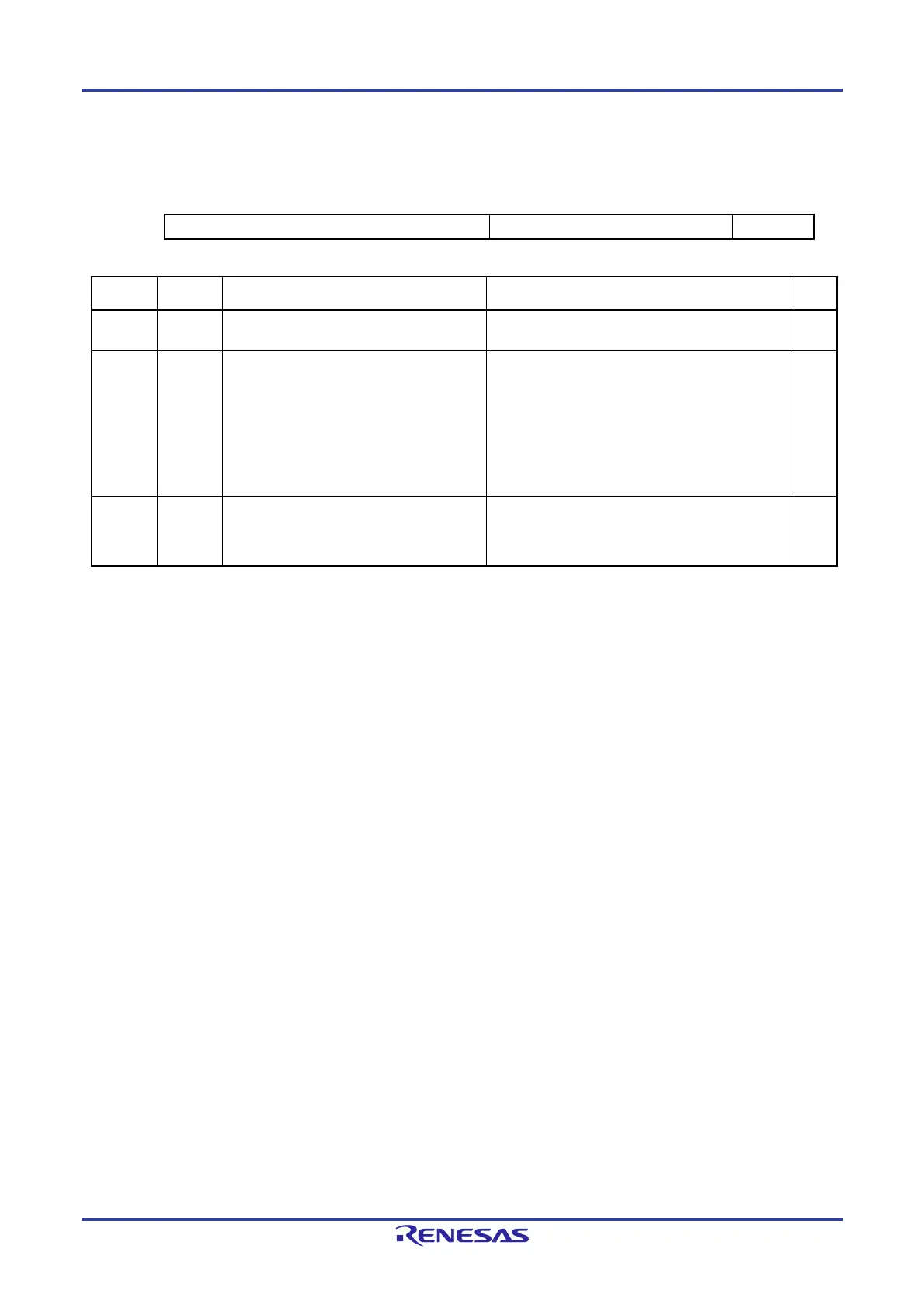

Bit Symbol Bit Name Function R/W

0 LWBR0 Wake-up Baud Rate Select 0: When LIN1.3 is used

1: When LIN 2.x is used

R/W

3 to 1 LPRS

[2:0]

Prescaler Clock Select

b3 b1

0 0 0: 1/1

0 0 1: 1/2

0 1 0: 1/4

0 1 1: 1/8

1 0 0: 1/16

1 0 1: 1/32

1 1 0: 1/64

1 1 1: 1/128

R/W

7 to 4 NSPB

[3:0]

Bit Sampling Count Select

b7 b4

0 0 0 0: 16 sampling

1 1 1 1: 16 sampling

Settings other than the above are prohibited.

R/W

Set the LWBRn register when the OMM0 bit in the LMSTn register is 0 (LIN reset mode).

LWBR0 bit (wake-up baud rate select bit)

When LIN Specification Package Revision 1.3 is used, set the LWBR0 bit in the LWBRn register to 0. This allows the 2.5-

Tbit or longer low level width of the input signal to be measured. When LIN Specification Package Revision 2.x is used, set

the LWBR0 bit to 1. When the LWBR0 bit is set to 1, fa is always selected as the LIN system clock (f

LIN) in LIN wake-up

mode regardless of the setting of LCKS bits in the LMDn register (setting of LCKS bits not affected). This allows the 2.5-Tbit

or longer low level width of the input signal to be measured.

Setting the baud rate to 19200 bps with fa selected allows 130 s or longer low level width of the input signal to be detected

in LIN wake-up mode regardless of the setting of LCKS bits in the LMDn register.

LPRS bits (prescaler clock select bits)

The LPRS bits select the frequency division ratio for the prescaler.

The LIN communication clock source frequency is divided based on this prescaler.

NSPB bits (bit sampling count select bits)

The NSPB bits select the number of sampling in one Tbit (reciprocal of the baud rate).

In LIN master mode (LIN/UART mode select bits in LIN/UART mode register = 00b), set the NSPB bits to 0000b or 1111b

(16 sampling).

Loading...

Loading...