RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1118

Dec 10, 2015

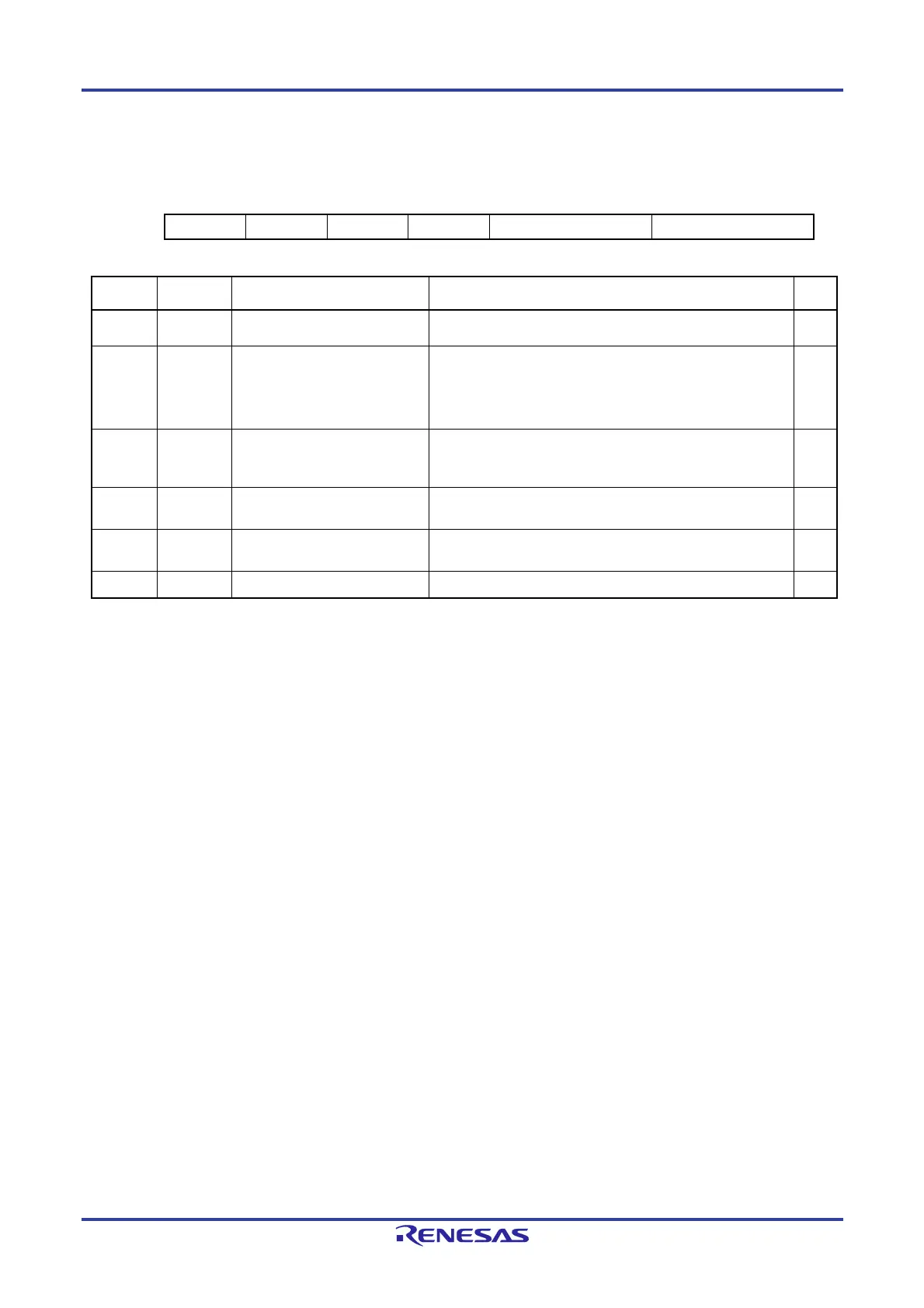

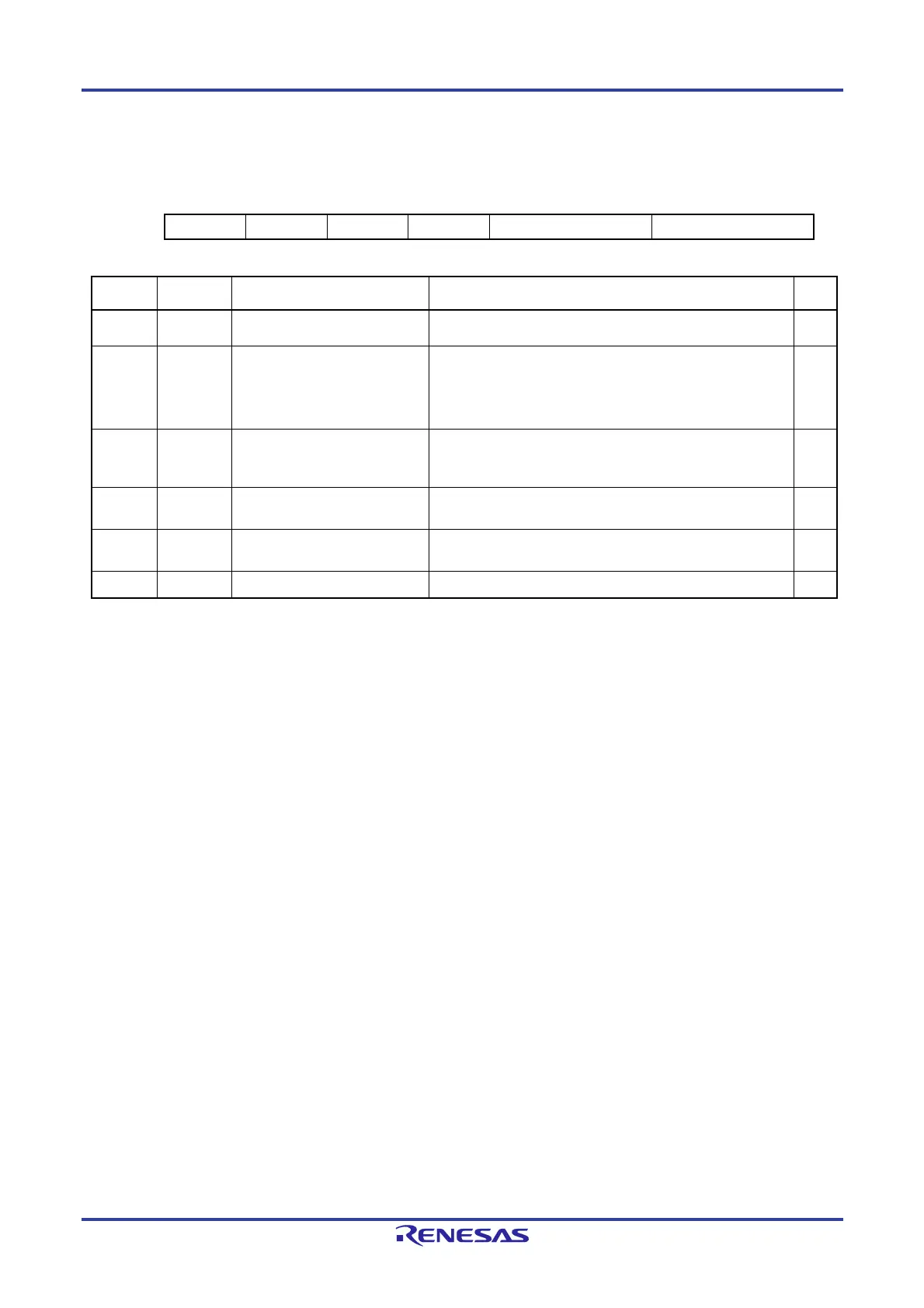

(10) LIN/UART Mode Register (LMDn)

Address: F06C8H

7 6 5 4 3 2 1 0

— — LRDNFS LIOS LCKS[1:0]

LMD[1:0]

Value after reset:

0 0 0 0 0 0 0 0

Bit Symbol Bit Name Function R/W

1, 0 LMD[1:0] LIN/UART Mode Select

b1 b0

0 0: LIN master mode

R/W

3, 2 LCKS[1:0] LIN System Clock Select

b3 b2

0 0: fa (Clock generated by baud rate prescaler 0)

0 1: fb (1/2 clock generated by baud rate prescaler 0)

1 0: fc (1/8 clock generated by baud rate prescaler 0)

1 1: fd (1/2 clock generated by baud rate prescaler 1)

R/W

4 LIOS LIN Interrupt Output Select 0: LIN interrupt is used.

1: Transmission interrupt, successful reception interrupt, and

reception status interrupt are used.

R/W

5 LRDNFS LIN Reception Data Noise

Filtering Disable

0: The noise filter is enabled.

1: The noise filter is disabled.

R/W

6 — Reserved This bit is always read as 0. The write value should always be

0.

R/W

7 — Reserved This bit is always read as 0. The write value should always be 0 R/W

Set the LMDn register when the OMM0 bit in the LMSTn register is 0 (LIN reset mode).

LMD[1:0] bits (LIN/UART mode select bits)

The LMD bits select the LIN/UART module mode.

To use the LIN/UART module as a LIN master, set these bits to 00b.

With 00b set, the LIN/UART module operates in LIN master mode.

LCKS[1:0] bits (LIN system clock select bits)

The LCKS bits select the clock to be input to the protocol controller.

With 00b set, the protocol controller is provided with fa (clock generated by baud rate prescaler 0).

With 01b set, the protocol controller is provided with fb (1/2 clock generated by baud rate prescaler 0).

With 10b set, the protocol controller is provided with fc (1/8 clock generated by baud rate prescaler 0).

With 11b set, the protocol controller is provided with fd (1/2 clock generated by baud rate prescaler 1).

When the LWBR0 bit in the LWBRn register is 1 (LIN 2.x is used) and the LMSTn register is 01h (LIN wake-up mode), fa is

always input to the protocol controller regardless of the setting of LCKS bits (setting of LCKS bits not affected).

LIOS bit (LIN interrupt output select bit)

The LIOS bit selects the number of interrupt outputs from the LIN/UART module.

With 0 set, the LIN interrupt is generated from the LIN/UART module.

With 1 set, the transmission interrupt, successful reception interrupt, and reception status interrupt are generated from the

LIN/UART module.

For each interrupt source, refer to 17.9 Interrupts.

LRDNFS bit (LIN reception data noise filtering disable bit)

The LRDNFS bit enables or disables the noise filter when receiving data.

With 0 set, the noise filter is enabled when receiving data.

With 1 set, the noise filter is disabled when receiving data.

Loading...

Loading...