Virtex-4 FPGA Configuration User Guide www.xilinx.com 105

UG071 (v1.12) June 2, 2017

Readback Command Sequences

c. Write the read STAT register packet header to the device.

d. Write two dummy words to the device to flush the packet buffer.

The MSB of all configuration packets sent through the CFG_IN register must be sent

first. The LSB is shifted while moving the TAP controller out of the SHIFT-DR state.

4. Shift the CFG_OUT instruction into the JTAG Instruction Register through the Shift-IR

state. The LSB of the CFG_OUT instruction is shifted first; the MSB is shifted while

moving the TAP controller out of the SHIFT-IR state.

5. Shift 32 bits out of the Status register through the Shift-DR state.

6. Reset the TAP controller.

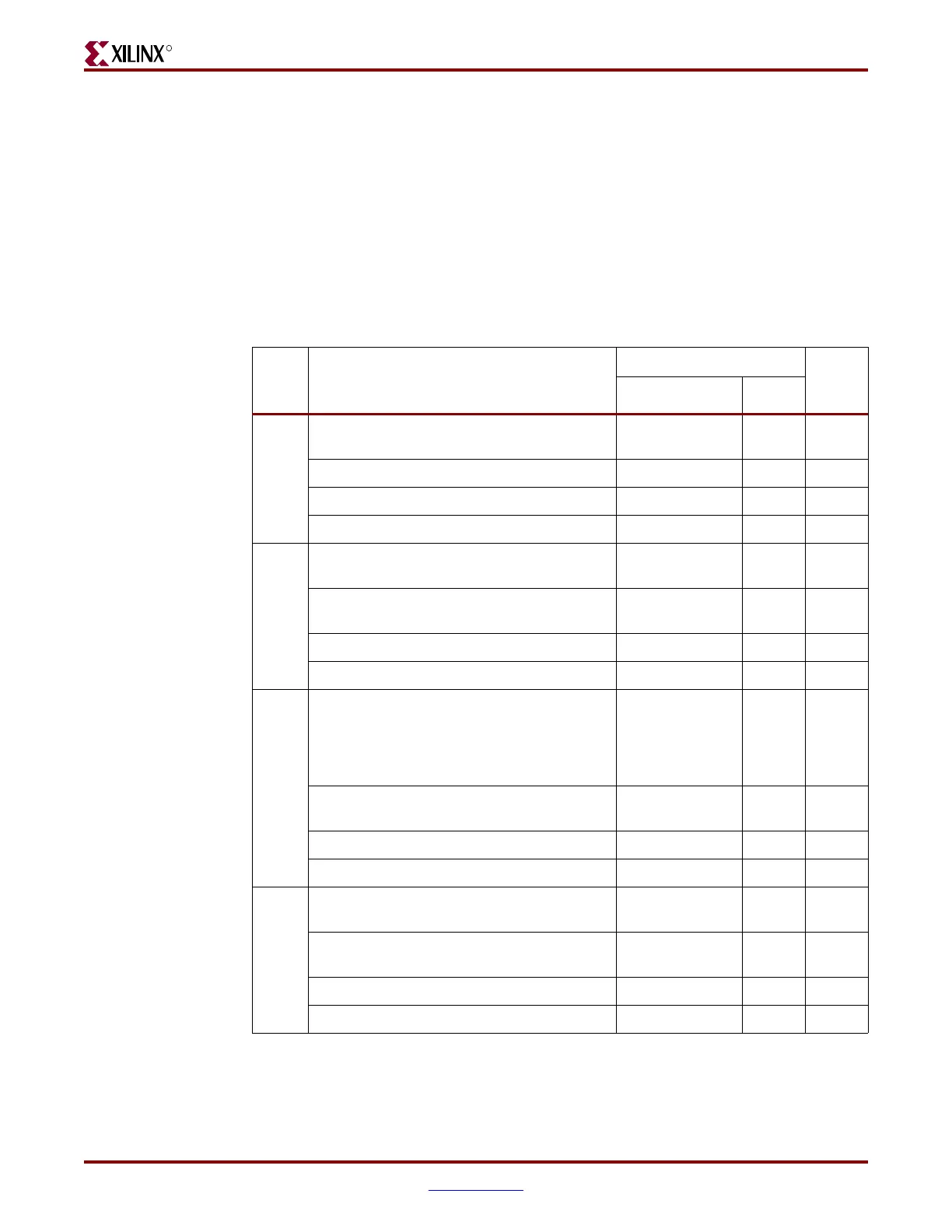

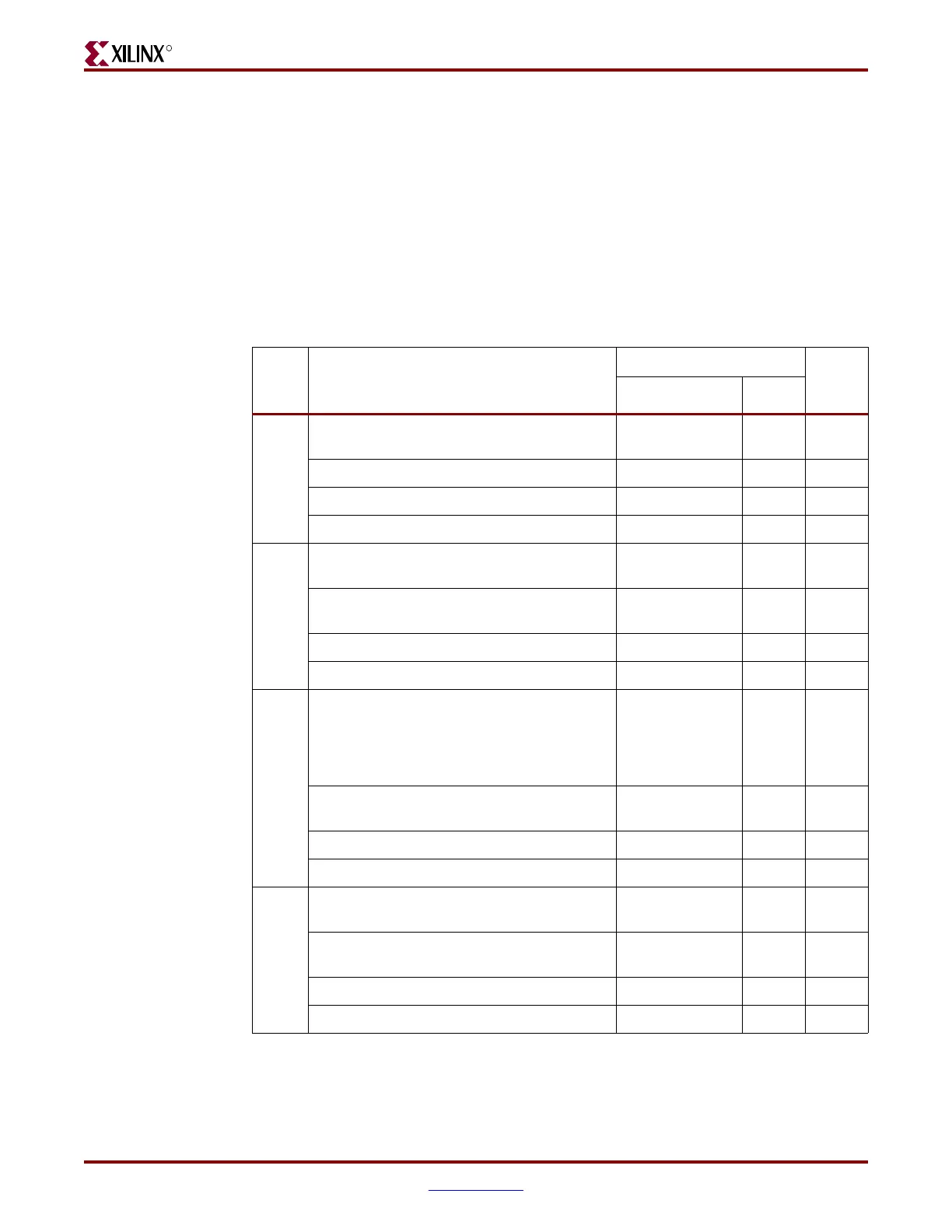

Table 8-4: Status Register Readback Command Sequence (JTAG)

Step Description

Set and Hold # of

Clocks

(TCK)

TDI TMS

1

Clock five 1s on TMS to bring the device to the

TLR state.

X15

Move into the RTI state. X 0 1

Move into the Select-IR state. X 1 2

Move into the Shift-IR state. X 0 2

2

Shift the first 9 bits of the CFG_IN instruction,

LSB first.

111100101

(CFG_IN)

09

Shift the MSB of the CFG_IN instruction while

exiting SHIFT-IR.

111

Move into the SELECT-DR state. X 1 2

Move into the SHIFT-DR state. X 0 2

3

Shift configuration packets into the CFG_IN

data register, MSB first.

a: 0xAA995566

b: 0x20000000

c: 0x2800E001

d: 0x20000000

0x20000000

0 159

Shift the LSB of the last configuration packet

while exiting SHIFT-DR.

011

Move into the SELECT-IR state. X 1 3

Move into the SHIFT-IR state. X 0 2

4

Shift the first 9 bits of the CFG_OUT instruction,

LSB first.

1110001101

(CFG_OUT)

09

Shift the MSB of the CFG_OUT instruction

while exiting Shift-IR.

111

Move into the SELECT-DR state. X 1 2

Move into the SHIFT-DR state. X 0 2

Loading...

Loading...