90 www.xilinx.com Virtex-4 FPGA Configuration User Guide

UG071 (v1.12) June 2, 2017

Chapter 7: Configuration Details

Command Register (CMD)

The Command Register is used to instruct the configuration control logic to strobe global

signals and perform other configuration functions. The command present in the CMD

register is executed each time the FAR is loaded with a new value. Table 7-6 gives the

Command Register commands and codes.

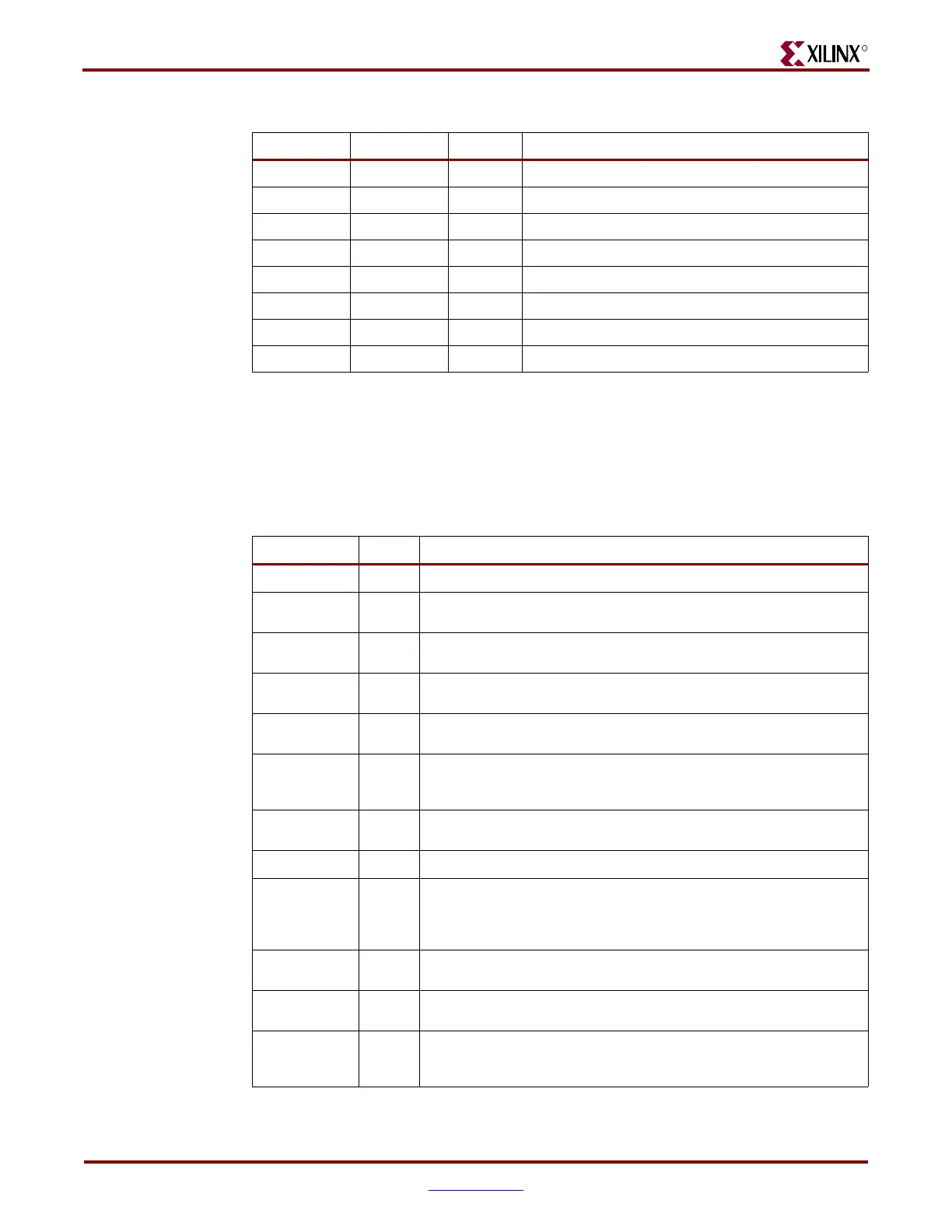

MASK

Read/Write 00110

Masking Register for CTL

STAT

Read 00111

Status Register

LOUT

Write 01000

Legacy Output Register (DOUT for daisy chain)

COR

Read/Write 01001

Configuration Option Register

MFWR

Write 01010

Multiple Frame Write

CBC

Write 01011

Initial CBC value register

IDCODE

Read/Write 01100

Device ID register

AXSS

Read/Write 01101

User bitstream access register

Table 7-5: Configuration Registers (Continued)

Reg. Name Read/Write Address Description

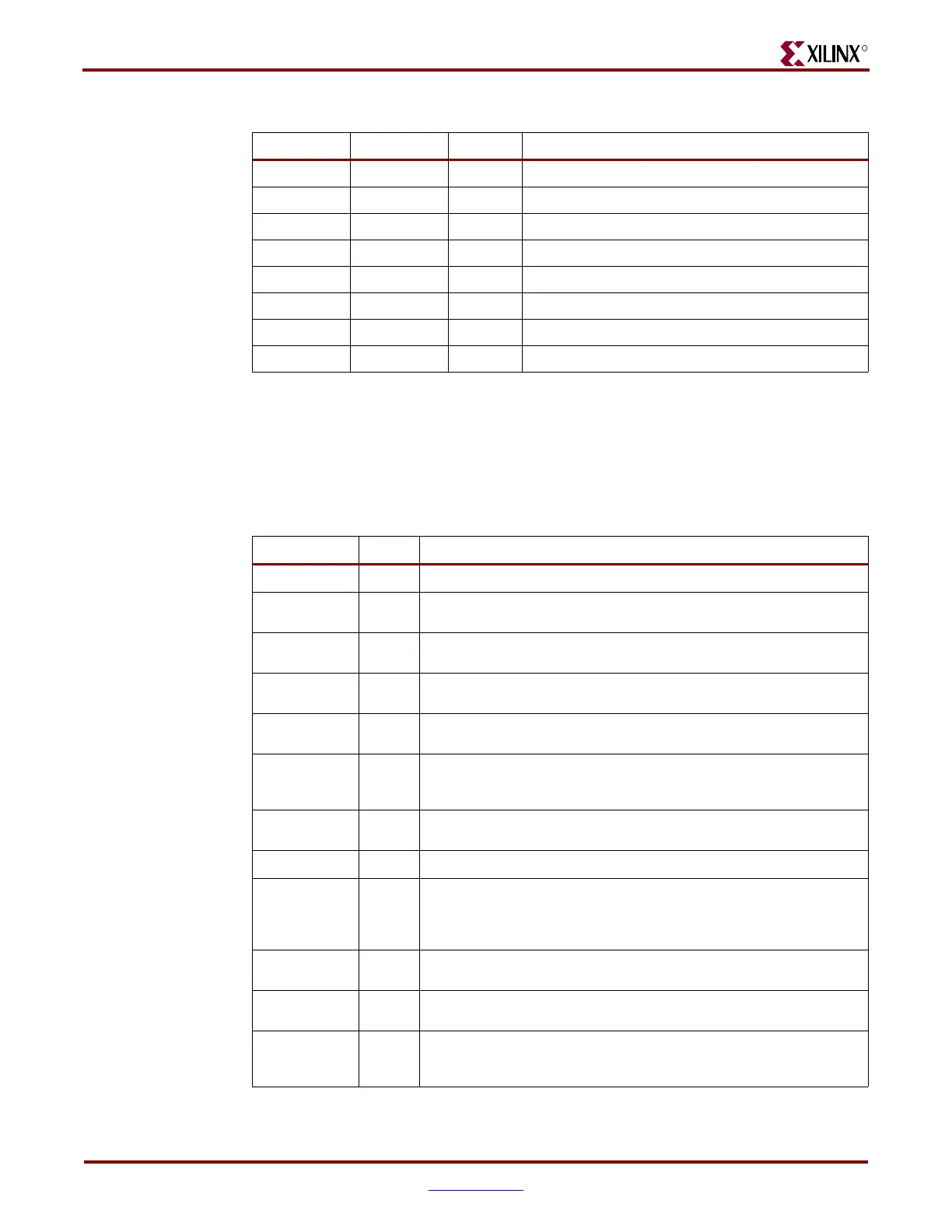

Table 7-6: Command Register Codes

Command Code Description

NULL

0000

Null Command

WCFG

0001

Write Configuration Data: used prior to writing configuration data to

the FDRI.

MFWR

0010

Multiple Frame Write: used to perform a write of a single frame data to

multiple frame addresses.

LFRM

0011

Last Frame: Deasserts the GHIGH_B signal, activating all interconnect.

The GHIGH_B signal is asserted with the AGHIGH command.

RCFG

0100

Read Configuration Data: used prior to reading configuration data

from the FDRO.

START

0101

Begin Startup Sequence: initiates the startup sequence. The startup

sequence begins after a successful CRC check and a DESYNC

command are performed.

RCAP

0110

Reset Capture: resets the CAPTURE signal after performing readback-

capture in single-shot mode (see “Readback Capture,” page 113).

RCRC

0111

Reset CRC: resets the CRC register

AGHIGH

1000

Assert GHIGH_B Signal: places all interconnect in a high-Z state to

prevent contention when writing new configuration data. This

command is only used in shutdown reconfiguration. Interconnect is

reactivated with the LFRM command.

SWITCH

1001

Switch CCLK Frequency: updates the frequency of the Master CCLK to

the value specified by the OFSEL bits in the COR.

GRESTORE

1010

Pulse the GRESTORE Signal: sets/resets (depending on user

configuration) IOB and CLB flip-flops.

SHUTDOWN

1011

Begin Shutdown Sequence: initiates the shutdown sequence, disabling

the device when finished. Shutdown activates on the next successful

CRC check or RCRC instruction (typically an RCRC instruction).

Loading...

Loading...