88 www.xilinx.com Virtex-4 FPGA Configuration User Guide

UG071 (v1.12) June 2, 2017

Chapter 7: Configuration Details

Configuration Control Logic

The Virtex-4 configuration logic consists of a packet processor, a set of registers, and global

signals that are controlled by the configuration registers. The packet processor controls the

flow of data from the configuration interface (SelectMAP, JTAG, or Serial) to the

appropriate register. The registers control all other aspects of configuration.

Packet Types

The FPGA bitstream consists of two packet types: Type 1 and Type 2. These packet types

and their usage are described below.

Type 1 Packet

The Type 1 packet is used for register reads and writes. Only 5 out of 14 register address

bits are used in Virtex-4 FPGAs. The header section is always a 32-bit word.

Following the Type 1 packet header is the Type 1 Data section, which contains the number

of 32-bit words specified by the word count portion of the header. See Table 7-2 and

Table 7-3.

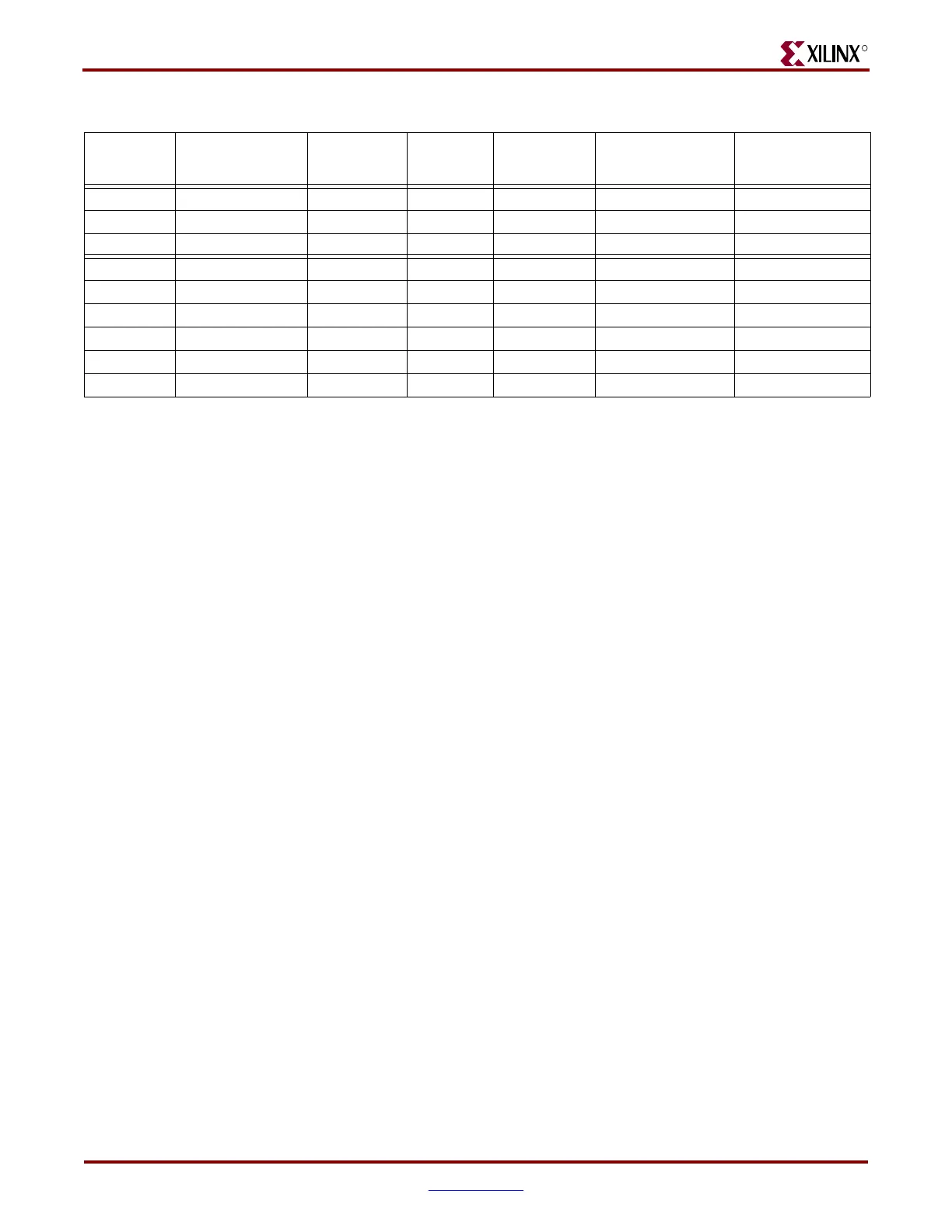

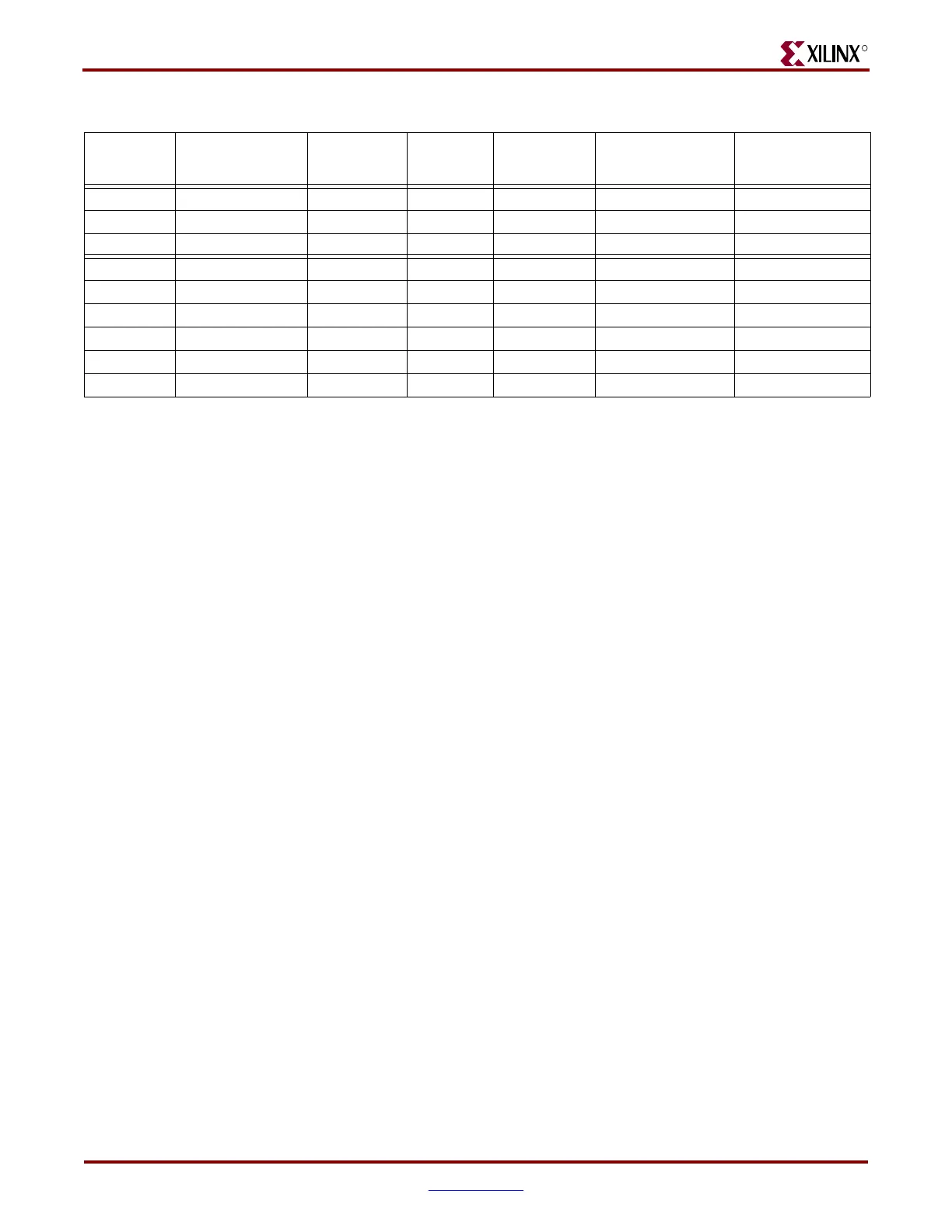

XC4VSX25 440 6,940 7,380 41 284,540 1312

XC4VSX35 660 10,410 11,070 41 426,810 1312

XC4VSX55 1,104 17,304 18,408 41 709,464 1312

XC4VFX12 248 3,600 3,848 41 147,600 1312

XC4VFX20 360 5,488 5,848 41 225,008 1312

XC4VFX40 660 10,296 10,956 41 422,136 1312

XC4VFX60 1,040 15,976 17,016 41 665,016 1312

XC4VFX100 1,660 25,170 26,830 41 1,031,970 1312

XC4VFX140 2,424 36,444 38,868 41 1,494,204 1312

Notes:

1. Non-configuration frames should be considered when calculating T

PL

(Program Latency) but do not contribute to the bitstream size.

See Table 41: Configuration Switching Characteristics in the Virtex-4 FPGA Data Sheet.

2. Configuration frames contribute to both the T

PL

calculation and the overall bitstream size.

3. The number of device frames equals the number of non-configuration plus configuration frames, and is the number of frames to use

when calculating T

PL

.

4. All Virtex-4 configuration frames consist of 41 32-bit words.

5. Configuration array size equals the number of configuration frames times the number of words per frame.

6. Configuration overhead consists of commands in the bitstream that are needed to perform configuration, but do not themselves

program any memory cells. Configuration overhead contributes to the overall bitstream size.

Table 7-1: Virtex-4 Frame Count, Frame Length, Overhead and Bitstream Size (Continued)

Device

Non-Configuration

Frames

(1)

Configuration

Frames

(2)

Device

Frames

(3)

Frame Length

(words)

(4)

Configuration

Array Size

(words)

(5)

Configuration

Overhead

(words)

(6)

Loading...

Loading...