Virtex-4 FPGA Configuration User Guide www.xilinx.com 49

UG071 (v1.12) June 2, 2017

SelectMAP Configuration Interface

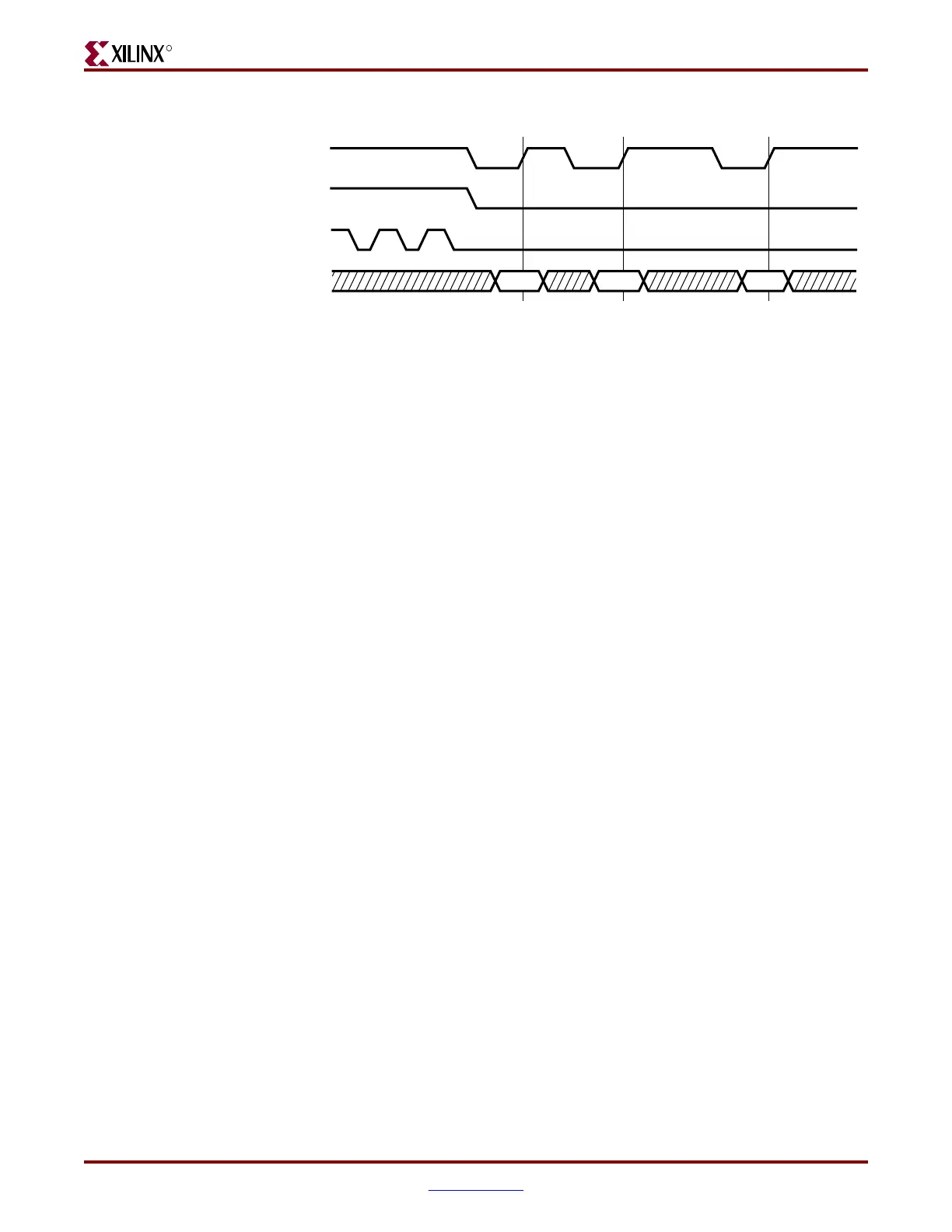

Notes relevant to Figure 2-18:

1. SelectMAP data pins are in High-Z state while CS_B is deasserted.

2. RDWR_B has no effect on the device while CS_B is deasserted.

3. CS_B is asserted by the user. Device begins loading configuration data on rising CCLK

edges.

4. Byte loaded on rising CCLK edge.

5. Byte loaded on rising CCLK edge.

6. Byte loaded on rising CCLK edge.

SelectMAP ABORT

An ABORT is an interruption in the SelectMAP configuration or readback sequence

occurring when the state of RDWR_B changes while CS_B is asserted. During a

configuration ABORT, an 8-bit status word is driven onto the SelectMAP data pins over the

next four CCLK cycles. After the ABORT sequence finishes, the user can resynchronize the

configuration logic and resume configuration. For applications that must de-assert

RDWR_B between bytes, see Controlled CCLK method, Figure 2-18.

Configuration Abort Sequence Description

An ABORT is signaled during configuration as follows:

1. The configuration sequence begins normally.

2. The user pulls the RDWR_B pin High while the device is selected (CS_B asserted Low).

3. BUSY goes High if CS_B remains asserted (Low). The FPGA drives the status word

onto the data pins if RDWR_B remains set for read control (logic High).

4. The ABORT lasts for four clock cycles and Status is updated.

Figure 2-18: Non-Continuous SelectMAP Data Loading with Controlled CCLK

CCLK

CS_B

RDWR_B

DATA[0:7]

ug071_27_080204

Byte 0 Byte 1 Byte

n

(1)

(2)

(3)

(4) (5) (6)

Loading...

Loading...