Virtex-4 FPGA Configuration User Guide www.xilinx.com 91

UG071 (v1.12) June 2, 2017

Configuration Control Logic

Control Register (CTL)

The Control Register is used to set the configuration security level, the persist setting, and

to toggle the Global Three-State signal. Writes to the CTL register are masked by the value

in the MASK register (this allows the GTS_USR_B signal to be toggled without re-

specifying the Security and Persist bits). The default value of the GLUTMASK_B bit in the

CTL register is 1, which leads to corruption of SRL16 and distributed RAM (LUTRAM)

during active readback of the device. Active readback is defined as readback that occurs

while the device is not in the shutdown state. To prevent corruption of SRL16 and

distributed RAM during active readback, the user must set the GLUTMASK_B bit to 0.

This is accomplished by writing a 1 to bit 8 of the MASK register followed by writing a 0 to

bit 8 of the CTL register. The MASK register is cleared after each write to the CTL register,

which prevents inadvertent changes to the Control Register.

The fields are illustrated in Figure 7-1 and defined in Table 7-7.

GCAPTURE

1100

Pulse GCAPTURE: loads the capture cells with the current register

states (see “Readback Capture,” page 113).

DESYNC

1101

Reset DALIGN Signal: used at the end of configuration to

desynchronize the device. After de-synchronization, all values on the

configuration data pins are ignored.

Table 7-6: Command Register Codes (Continued)

Command Code Description

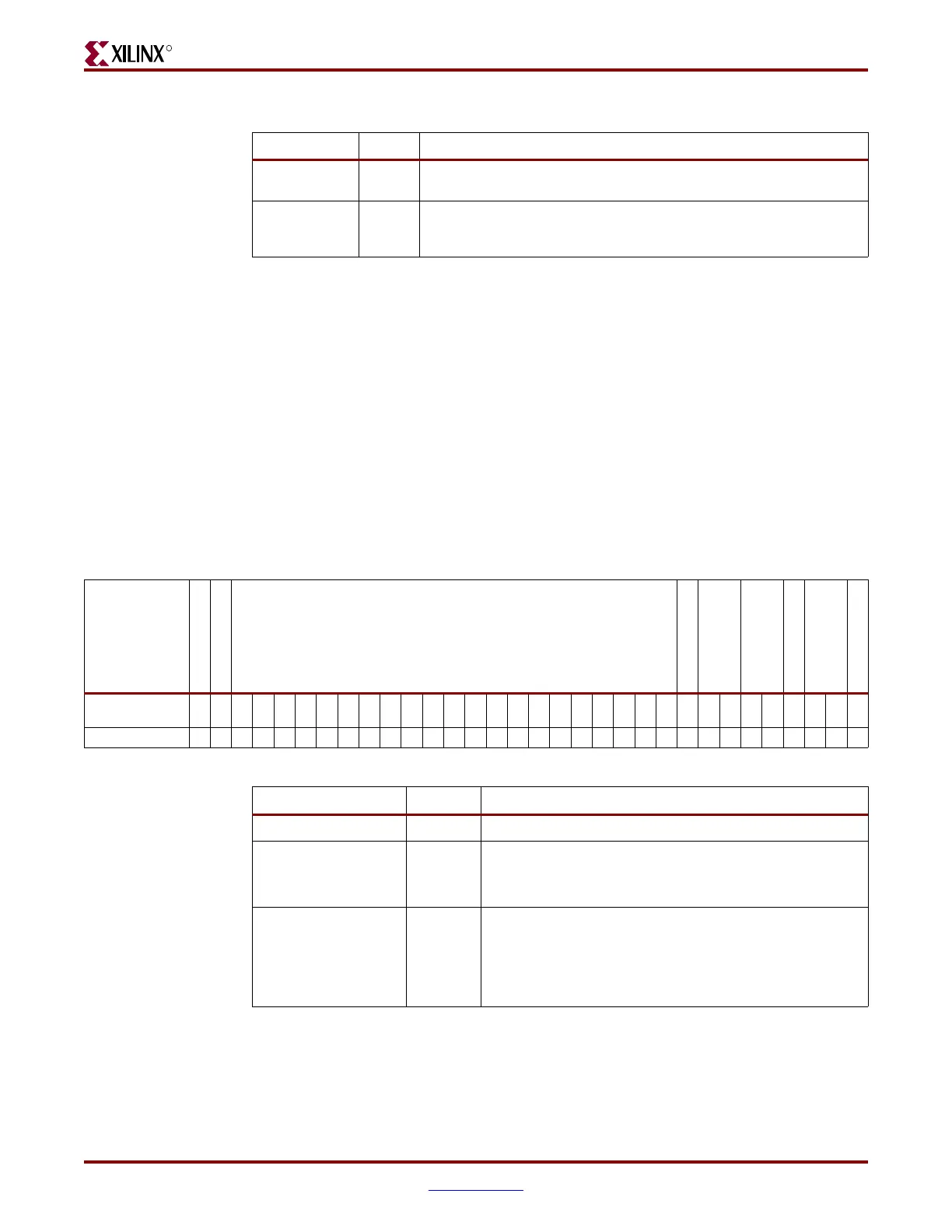

Figure 7-1: Control Register

Description

Reserved

ICAP SEL

Reserved

GLUTMASK_B

Reserved

SBITS

PERSIST

Reserved

GTS_USR_B

Bit Index

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

9 8 76543 210

Value 0000000000000000xxxxxxxxxxxxxxxx

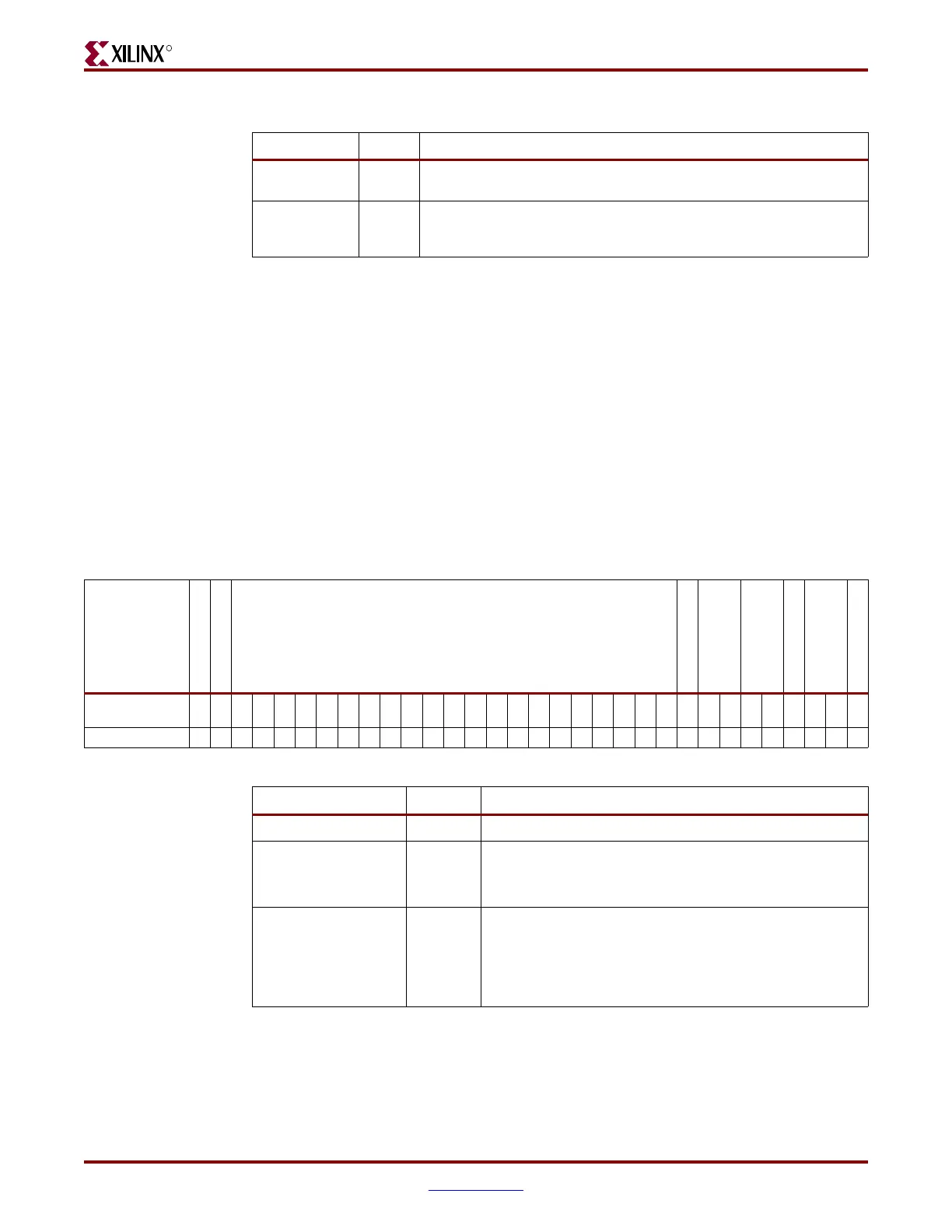

Table 7-7: Control Register Description

Name Bit Index Description

Reserved

Various Reserved CTL register bits. Always leave these bits set to 0.

ICAP_SEL

30

ICAP Port Select.

0: Top ICAP Port Enabled (default)

1: Bottom ICAP Port Enabled

SBITS

5:4

Security Level.

00: Read/Write OK (default)

01: Readback disabled

1x: Readback disabled, writing disabled except CRC

register

Loading...

Loading...