44 www.xilinx.com Virtex-4 FPGA Configuration User Guide

UG071 (v1.12) June 2, 2017

Chapter 2: Configuration Interfaces

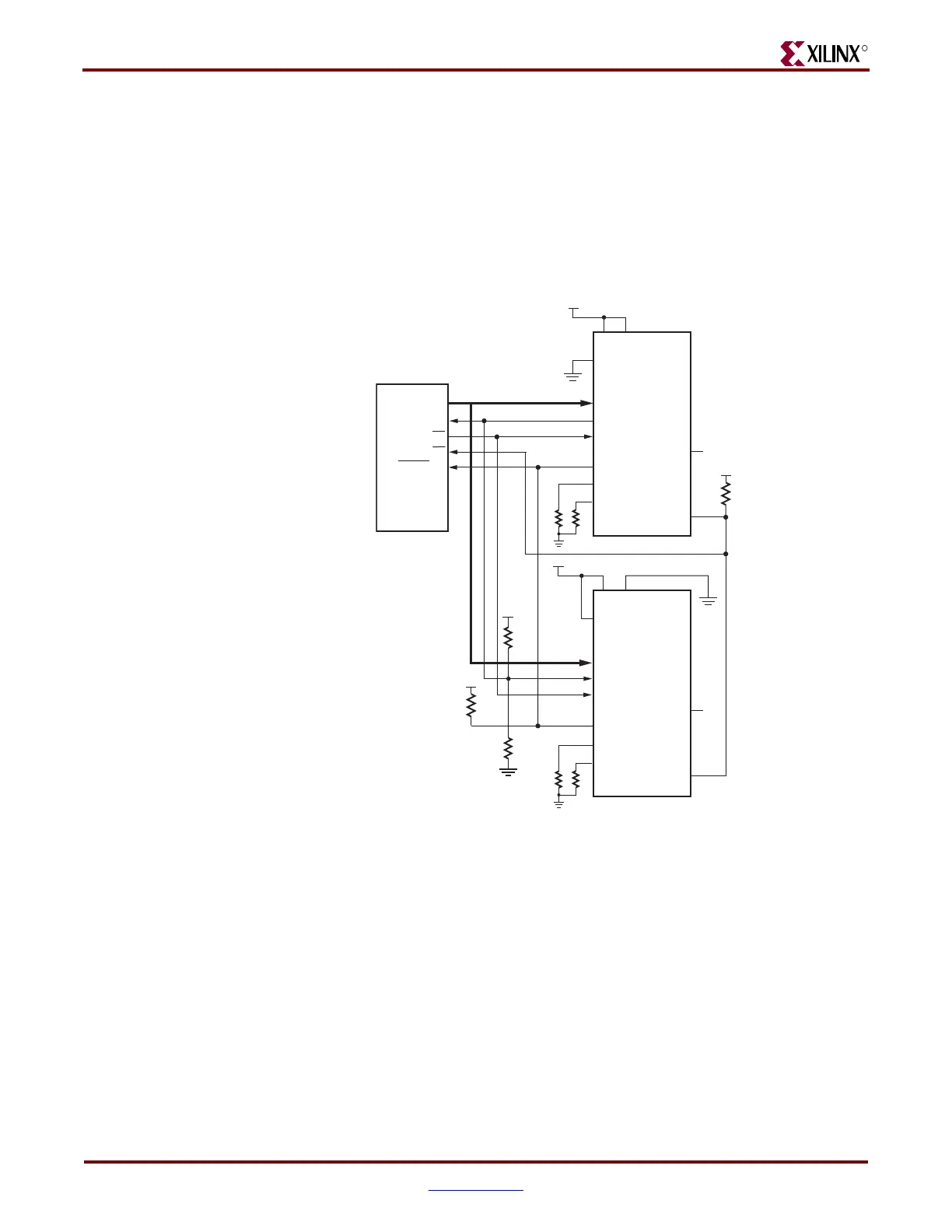

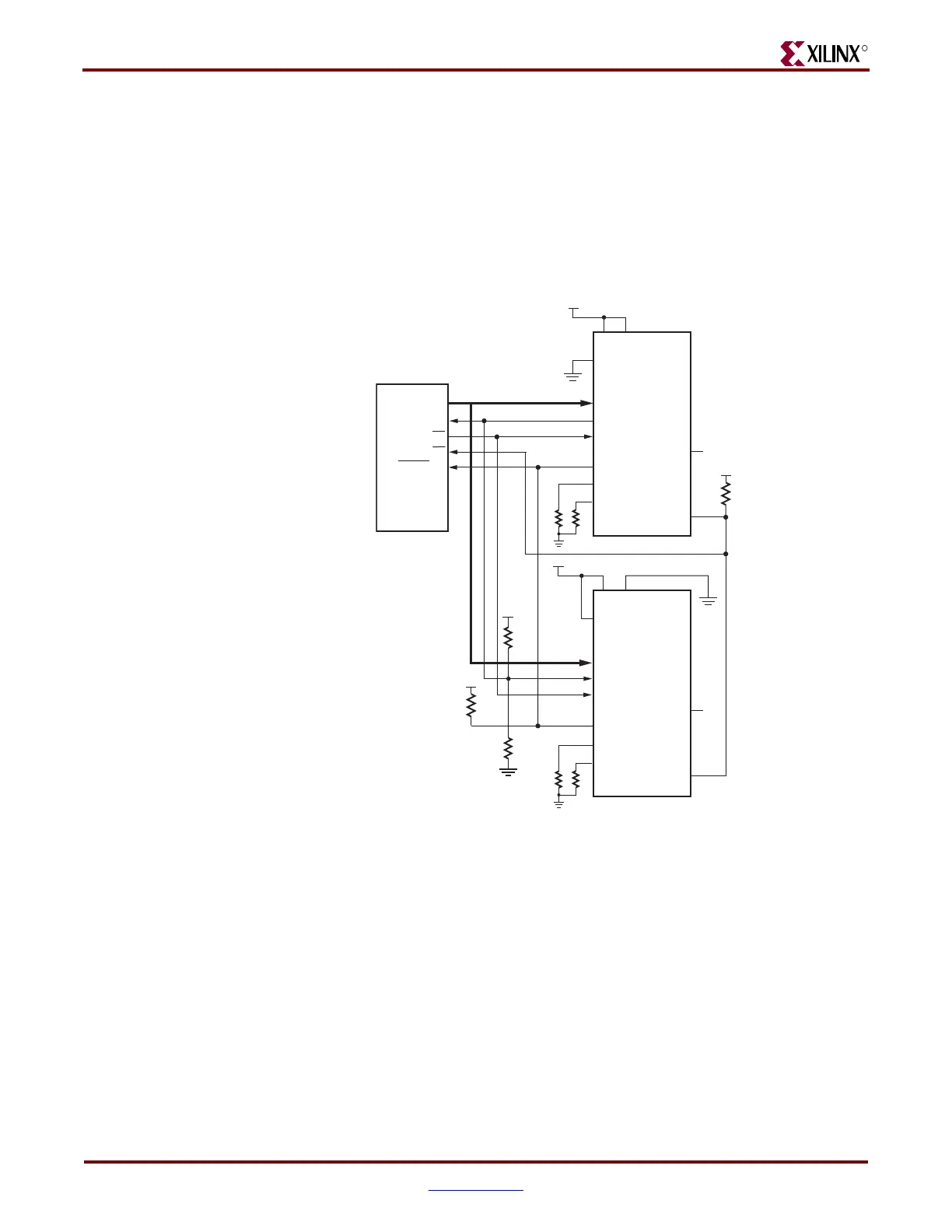

Ganged SelectMAP

It is also possible to configure simultaneously multiple devices with the same

configuration bitstream by using ganged SelectMAP configuration. In a ganged

SelectMAP arrangement, the CS_B pins of two or more devices are connected together (or

tied to ground), causing all devices to recognize data presented on the SelectMAP data

pins.

All devices can be set for Slave SelectMAP mode if an external oscillator is available, or one

device can be designated as the Master device, as illustrated in Figure 2-15.

Notes relevant to Figure 2-15:

1. The DONE pin is by default an open-drain output requiring an external pull-up

resistor. A 330Ω pull-up resistor is recommended. In this arrangement, the active

DONE driver must be disabled for both devices.

2. The INIT_B pin is a bidirectional, open-drain pin. An external pull-up resistor is

required.

3. The BitGen startup clock setting must be set for CCLK for SelectMAP configuration.

4. The BUSY signal is not used for ganged SelectMAP configuration.

5. The PROM in this diagram represents one or more Xilinx Platform Flash PROMs.

Multiple serial PROMs can be cascaded to increase the overall configurations storage

capacity.

Figure 2-15: Ganged SelectMAP Configuration

(2)

DATA[0:7]

CCLK

D[0:7]

CCLK

PROGRAM_B

D[0:7]

CCLK

PROGRAM_B

DONE

DONE

BUSY

BUSY

INIT_B

RDWR_B

CS_B

RDWR_B

CS_B

INIT_B

CE

RESET/OE

CF

ug071_24_073007

Xilinx

Serial PROM

Virtex-4

SelectMAP

Master

Virtex-4

SelectMAP

Slave

(1)

M2

M1 M0

M2

M1 M0

(10)

(10)

Loading...

Loading...