50 www.xilinx.com Virtex-4 FPGA Configuration User Guide

UG071 (v1.12) June 2, 2017

Chapter 2: Configuration Interfaces

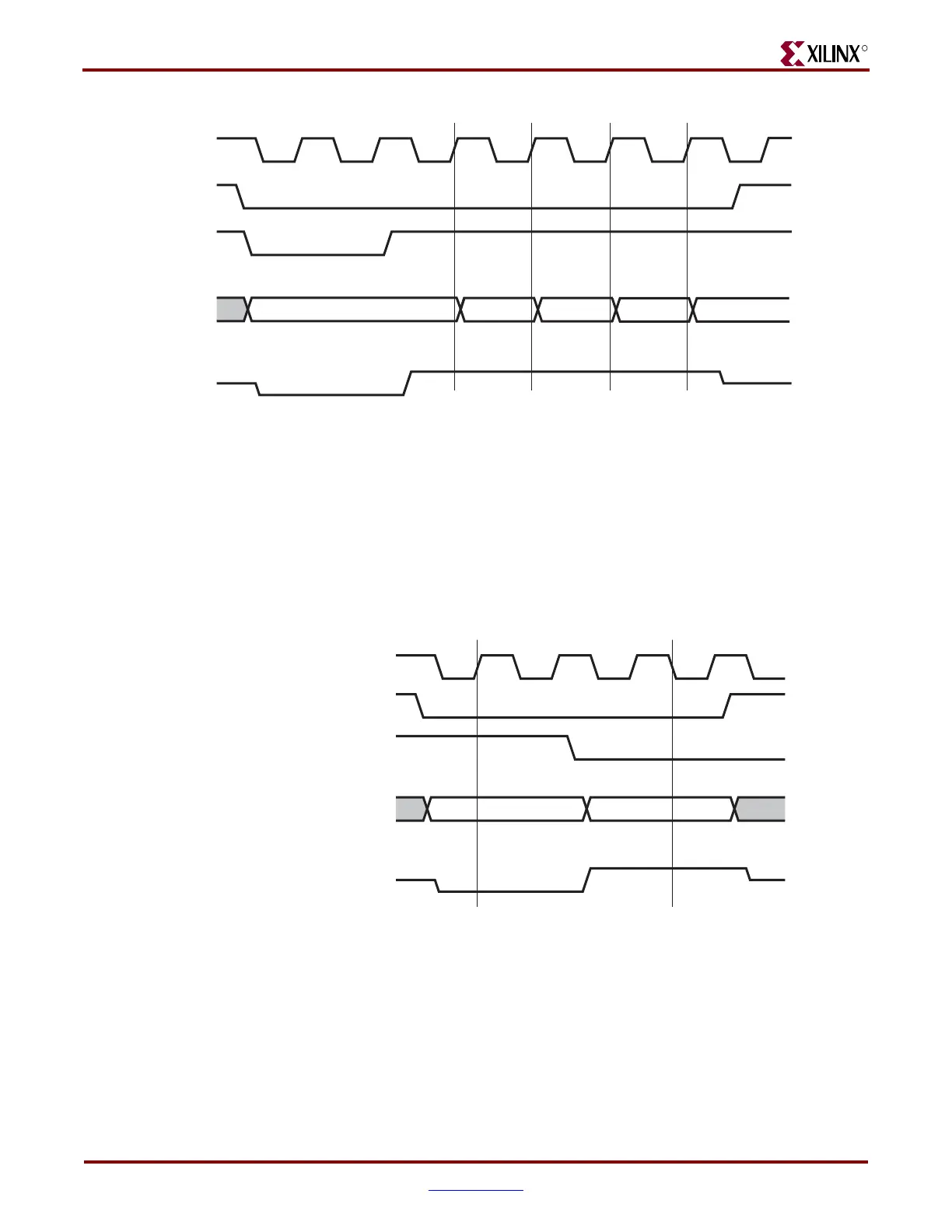

Readback Abort Sequence Description

An ABORT is signaled during readback as follows:

1. The readback sequence begins normally.

2. The user pulls the RDWR_B pin Low while the device is selected (CS_B asserted Low).

3. BUSY goes High if CS_B remains asserted (Low).

4. The ABORT ends when CS_B is deasserted.

ABORTs during readback are not followed by a status word, because the RDWR_B signal

is set for write control (FPGA SelectMAP data pins are inputs).

ABORT Status Word

During the configuration ABORT sequence, the device drives a status word onto the

SelectMAP data pins. The key for that status word is given in Table 2-5.

Figure 2-19: Configuration Abort Sequence

DATA[0:7]

BUSY

CCLK

STAT U S

ABORT

ug071_028_091207

CS_B

RDWR_B

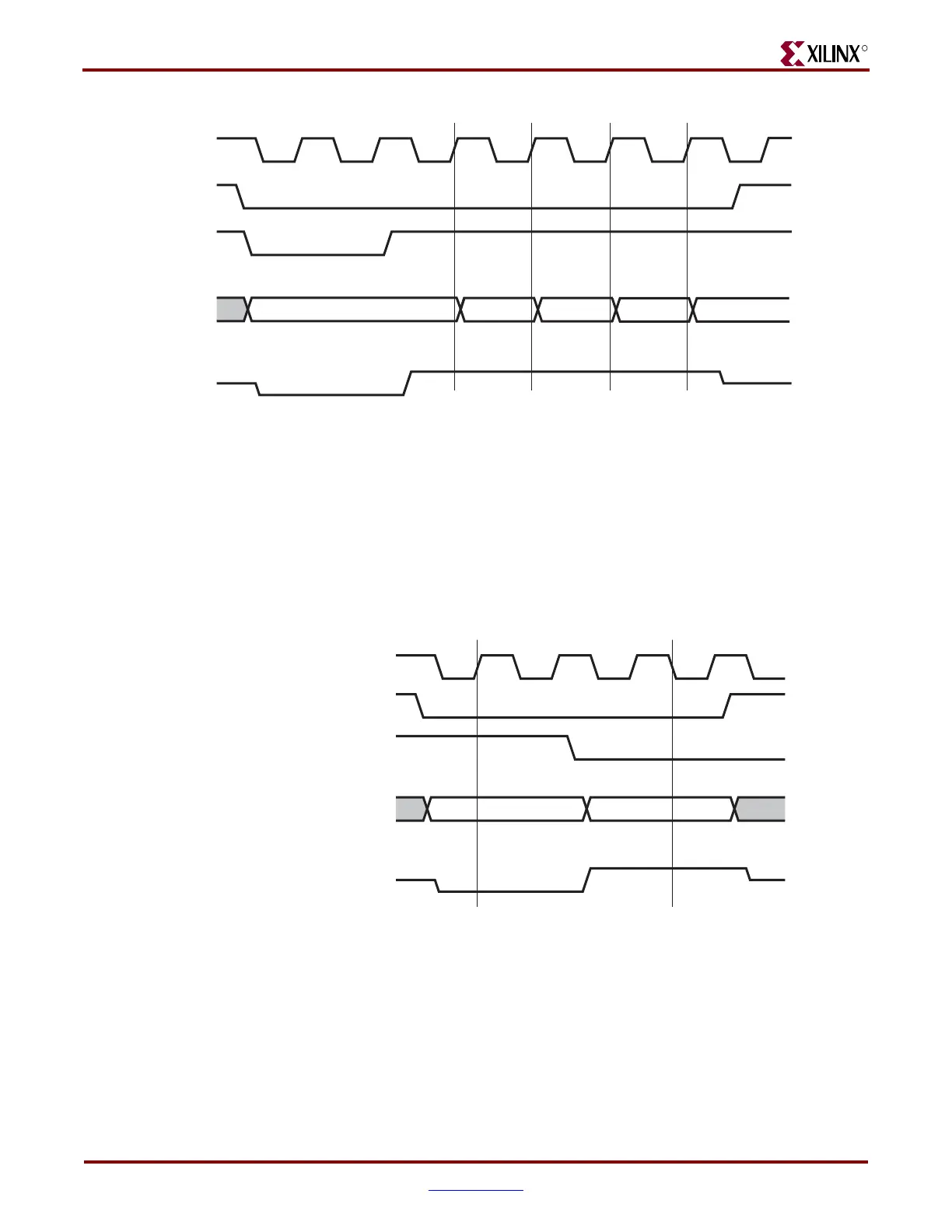

Figure 2-20: Readback Abort Sequence

DATA[0:7]

BUSY

CCLK

FPGA

ABORT

ug071_029_031104

CS_B

RDWR_B

Loading...

Loading...