92 www.xilinx.com Virtex-4 FPGA Configuration User Guide

UG071 (v1.12) June 2, 2017

Chapter 7: Configuration Details

Frame Address Register (FAR)

The Virtex-4 devices are divided into two halves, the top, and the bottom. Frames in the

bottom half mirror images in the top half with the exception of the vertical HCLK rows that

contain the global and regional clocks. The HCLK title bits are in the same order in the both

of the top and bottom frames.

All Frames in Virtex-4 have a fixed, identical length of 1312 bits (41 32-bit words). One

Frame configures one HCLK with either 4 block RAMS, 32 IOBs or 4 DSPs.

The FAR is divided into five fields: top/bottom bit, block type, row address, column

address, and minor address. The address can be written directly or can be auto-

incremented at the end of each frame. The typical bitstream starts at address 0 and auto-

increment to the final count.

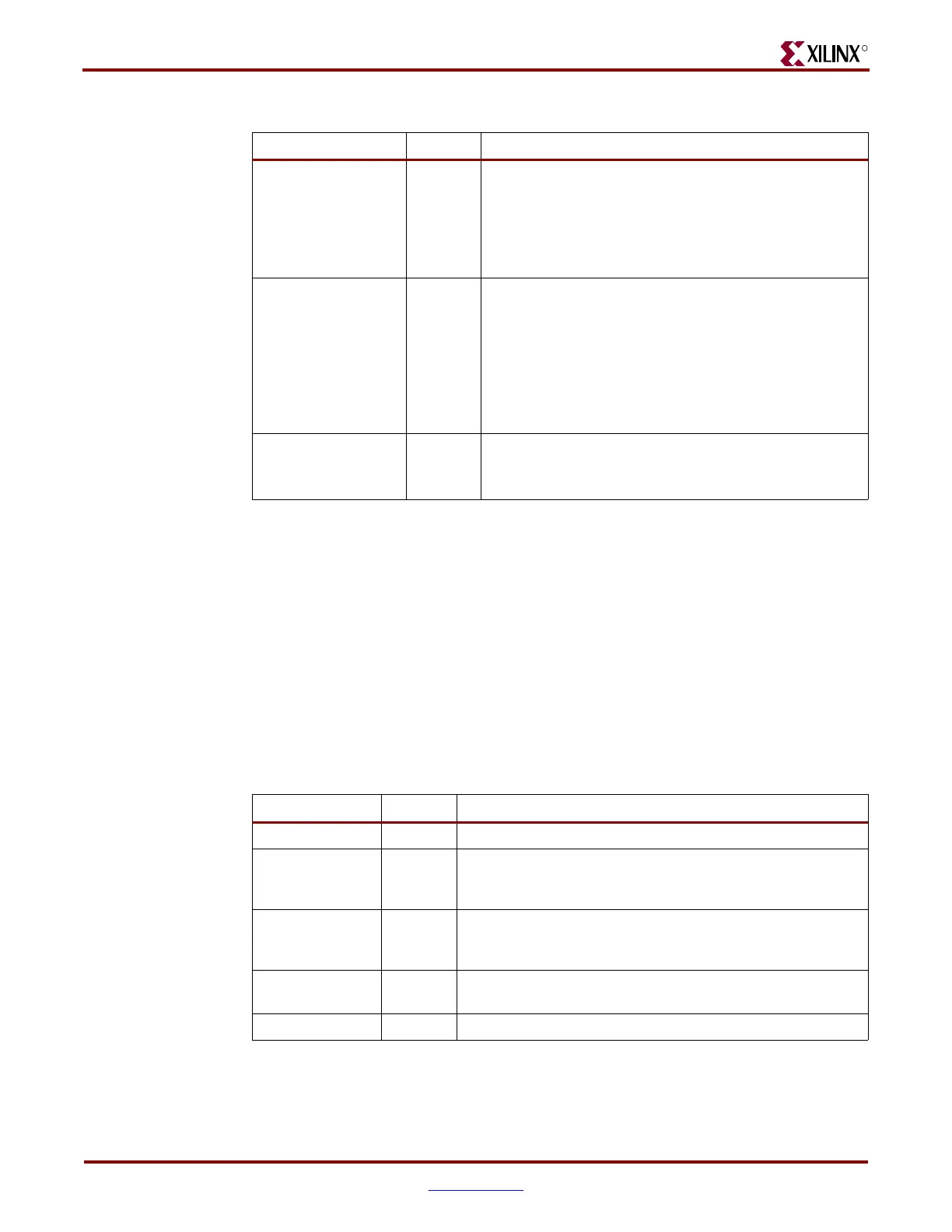

PERSIST

3

The configuration interface defined by M2:M0 remains after

configuration. Typically used only with the SelectMAP

interface to allow reconfiguration and readback. See also

“SelectMAP Reconfiguration” in Chapter 2.

0: No (default)

1: Yes

GLUTMASK

8

GLUTMASK affects how certain memory cells are read back.

This applies to SRL16 and distributed RAM (LUTRAM) bits

as well as configuration bits that are accessible through a

DRP port.

0=Readback all 0s from SRL16 and Distributed RAM. Use

with active device readback.

1=Readback dynamic values from SFR16 and Distributed

RAM. Use with shutdown readback.

GTS_USER_B

0

Active Low high-Z state for I/Os.

0: I/Os placed in high-Z state

1: I/Os active

Table 7-7: Control Register Description (Continued)

Name Bit Index Description

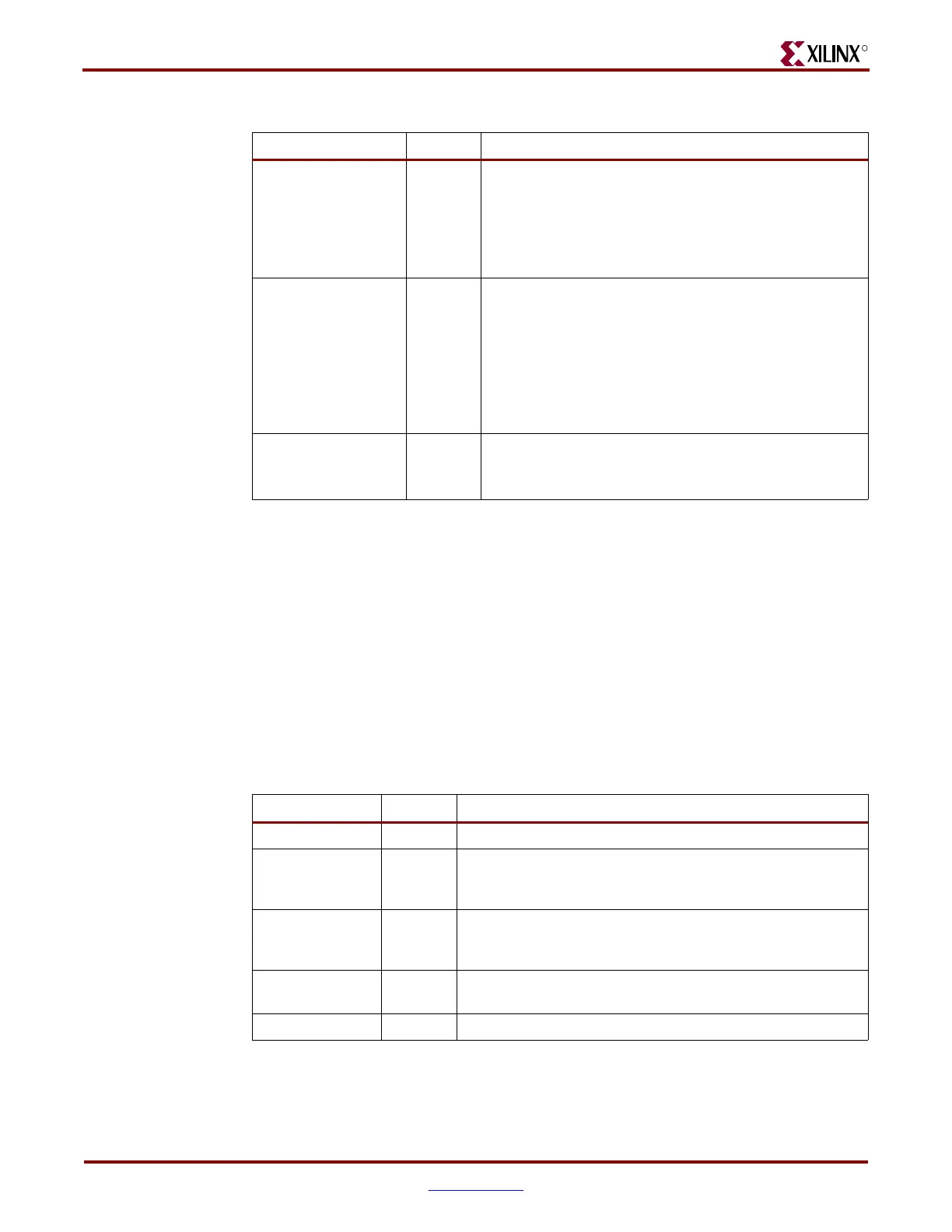

Table 7-8: Frame Address Register Description

Address Type Bit Index Description

Top_B Bit 22 Select between top-half rows and bottom-half rows.

Block Type 21:19 Block types are, CLB/IO/CLK (000), block RAM Interconnect

(001), block RAM content (010), CFG_CLB (011), and

CFG_BRAM (100). A normal bitstream stops at type 010.

Row Address 18:14 Selects a row of frames, for example, a row of 16 CLBs in height,

with an HCLK row in the middle. The row addresses increase

away from the middle (in both top and bottom).

Column Address 13:6 Selects a major column, such as a column of CLBs. Column

addresses start at 0 on the left and increase to the right.

Minor Address 5:0 Selects a memory-cell address line within a major column.

Loading...

Loading...