42 www.xilinx.com Virtex-4 FPGA Configuration User Guide

UG071 (v1.12) June 2, 2017

Chapter 2: Configuration Interfaces

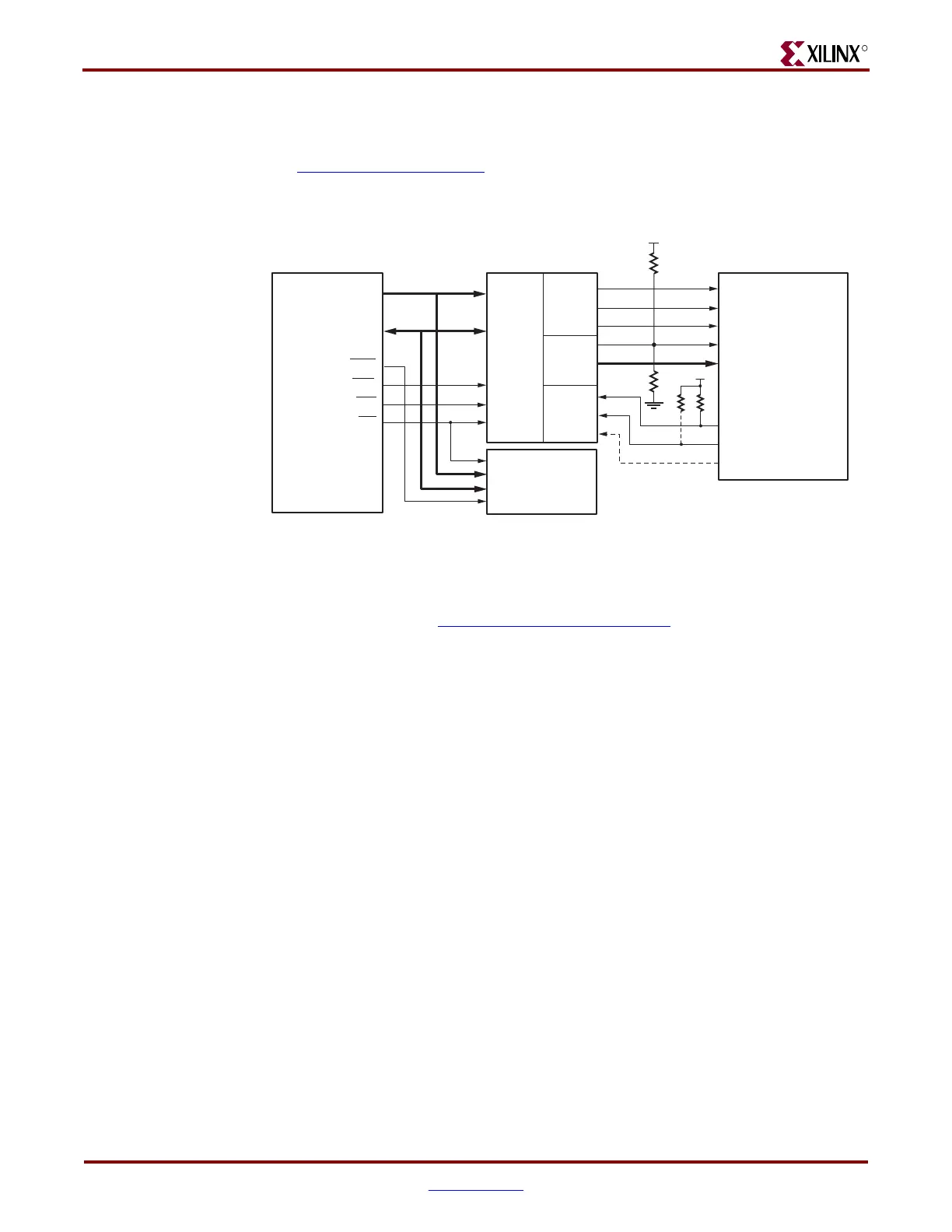

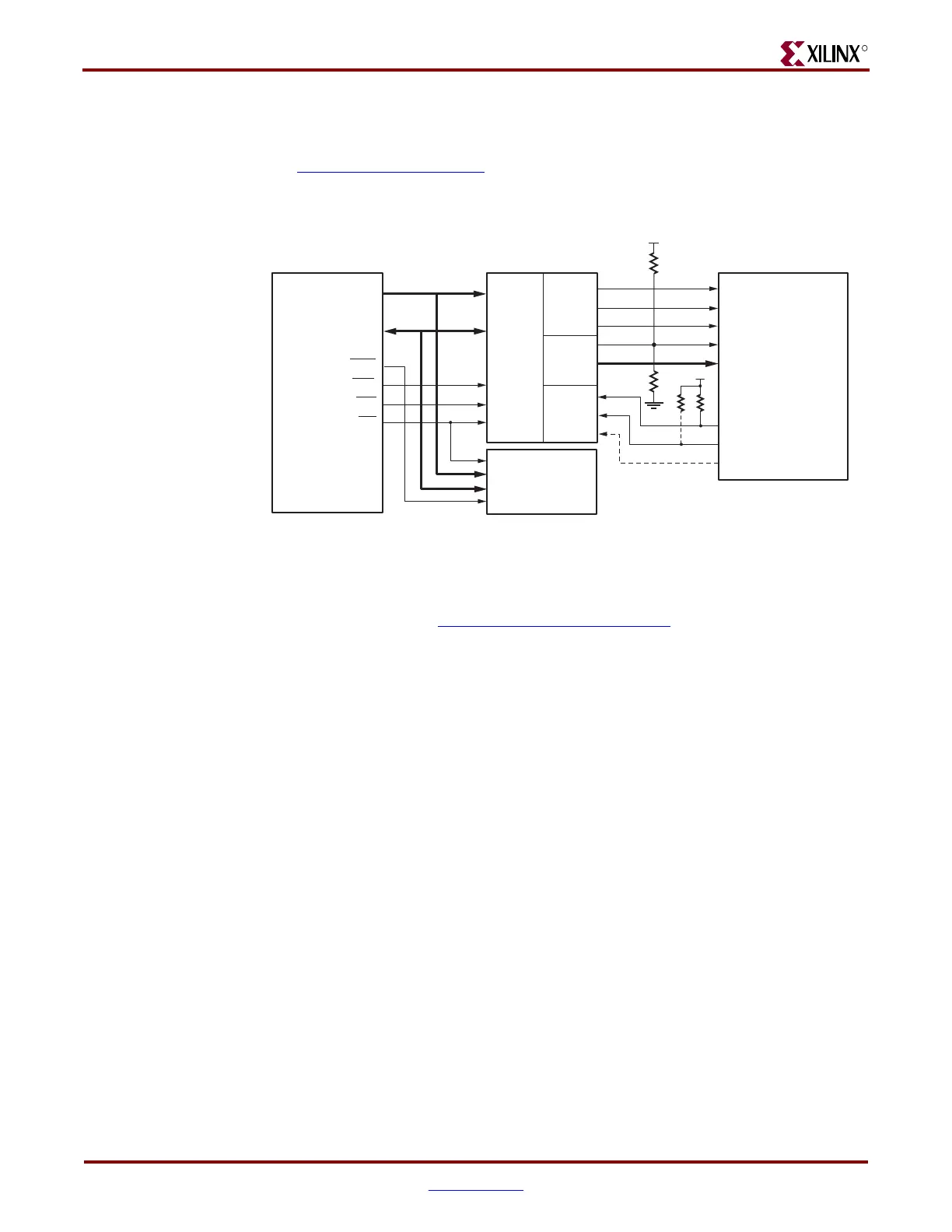

For custom applications where a microprocessor or CPLD is used to configure a single

Virtex-4 device, either Master or Slave SelectMAP mode can be used (Figure 2-13). See

Xilinx Application Note XAPP502

for information on configuring Virtex devices using a

microprocessor). Refer to “SelectMAP Data Loading” for details on handling the CS_B,

RDWR_B, and BUSY signals.

Notes relevant to Figure 2-13:

1. This schematic is from Xilinx Application Note XAPP502

. It is one of many possible

implementations.

2. The DONE pin is by default an open-drain output requiring an external pull-up

resistor. A 330Ω pull-up resistor is recommended. In this arrangement, the active

DONE driver can be enabled, eliminating the need for an external pull-up resistor.

3. The INIT_B pin is a bidirectional, open-drain pin. An external pull-up resistor is

required.

4. The BitGen startup clock setting must be set for CCLK for SelectMAP configuration.

5. The BUSY signal can be left unconnected if readback is not needed.

6. The CS_B and RDWR_B signals can be tied to ground if only one FPGA is going to be

configured and readback is not needed.

7. The CCLK net requires Thevenin parallel termination. See “Board Layout for

Configuration Clock (CCLK),” page 34.

Multiple Device SelectMAP Configuration

Multiple Virtex-4 devices in Slave SelectMAP mode can be connected on a common

SelectMAP bus (Figure 2-14). In a SelectMAP bus, the data pins (SelectMAP data, CCLK,

RDWR_B, BUSY, PROGRAM_B, DONE, and INIT_B share a common connection between

all of the devices. To allow each device to be accessed individually, the CS_B (Chip Select)

inputs must not be tied together. External control of the CS_B signal is required and is

usually provided by a microprocessor or CPLD.

If Readback is going to be performed on the device after configuration, the RDWR_B and

BUSY signals must be handled appropriately. (For details, refer to Chapter 8)

Figure 2-13: Single Slave Device SelectMAP Configuration

from Microprocessor and CPLD

Microprocessor

CPLD

Virtex-4

Slave

SelectMAP

Memory

Program

Register

Config.

Register

Input

Register

Used for storage

of the configuration

bitstream

ug071_19_073007

ADDRESS

DATA

CSO

CS1

WE

OE

PROGRAM_B

CS_B

RDWR_B

CCLK

D[0:7]

INIT_B

DONE

BUSY

(3)(2)

(7)

(7)

Loading...

Loading...