Virtex-4 FPGA Configuration User Guide www.xilinx.com 19

UG071 (v1.12) June 2, 2017

Bitstream Loading (Steps 4-7)

the device to upcoming configuration data and aligns the configuration data with the

internal configuration logic. Any data on the configuration input pins prior to

synchronization is ignored.

Synchronization is transparent to most users because all configuration bitstreams (.bit

files) generated by the Xilinx ISE® Bitstream Generator (BitGen) software include the

synchronization word. Table 1-5 shows signals relating to synchronization.

Check Device ID (Step 5)

Once the device is synchronized, a device ID check must pass before the configuration data

frames can be loaded. This prevents an attempted configuration with a bitstream that is

formatted for a different device.

For example, the device ID check should prevent an XC4VLX15 from being configured

with an XC4VLX80 bitstream.

The device ID check is built into the bitstream, making this step transparent to most

designers. Figure 1-7 shows the relative position of the device ID check, Table 1-6 shows

the Virtex-4 device IDs, and Table 1-7 shows the signals relating to the device ID check. The

device ID check is performed through commands in the bitstream to the configuration

logic, not through the JTAG IDCODE register in this case.

Table 1-5: Signals Relating to Synchronization

Signal Name Type Access Description

DALIGN Status Only available through the

SelectMAP interface during an

ABORT. (See “Configuration

Abort Sequence Description,”

page 49.)

Indicates whether device

is synchronized.

Figure 1-7: Check Device ID (Step 5)

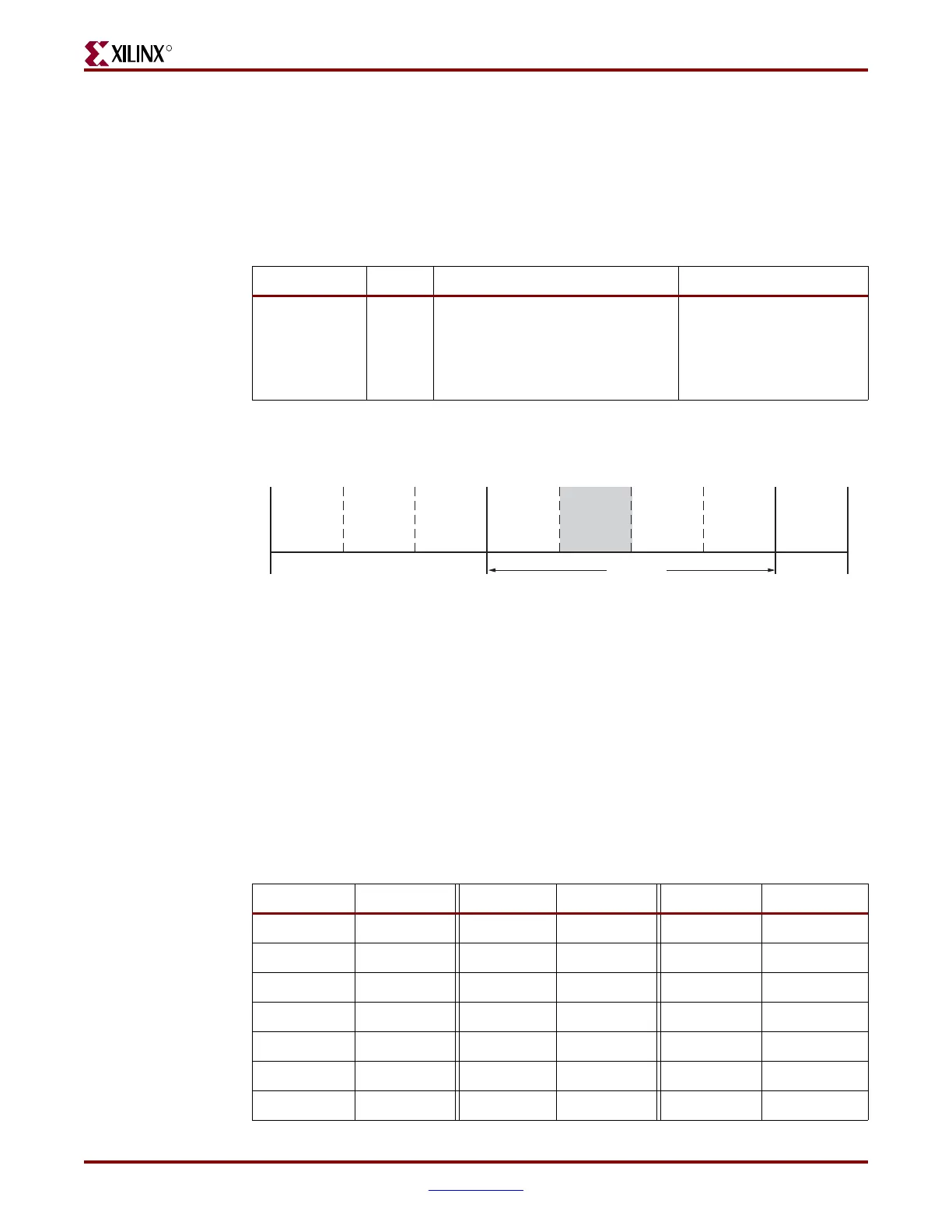

Table 1-6: Virtex-4 Device ID Codes

Device IDCODE Device IDCODE Device IDCODE

XC4VLX15 01658093 XC4VFX12 01E58093

XC4VLX25 0167C093 XC4VSX25 02068093 XC4VFX20 01E64093

XC4VLX40 016A4093 XC4VSX35 02088093 XC4VFX40 01E8C093

(1)

XC4VLX60 016B4093 XC4VSX55 020B0093 XC4VFX60 01EB4093

XC4VLX80 016D8093

XC4VLX100 01700093 XC4VFX100 01EE4093

XC4VLX160 01718093 XC4VFX140 01F14093

Device

Power-Up

Sample Mode

Pins

Synchronization

Device ID

Check

CRC Check

Clear

Configuration

Memory

Startup

Sequence

Load

Configuration

Data

Start

Finish

ug071_07_122105

Bitstream

Loading

Steps

12345678

Loading...

Loading...