Virtex-4 FPGA Configuration User Guide www.xilinx.com 61

UG071 (v1.12) June 2, 2017

Boundary-Scan for Virtex-4 Devices Using IEEE Standard 1149.1

Boundary-Scan Architecture

Virtex-4 device registers include all registers required by the IEEE 1149.1 Standard. In

addition to the standard registers, the family contains optional registers for simplified

testing and verification (Table 3-2).

Boundary-Scan Register

The test primary data register is the Boundary-Scan register. Boundary-Scan operation is

independent of individual IOB configurations. Each IOB, bonded or un-bonded, starts as

bidirectional with 3-state control. Later, it can be configured to be an input, output, or

3-state only. Therefore, three data register bits are provided per IOB (Figure 3-3).

When conducting a data register (DR) operation, the DR captures data in a parallel fashion

during the CAPTURE-DR state. The data is then shifted out and replaced by new data

during the SHIFT-DR state. For each bit of the DR, an update latch is used to hold the input

data stable during the next SHIFT-DR state. The data is then latched during the

UPDATE-DR state when TCK is Low. The internal DR CLK follows TCK when the TAP

controller is in the CAPTURE-DR state and SHIFT-DR state, however, it can toggle in other

states.

The update latch is opened each time the TAP controller enters the UPDATE-DR state. Care

is necessary when exercising an INTEST or EXTEST to ensure that the proper data has been

latched before exercising the command. This is typically accomplished by using the

SAMPLE/PRELOAD instruction.

Consider internal pull-up and pull-down resistors when developing test vectors for testing

opens and shorts. The Boundary-Scan mode determines whether the IOB has a pull-up

resistor. Figure 3-3 is a representation of Virtex-4 Boundary-Scan architecture.

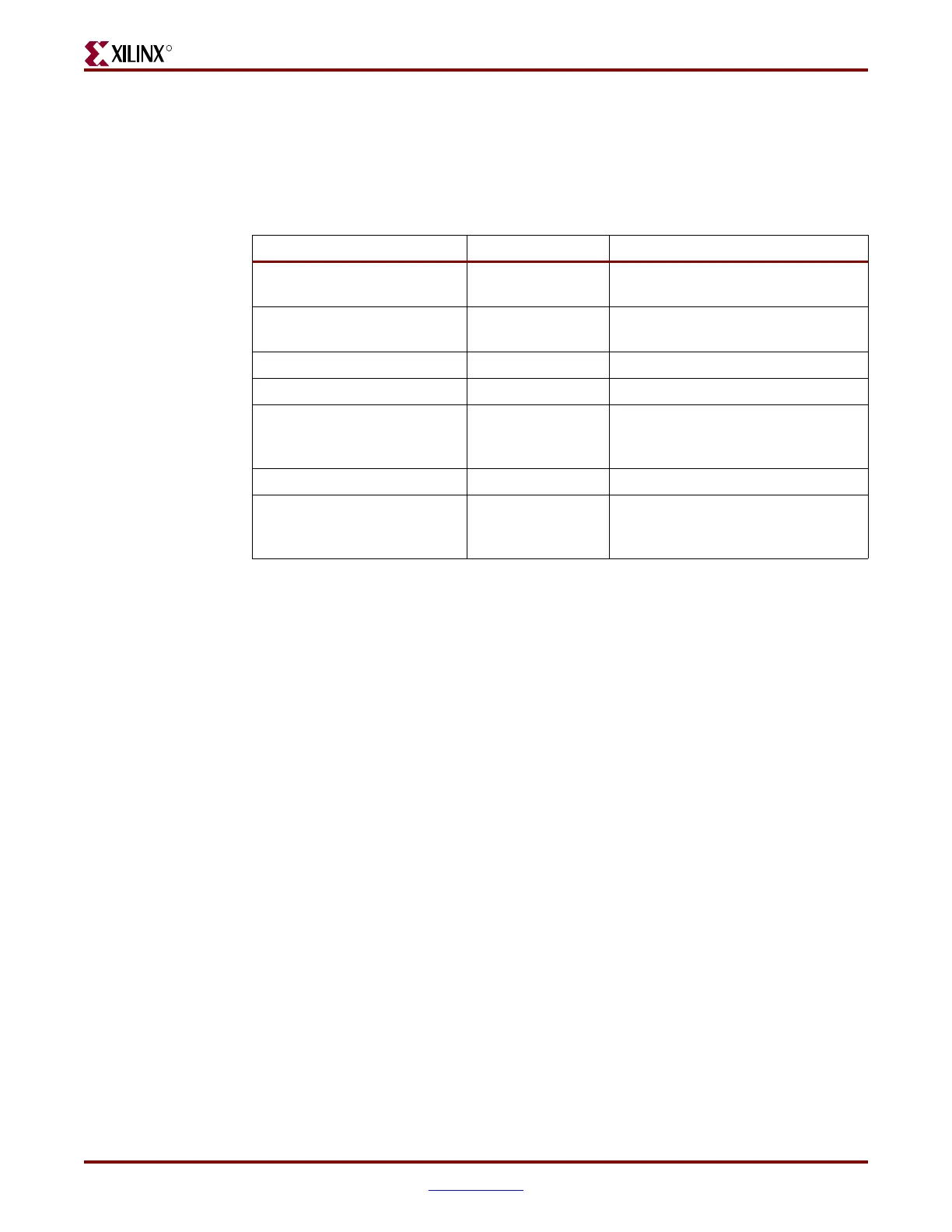

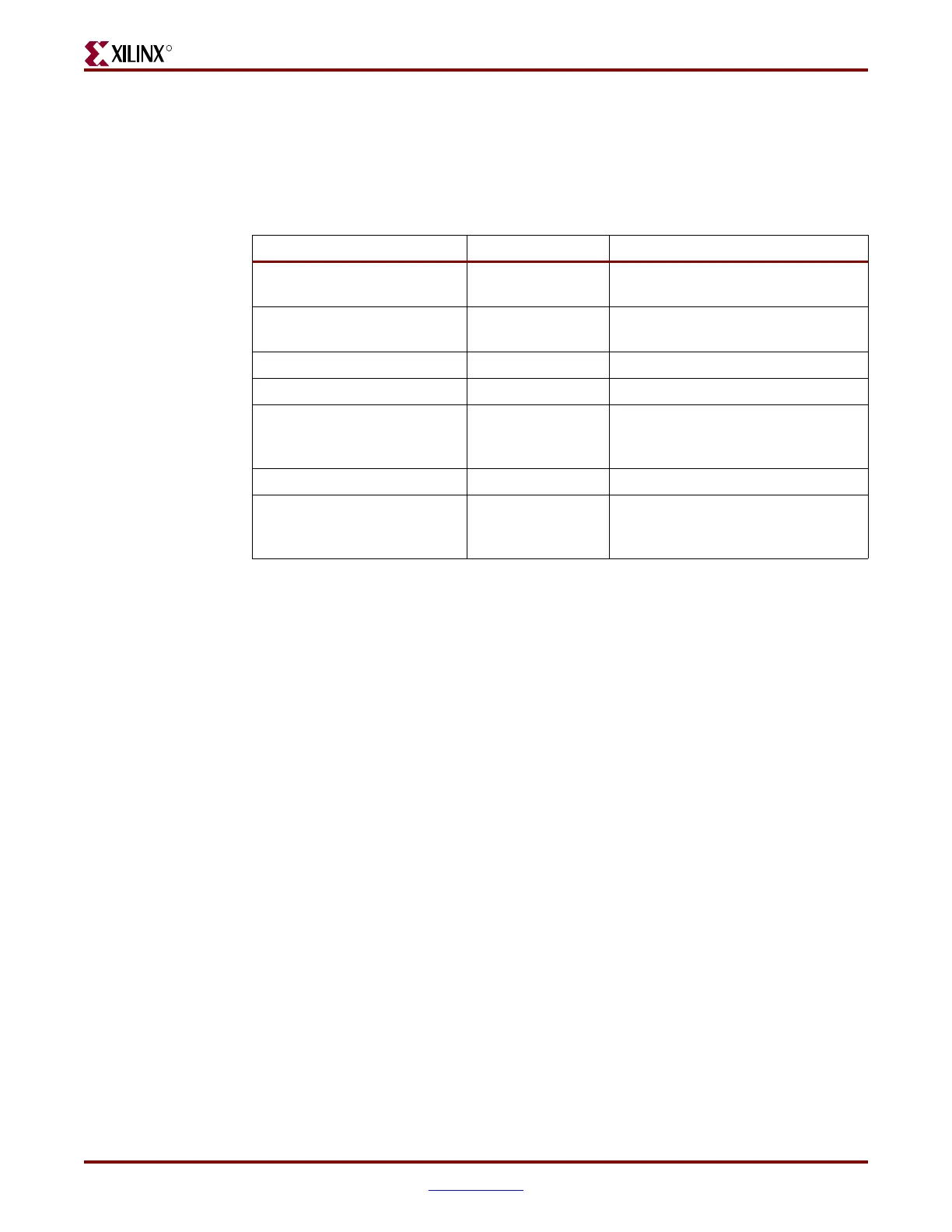

Table 3-2: Virtex-4 JTAG Registers

Register Name Register Length Description

Boundary-Scan Register 3 bits per I/O

Controls and observes input,

output, and output enable.

Instruction Register 10 bits

Holds current instruction OPCODE

and captures internal device status.

Bypass Register 1 bit Device bypass.

Identification Register 32 bits Captures device ID.

JTAG Configuration Register 32 bits

Allows access to the configuration

bus when using the CFG_IN or

CFG_OUT instructions.

USERCODE Register 32 bits Captures user-programmable code.

User-Defined Registers

(USER1, USER2, USER3,

and USER4)

Design-specific Design-specific.

Loading...

Loading...