Virtex-4 FPGA Configuration User Guide www.xilinx.com 93

UG071 (v1.12) June 2, 2017

Configuration Control Logic

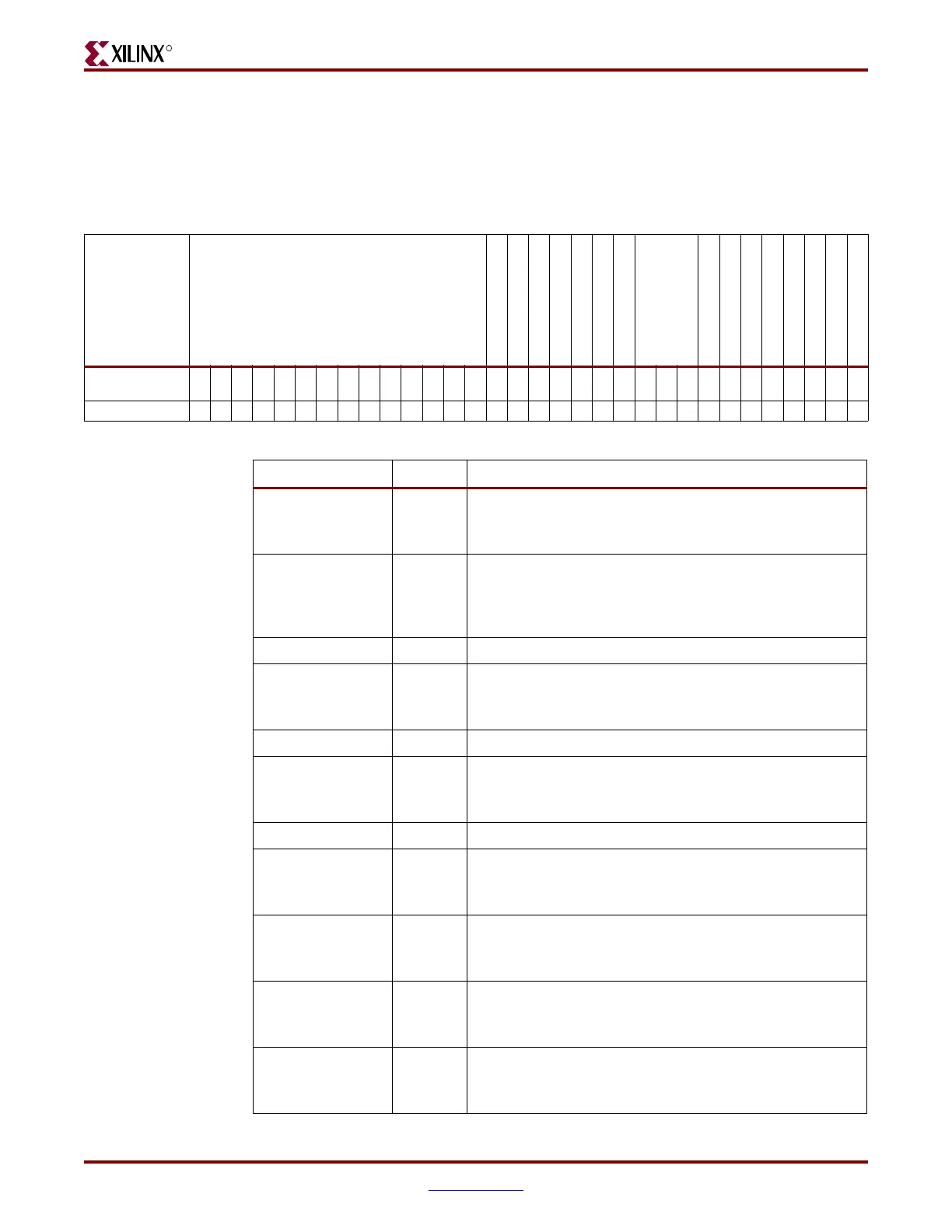

Status Register (STAT)

The Status Register indicates the value of numerous global signals. The register can be read

through the SelectMAP or JTAG interfaces. Figure 7-2 gives the name of each bit position in

the STAT register; a detailed explanation of each bit position is given in Table 7-9.

Figure 7-2: Status Register

Description

–

Reserved

DEC_ERROR

ID_ERROR

DONE

RELEASE_DONE

INIT

INIT_COMPLETE

MODE

GHIGH_B

GWE

GTS_CFG_B

EOS

DCI_MATCH

DCM_LOCK

PART_SECURED

CRC_ERROR

Bit Index

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0

9 8 76543 210

Value 0000000000000000xxxxxxxxxxxxxxxx

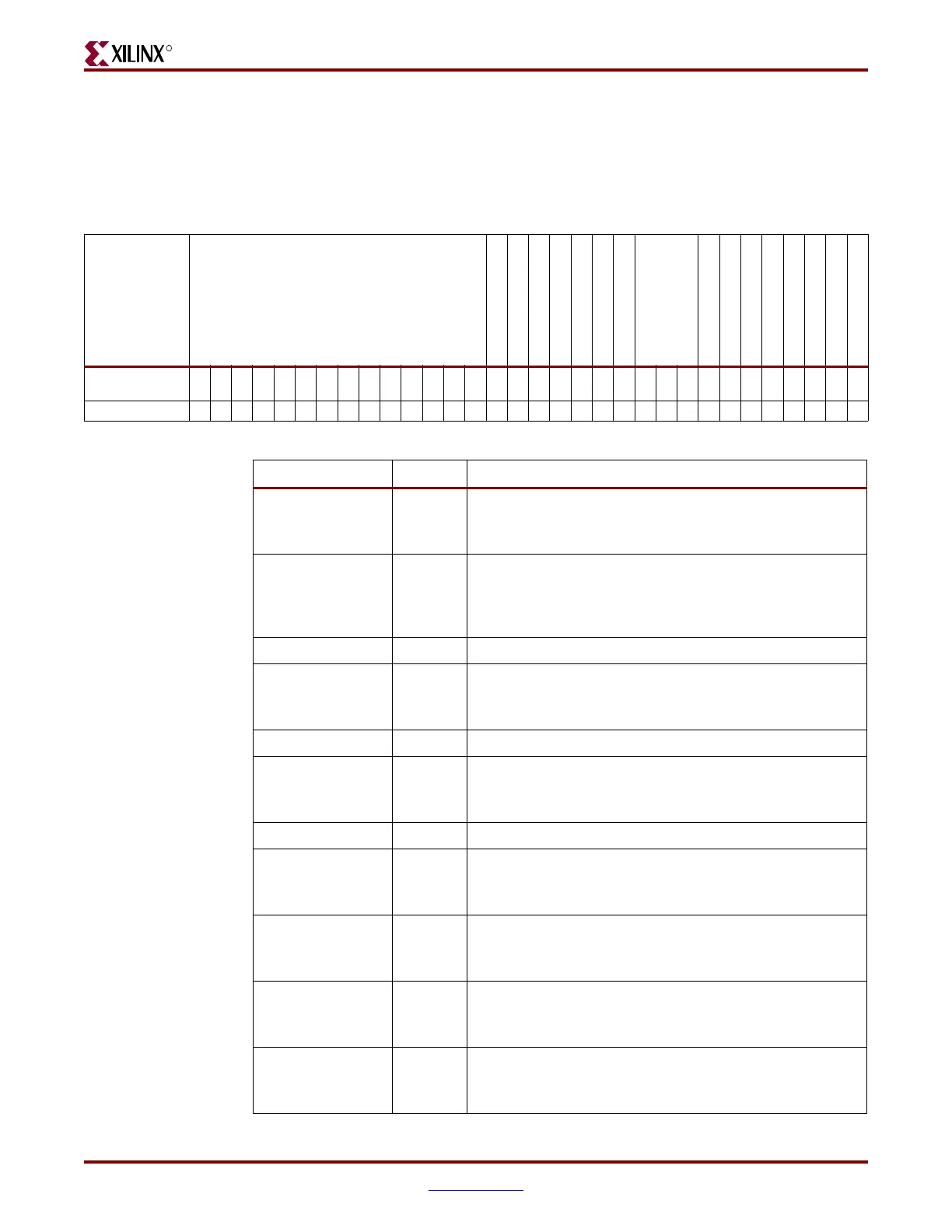

Table 7-9: Status Register Description

Name Bit Index Description

DEC_ERROR

16

FDRI write attempted before or after decrypt operation.

0: No DEC_ERROR

1: DEC_ERROR

ID_ERROR

15

Attempt to write to FDRI without successful DEVICE_ID

check.

0: No ID_ERROR

1: ID_ERROR

DONE

14 Value on DONE pin.

RELEASE_DONE

13

Value of internal DONE signal.

0: DONE signal not released (pin is actively held Low)

1: DONE signal released (can be held Low externally)

INIT

12 Value on INIT pin

INIT_COMPLETE

11

Internal signal indicating initialization has completed.

0: Initialization has not finished

1: Initialization finished

MODE

10:8 Status of the MODE pins (M2:M0).

GHIGH_B

7

Status of GHIGH_B.

0: GHIGH_B asserted

1: GHIGH_B deasserted

GWE

6

Status of GWE.

0: FFs and block RAM are write disabled

1: FFs and block RAM are write enabled

GTS_CFG_B

5

Status of GTS_CFG_B.

0: All I/Os are placed in high-Z state

1: All I/Os behave as configured

EOS

4

End of Startup signal from Startup Block.

0: Startup sequence has not finished

1: Startup sequence has finished

Loading...

Loading...