40 www.xilinx.com Virtex-4 FPGA Configuration User Guide

UG071 (v1.12) June 2, 2017

Chapter 2: Configuration Interfaces

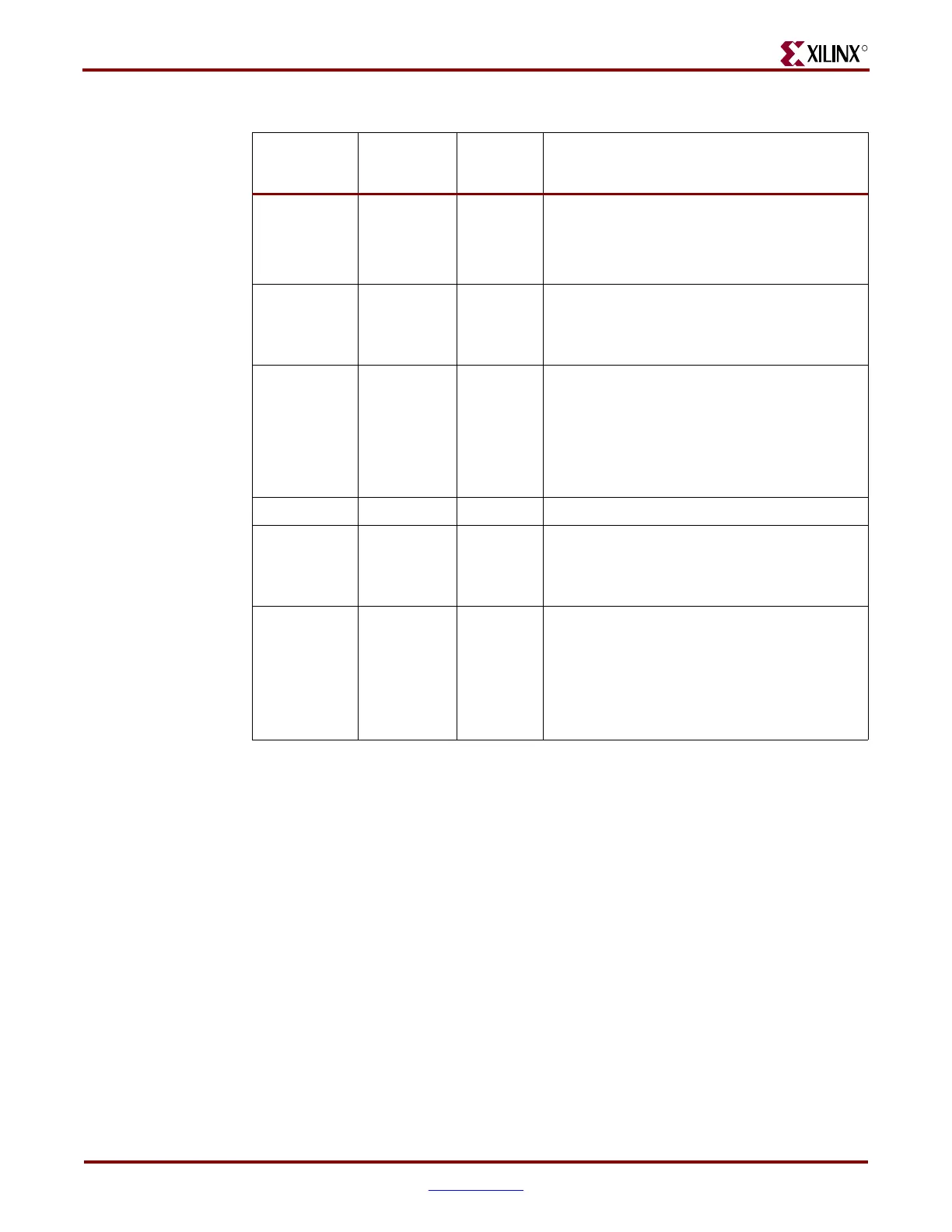

DOUT_BUSY

Three-State

Output

Dedicated

Indicates that the device is not ready to send

readback data. For Virtex-4 devices, the BUSY

signal is only needed for readback; it is not needed

for configuration (see “SelectMAP Data

Loading”).

DONE

Bidirectional,

Open-Drain

or active

Dedicated

Active High signal indicating configuration is

complete:

0 = FPGA not configured

1 = FPGA configured

INIT_B

Input or

Output,

Open-Drain

Dedicated

Before MODE pins are sampled, INIT_B is an

input that can be held Low to delay configuration.

After MODE pins are sampled, INIT_B is an open-

drain active Low output indicating whether a CRC

error occurred during configuration:

0 = CRC error

1 = No CRC error

PROGRAM_B Input Dedicated Active-Low asynchronous full-chip reset

CS_B Input Dedicated

Active-Low chip select to enable the SelectMAP

data bus (see “SelectMAP Data Loading”):

0 = SelectMAP data bus enabled

1 = SelectMAP data bus disabled

(2)

RDWR_B Input Dedicated

Determines the direction of the SelectMAP data

bus (see “SelectMAP Data Loading”):

0 = inputs

1 = outputs

RDWR_B input can only be changed while CS_B is

deasserted, otherwise an ABORT occurs (see

“SelectMAP ABORT”)

(2)

.

Notes:

1. If SelectMAP32 is used and the bitstream is compressed by the -g compress in BitGen then the

CONFIG_MODE constraint must be used. the values for the CONFIG_MODE constraint are either

S_SelectMAP32 or S_SelectMAP32+READBACK. S_SelectMAP32+READBACK preserves the

S_SelectMAP32 data pins for readback (also known as persist).

2. If the SelectMAP interface is not used, the CS_B and RDWR_B pins can be left unconnected. Weak

pullups pull these pins High, and their state is ignored.

Table 2-4: Virtex-4 SelectMAP Configuration Interface Pins (Continued)

Pin Name Type

Dedicated

or Dual-

Purpose

Description

Loading...

Loading...