Virtex-4 FPGA Configuration User Guide www.xilinx.com 63

UG071 (v1.12) June 2, 2017

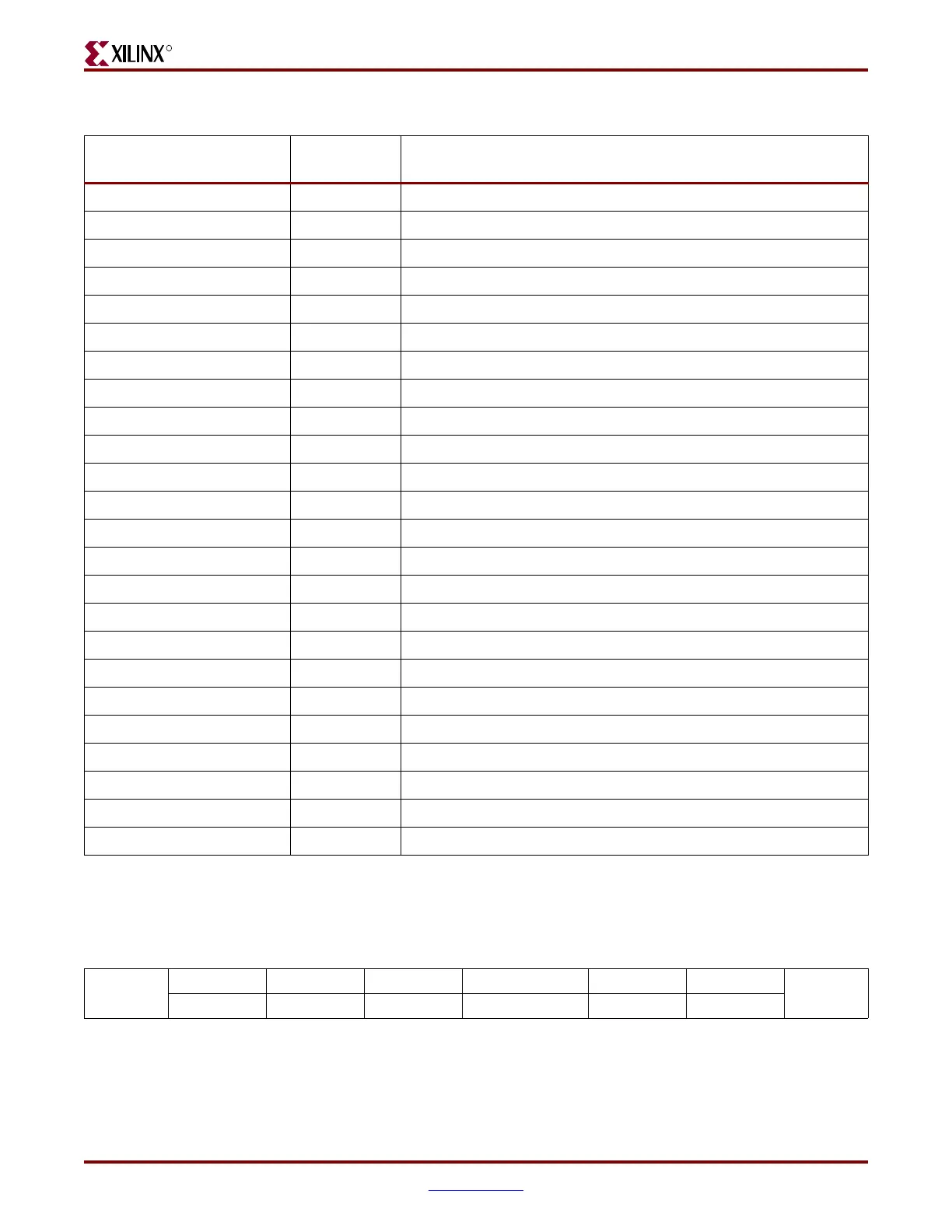

Boundary-Scan for Virtex-4 Devices Using IEEE Standard 1149.1

Table 3-3: Virtex-4 Boundary-Scan Instructions

Boundary-Scan Command

Binary Code

(9:0)

Description

EXTEST 1111000000 Enables Boundary-Scan EXTEST operation

SAMPLE 1111000001 Enables Boundary-Scan SAMPLE operation

USER1 1111000010 Access user-defined register 1

USER2 1111000011 Access user-defined register 2

USER3 1111100010 Access user-defined register 3

USER4 1111100011 Access user-defined register 4

CFG_OUT 1111000100 Access the configuration bus for readback

CFG_IN 1111000101 Access the configuration bus for configuration

INTEST 1111000111 Enables Boundary-Scan INTEST operation

USERCODE 1111001000 Enables shifting out user code

IDCODE 1111001001 Enables shifting out of ID code

HIGHZ 1111001010 3-state output pins while enabling Bypass Register

JPROGRAM 1111001011 Equivalent to and has the same affect as PROGRAM

JSTART 1111001100 Clocks the start-up sequence when StartClk is TCK

JSHUTDOWN 1111001101 Clocks the shutdown sequence

ISC_ENABLE 1111010000 Marks the beginning of ISC configuration. Full shutdown is executed

ISC_PROGRAM 1111010001 Enables in-system programming

ISC_PROGRAM_SECURITY 1111010010 Change security status from secure to non-secure mode and vice versa

ISC_ADDRESS_SHIFT 1111010011 For programming, key address is shifted first, before the key

ISC_NOOP 1111010100 No operation

ISC_READ 1111010101 Used to read back BBR

ISC_DISABLE 1111010111 Completes ISC configuration. Startup sequence is executed

BYPASS 1111111111 Enables BYPASS

RESERVED

All other codes

Xilinx reserved instructions

Notes:

1. For FX devices with two processors, the instruction codes are MSB extended with 1s. For example, the CFG_IN instruction is

1111 1111 000101.

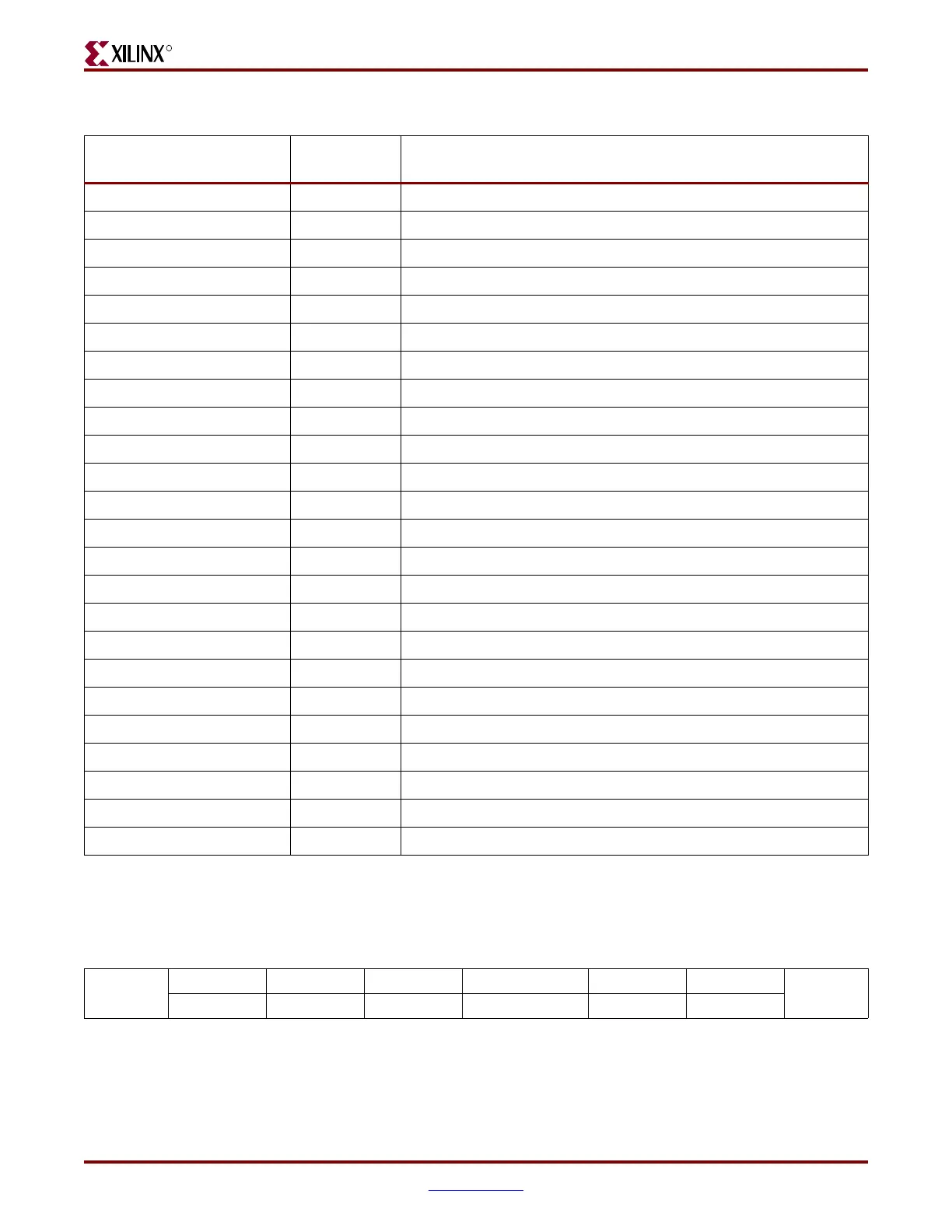

TDI →

IR[9:6] IR[5] IR[4] IR[3] IR[2] IR[1:0]

→ TDO

Reserved DONE INIT ISC_ENABLED ISC_DONE 0 1

Figure 3-4: Virtex-4 Instruction Capture Values Loaded into IR as Part of an Instruction Scan Sequence

Loading...

Loading...