150

*Notes: D includes D, HD; TD includes TD, HTD; CD includes CD, HCD, HSCD, HSD; DM

includes DM, DHM; DS includes DS, DHS. M includes M, HM, SM; S includes S, HS; T

includes T, HT; C includes C, HC.

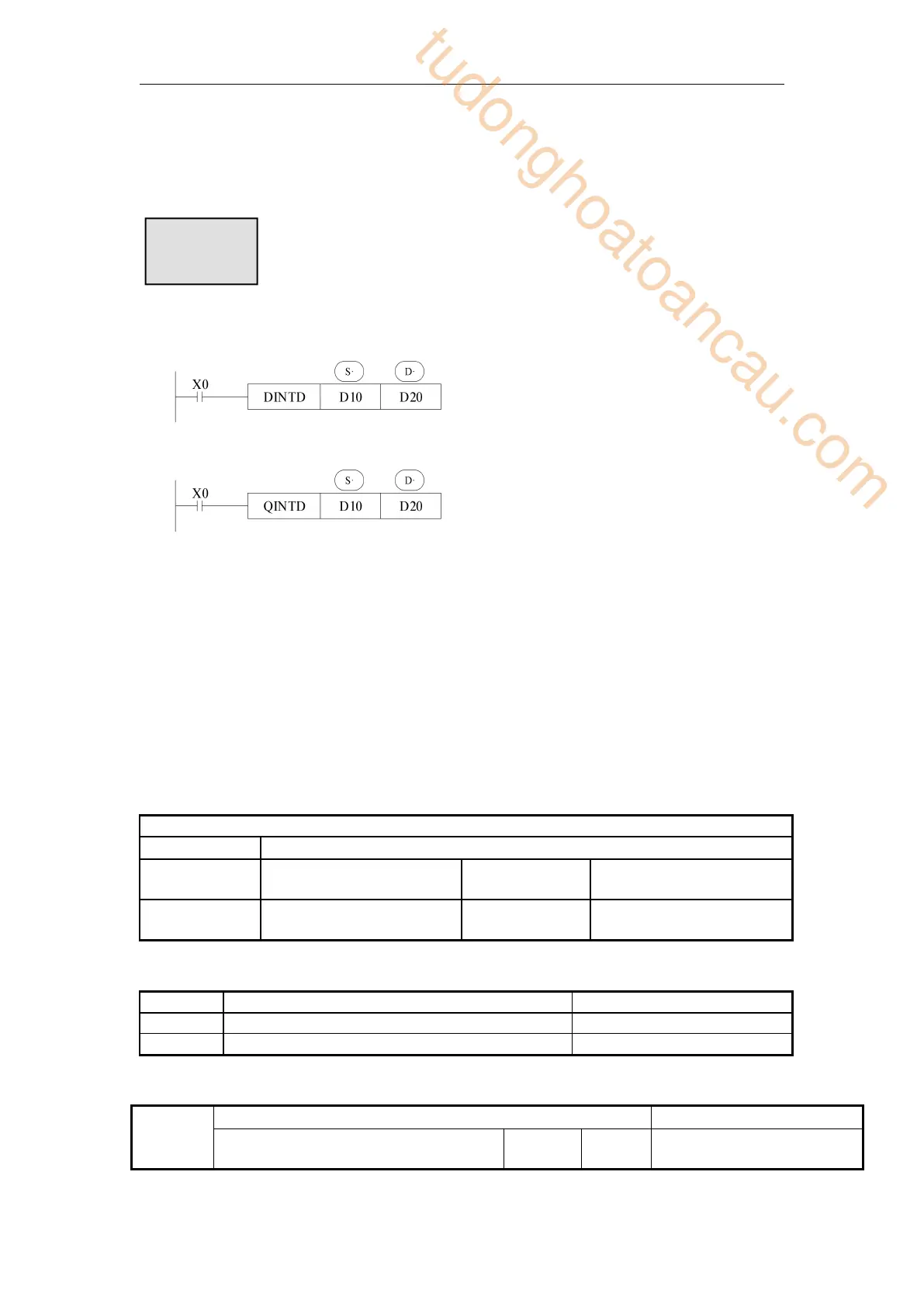

<32 bits instruction>

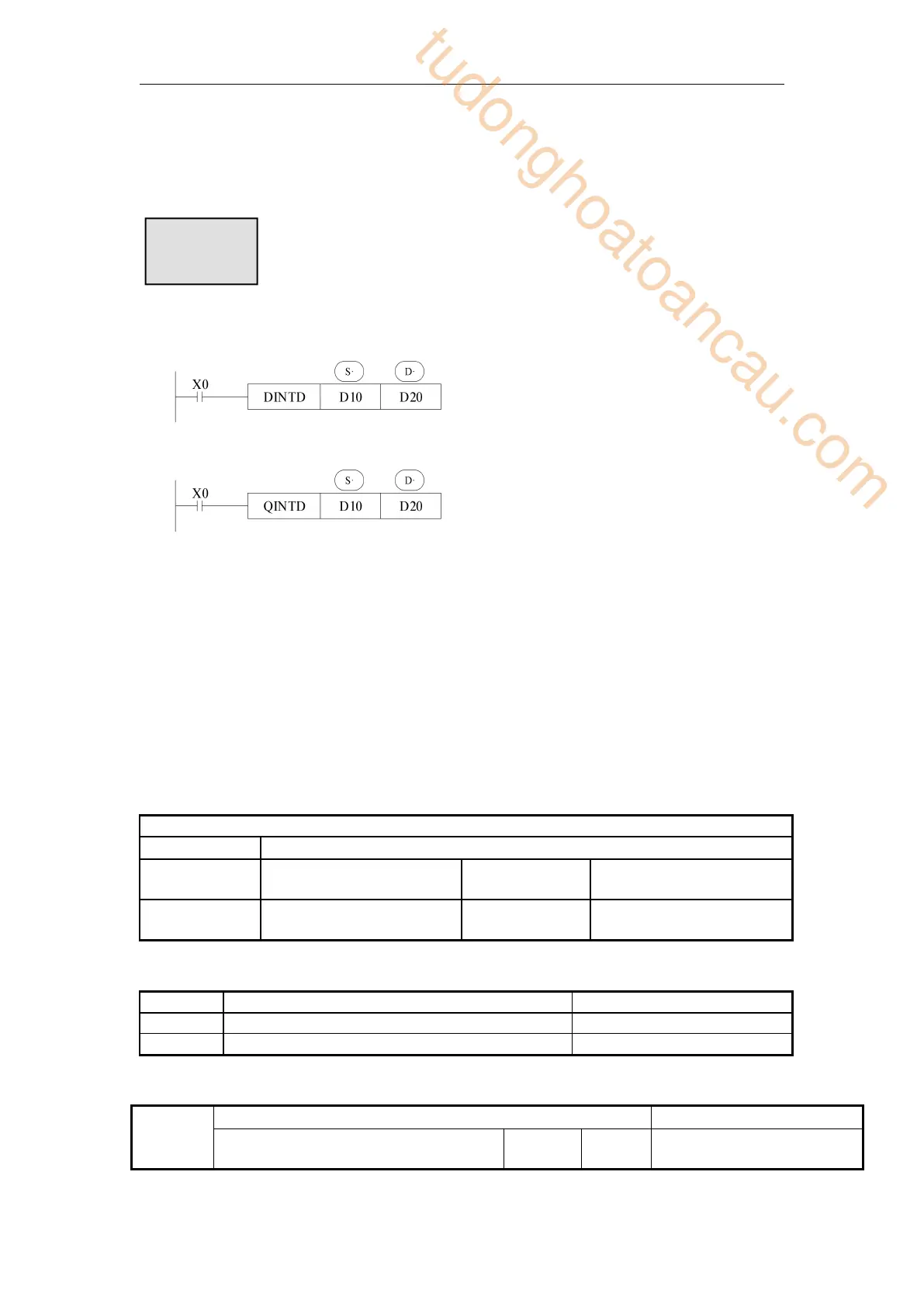

<64 bits instruction>

The binary source number is converted into a BIN integer and stored at the destination device.

Abandon the value behind the decimal point.

The inverse instruction is DFLTD/QFLTD.

For 64-bit instructions, the register address number must be even.

When the result is 0, the flag bit is ON.

The result is over below data, the carry flag is ON.

64 bits operation: -9223372036854775808~9223372036854775807。

4-8-7 Single precision floating point to double precision floating point[ECON]

1) Summary

Single precision floating point to double precision floating point [ECON]

Normal ON/OFF/falling

or rising pulse edge

2) Operands

Source soft element address

Target soft element address

3) Suitable soft components

(D13,D12,D11,D10) → (D21,D20)

Binary Float BIN integer

Give up the data after the decimal dot

(D13,D12,D11,D10)→ (D23,D22,D21,D20)

Binary Float BIN integer

Give up the data after the decimal dot

tudonghoatoancau.com

Loading...

Loading...