Preliminary Technical Data UG-1828

Rev. PrB | Page 159 of 277

After applying the interface gain, the signal is provided to the data port in 16-bit format. The baseband processor could retrieve the

interface gain through API commands to scale the power of the received signal to determine the power at the input to the device (or at

the input to an external gain element if considered part of the digital gain compensation).

Mode 2: No Digital Gain Compensation with External Interface Gain Control

This mode is similar to mode 1 except that user controls the interface gain manually. Similarly, when in NB applications, the interface

gain range could be selected from 0 dB to 18 dB in 6 dB step size while in WB applications the interface gain is fixed at 0 dB.

Mode 3: Digital Gain Compensation with Internal Interface Gain Control

In this mode gain compensation is used and the interface gain is determined internally. The device should be loaded with gain tables that

compensate for the analog front-end attenuation applied. Thus, as the analog front-end attenuation is increased, and equal amount of

digital gain is applied. The interface gain is determined by RSSI. If the power level is too high, the Slicer will shift the signal properly

before sending to the data port to avoid saturation.

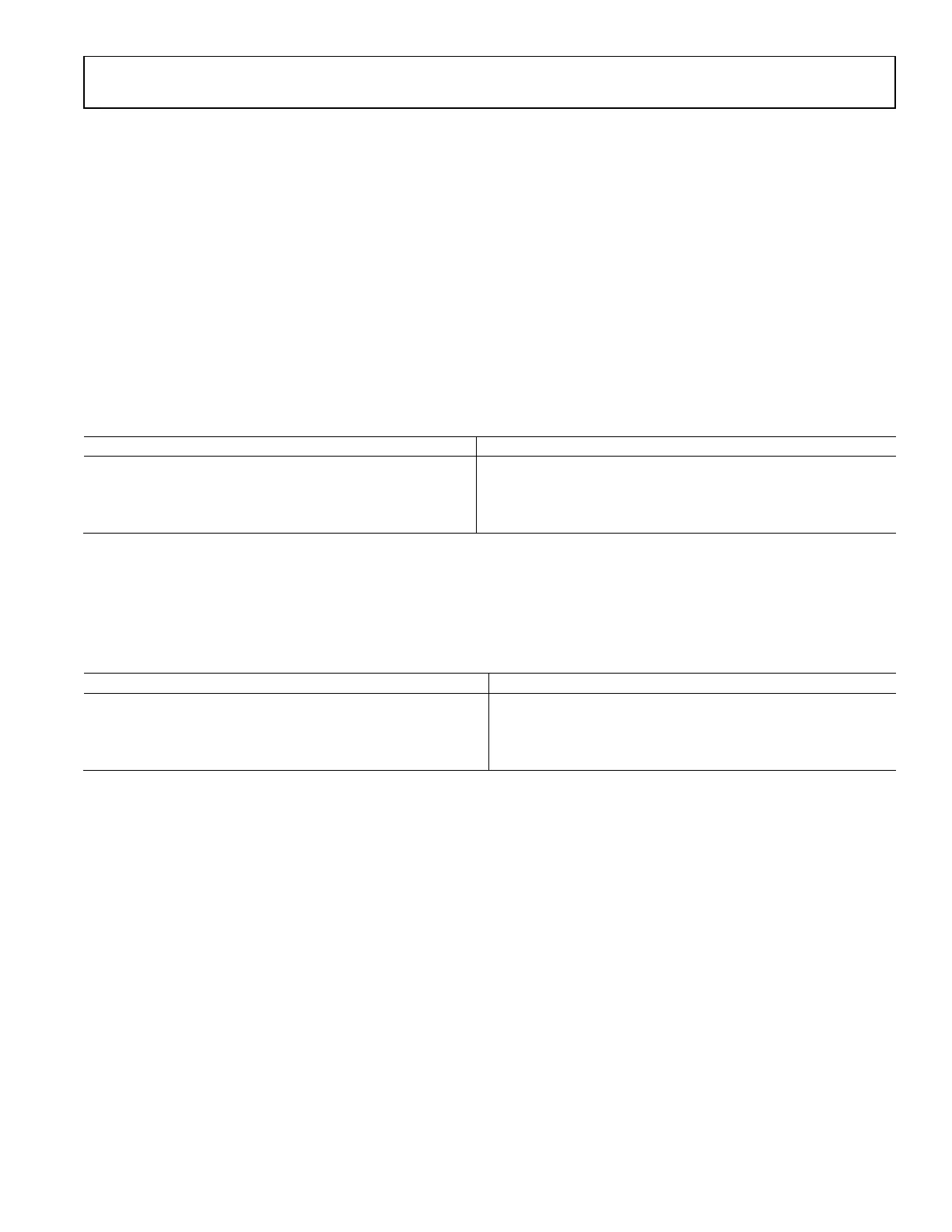

Slicer example: (note the following plots are only for showing the concepts which do not represent the actual implementation),

considering 3 different input signal power levels. The Power Level 1 fits a data length of 16 bit-width. The Power Level 2 is 0 dB to 6 dB

higher than Power Level 1which increases the bit-width by 1. The Power Level 3 is 6 dB to 12 dB higher than Power Level 1 which further

increases bit-width by 1. Figure 147 outlines this effect, with gray boxes indicating the valid (used) bits in each case.

D19 D18 D17 D16 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0D20D21D22

D19 D18 D17 D16 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0D20D21D22

D19 D18 D17 D16 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0D20D21D22

INPUT POWER LEVEL 1

INPUT POWER LEVEL 2

INPUT POWER LEVEL 3

24159-121

Figure 148. Bit Width of Input Signal with Increasing Power Levels

The slicer is used to attenuate the data such that it can fit into the resolution of the data port. Since the output is a shifted version of the

input, the slicer can only handle gains that are in ±6 dB steps.

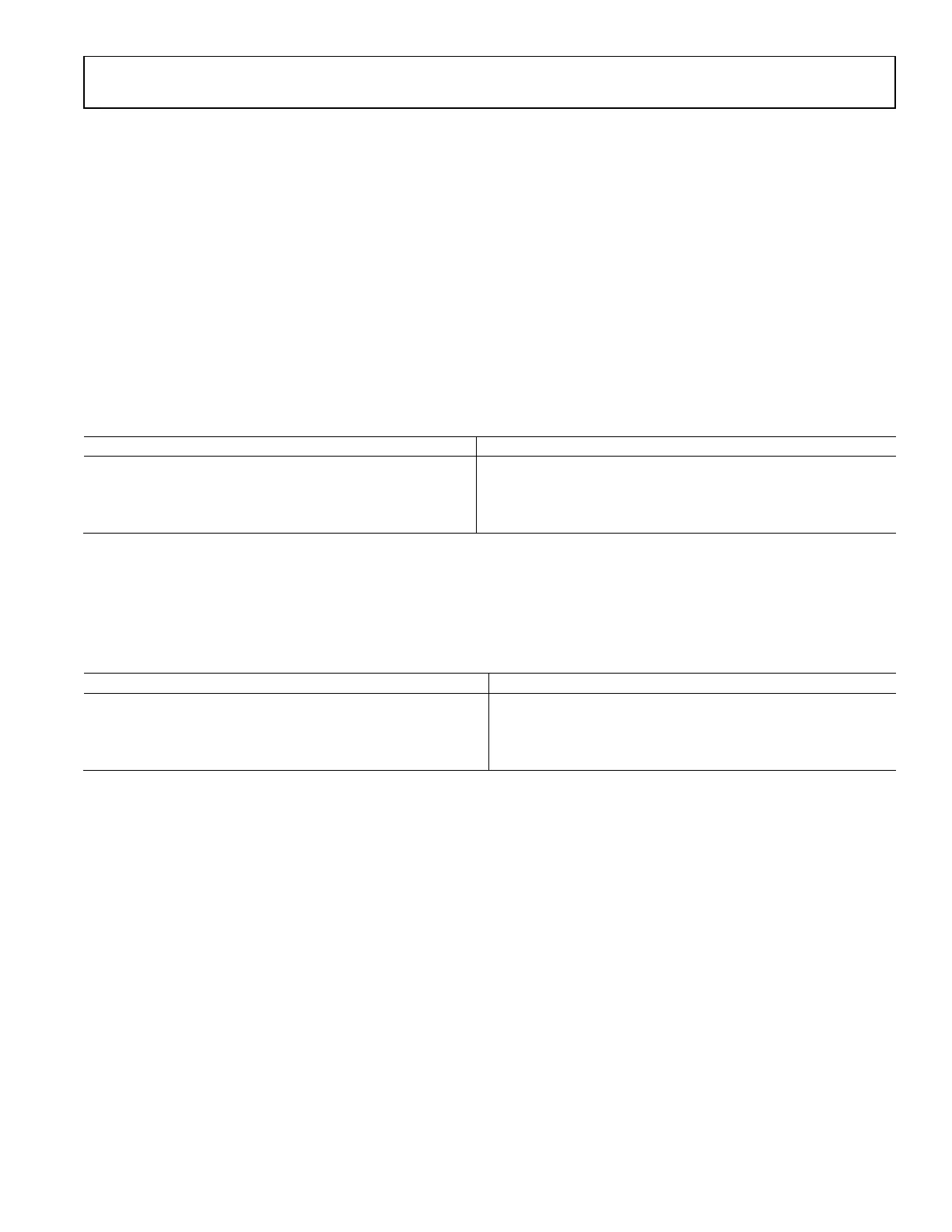

Figure 148 explains the slicer operation. For Power Level 1, the slicer shift value is calculated as 0 so the 16-bit output data is taken from

D15 – D0. As the power level increases, the bit-width of the signal has increased. For Power Level 2, now the bit-width is 17. The slicer

shift value becomes 1 so the 16-bit output data is taken from D16 – D1. This is equivalent to apply 6 dB of attenuation by slicer which

ensures that the bit-width of the signal is 16 once more; that is, the 16 MSBs have been selected (sliced) with the LSB dropped. When the

power level further increases as Power Level 2, the signal bit-width becomes 18-bit. The slicer shift value becomes 2 so the 16-bit output

data is taken from D17 – D2, which is equivalent to apply 12 dB of attenuation by slicer or slice the 16 MSBs dropping the 2 LSBs.

D19 D18

D17

D16

D15 D14

D13 D12 D11 D10 D9 D8

D7 D6

D5

D4 D3

D2

D1 D0D20D21

D22

D19 D18 D17 D16 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0D20D21D22

D19 D18 D17 D16 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0D20D21D22

SLICER SHIFT VALUE

0

1

2

INPUT POWER LEVEL 1

INPUT POWER LEVEL 2

INPUT POWER LEVEL 3

24159-122

Figure 149. Slicer Bit Selection with Different Input Power Levels

The slicer algorithm assumes a max PAR of 15dB and it adjusts the interface gain such that the measured signal power + 15 dB is less

than 0 dBFS. For NB applications, the interface gain is from −36 dB to +18 dB and for WB applications, the interface gain is from −36 dB

to 0 dB in 6 dB step size.

Similarly, the baseband processor could retrieve the interface gain through API commands to scale the power of the received signal to

determine the power at the input to the device (or at the input to an external gain element if considered part of the digital gain

compensation).

Mode 4: Digital Gain Compensation with External Interface Gain Control

This mode is similar to mode 3 except that user controls interface gain by selecting a proper value. The baseband processor could

measure the input signal power or use the power measurement done by RSSI in the device to determine the interface gain. Then through

API commands and the Slicer will operate in the same way as mentioned in mode 3. For NB applications, the interface gain is from −36 dB to

Loading...

Loading...