Preliminary Technical Data UG-1828

Rev. PrB | Page 51 of 277

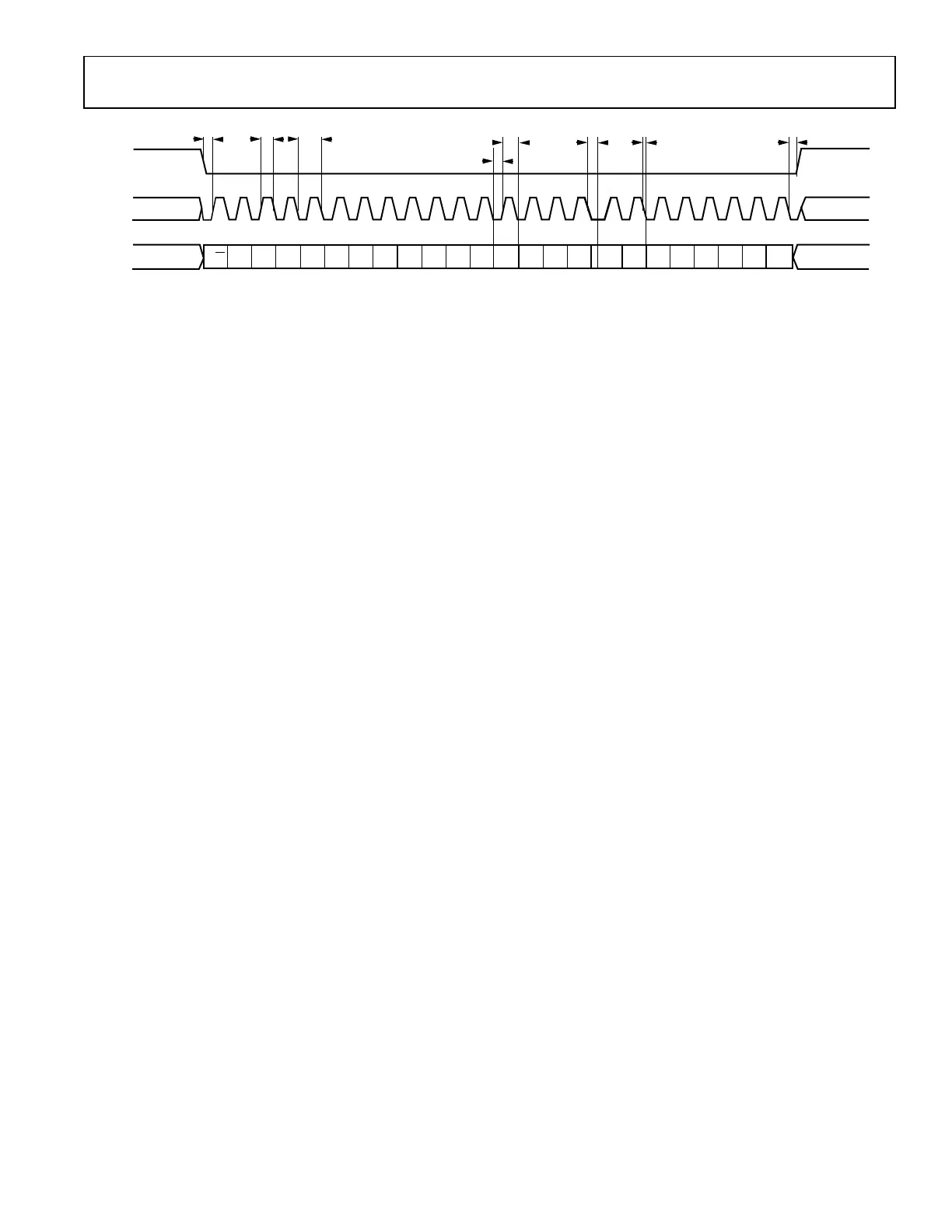

RX_DCLK_OUT

RX_STROBE_OUT

OR

RX_STROBE_OUT

RX_DATA_OUT

16 CYCLES (I SAMPLE) 16 CYCLES (Q SAMPLE) 224 CYCLES (NO SAMPLE)

I0_D15 I0_D14

I0_D0 Q0_D15

Q0_D14 Q0_D0

I0_D14I1_D15

24159-035

Figure 34. Receive CSSI timing with 8× Data Clock Rate for 16-Bit I/Q Data Sample (MSB First), 224 Cycles

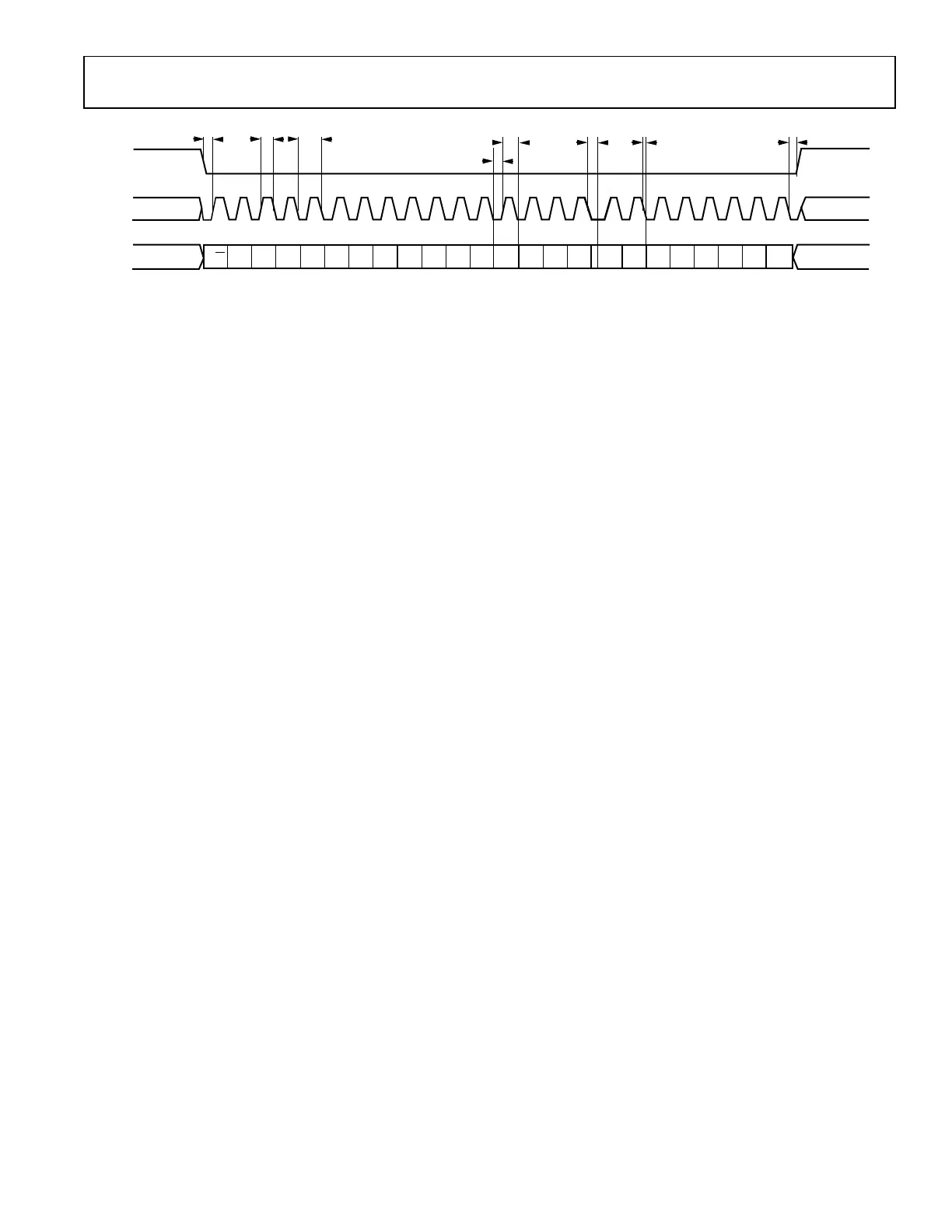

Figure 35, Figure 36, and Figure 37 illustrate the Receive CSSI interface (Rx1 and Rx2) in frequency deviation mode with 16-bit data

symbol with 2×, 4×, and 8× clock rates. The strobe pulse validates the start of the 16bits data symbol, the remaining data bits are ignored.

RX_CLOCK_OUT

RX_STROBE_OUT

OR

RX_STROBE_OUT

RX_DATA_OUT

16 CYCLES (I SAMPLE) 16 CYCLES (NO SAMPLE)

I0_D15 I0_D14 I0_D8 I0_D7 I0_D6 I0_D0 I0_D14I1_D15

24159-036

Figure 35. Receive CSSI Timing with 2× Data Clock Rate for 16-Bit Data Symbol (MSB First)

RX_CLOCK_OUT

RX_STROBE_OUT

OR

RX_STROBE_OUT

RX_DATA_OUT

16 CYCLES (I SAMPLE) 48 CYCLES (NO SAMPLE)

I0_D15 I0_D14 I0_D8 I0_D7 I0_D6

I0_D0 I0_D14I1_D15

24159-037

Figure 36. CSSI Receive Timing with 4× Data Clock Rate for 16-Bit Data Symbol (MSB First)

RX_CLOCK_OUT

RX_STROBE_OUT

OR

RX_STROBE_OUT

RX_DATA_OUT

16 CYCLES (I SAMPLE) 112 CYCLES (NO SAMPLE)

I0_D15 I0_D14 I0_D8 I0_D7 I0_D6 I0_D0 I0_D14I1_D15

24159-038

Figure 37. Receive CSSI Timing with 8× Data Clock Rate for 16-Bit Data Symbol (MSB First)

Four-Lane Mode CSSI Interface

The four-lane mode receive CSSI interface of each channel (Rx1 and Rx2) are a 6-wire digital interface consisting of:

• RX_DCLK_OUT: is an output clock synchronous data and strobe output signals.

• RX_STROBE_OUT: is an output signal indicating the first bit of the serial data sample.

• RX_IDATA0_OUT: is an output serial data stream of I sample low byte.

• RX_IDATA1_OUT: is an output serial data stream of I sample high byte.

• RX_QDATA2_OUT: is an output serial data stream of Q sample low byte.

• RX_QDATA3_OUT: is an output serial data stream of Q sample high byte.

Loading...

Loading...