Preliminary Technical Data UG-1828

Rev. PrB | Page 221 of 277

Table 99. DEV_CLK_IN Phase Noise Requirements for LMR Type Applications

Frequency Offset From Carrier PLL Loop Bandwidth Optimized for LMR Type Applications, 38.4 MHz (dBc/Hz)

100 Hz −106

1000 Hz −151

10 kHz −151

100 kHz −151

10 MHz −151

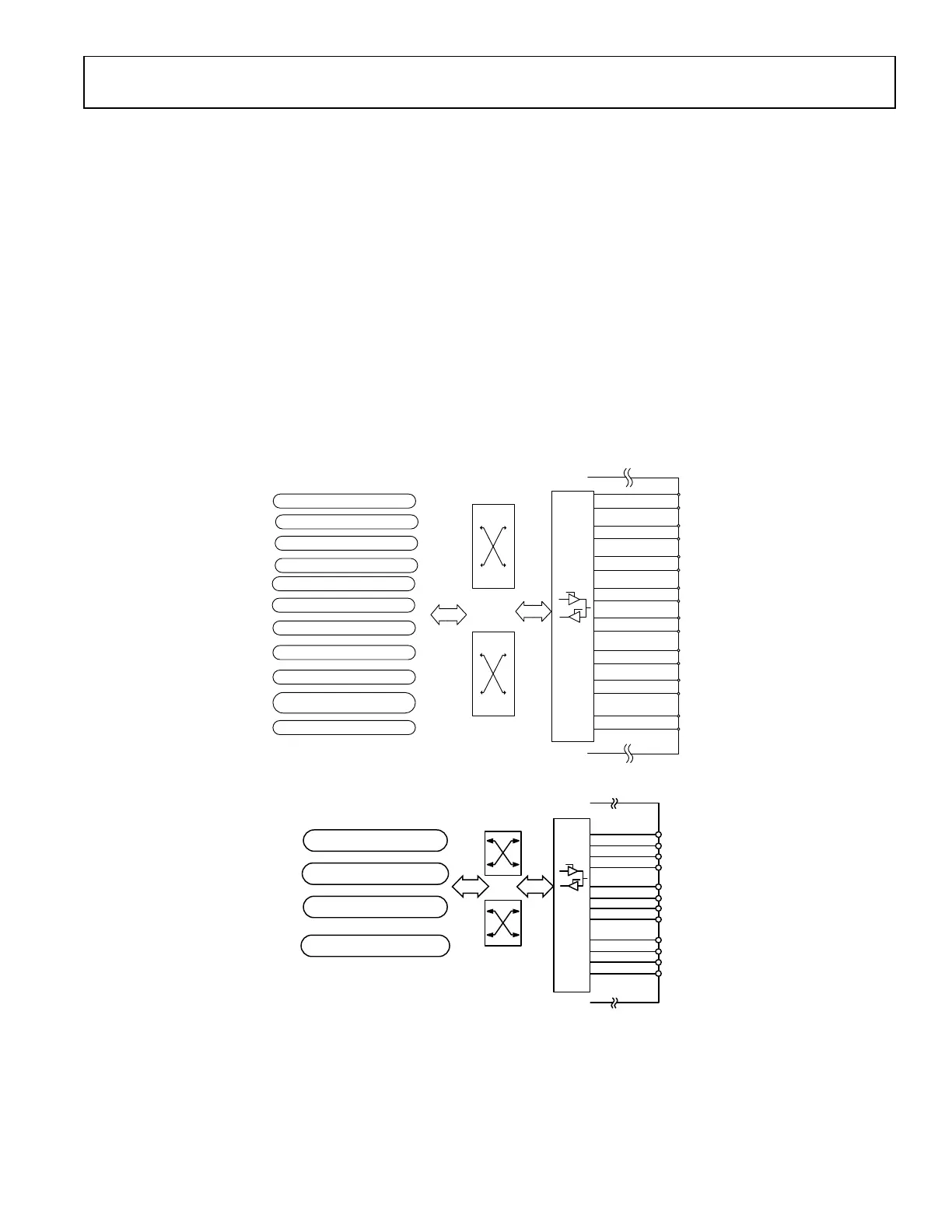

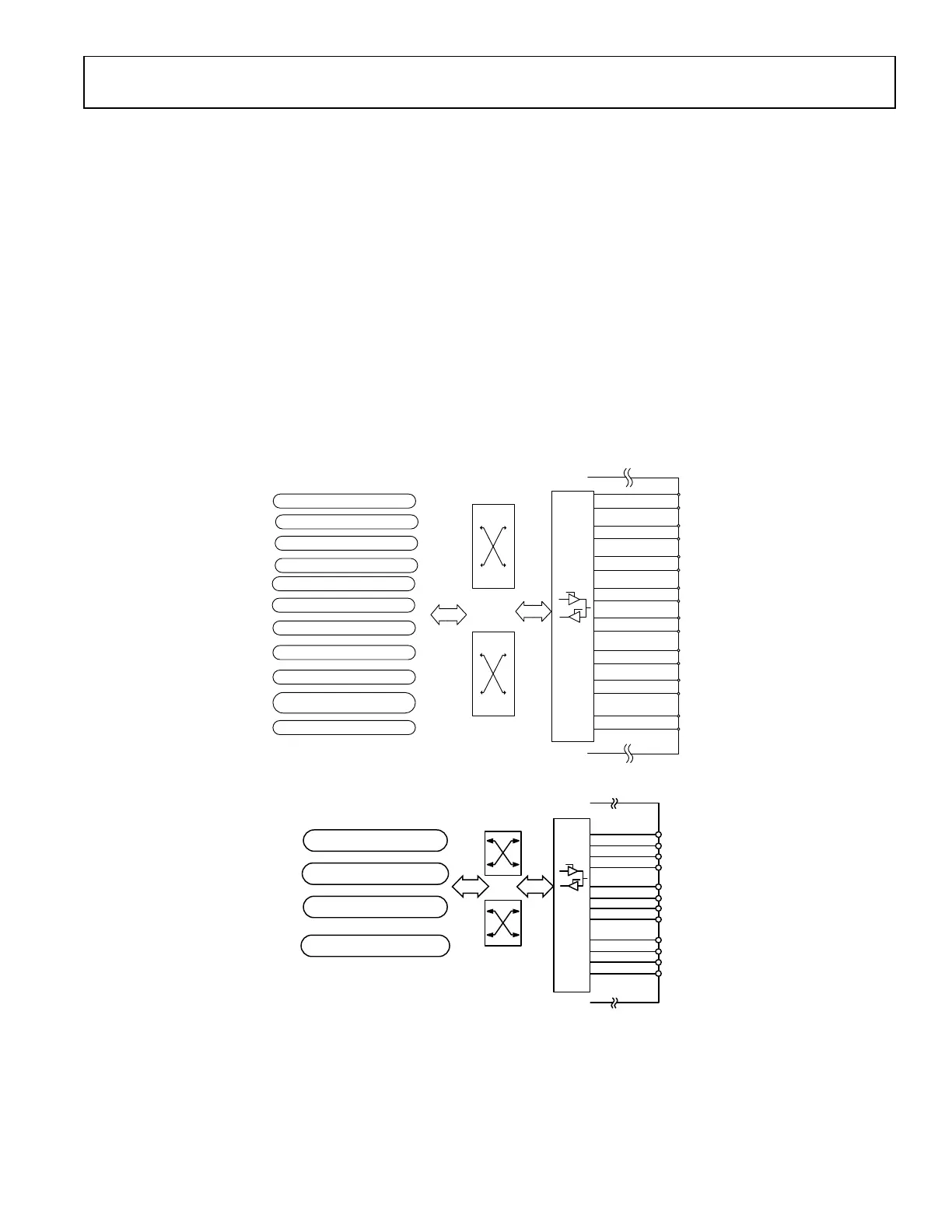

CONNECTION FOR MULTICHIP SYNCHRONIZATION (MCS) INPUT

A LVDS type MCS signal applied between MCS+(D7) and MCS-(D8) pins is used to provide time alignment synchronization for the

both RF and datalink systems. Similar to device clock input signal, a clock source with fast rise and fall times should be used as MCS

input signal. PCB traces for routing MCS signals should be implemented following guidelines that are similar to LVDS mode device

clock input trace.

Loading...

Loading...