UG-1828 Preliminary Technical Data

Rev. PrB | Page 26 of 277

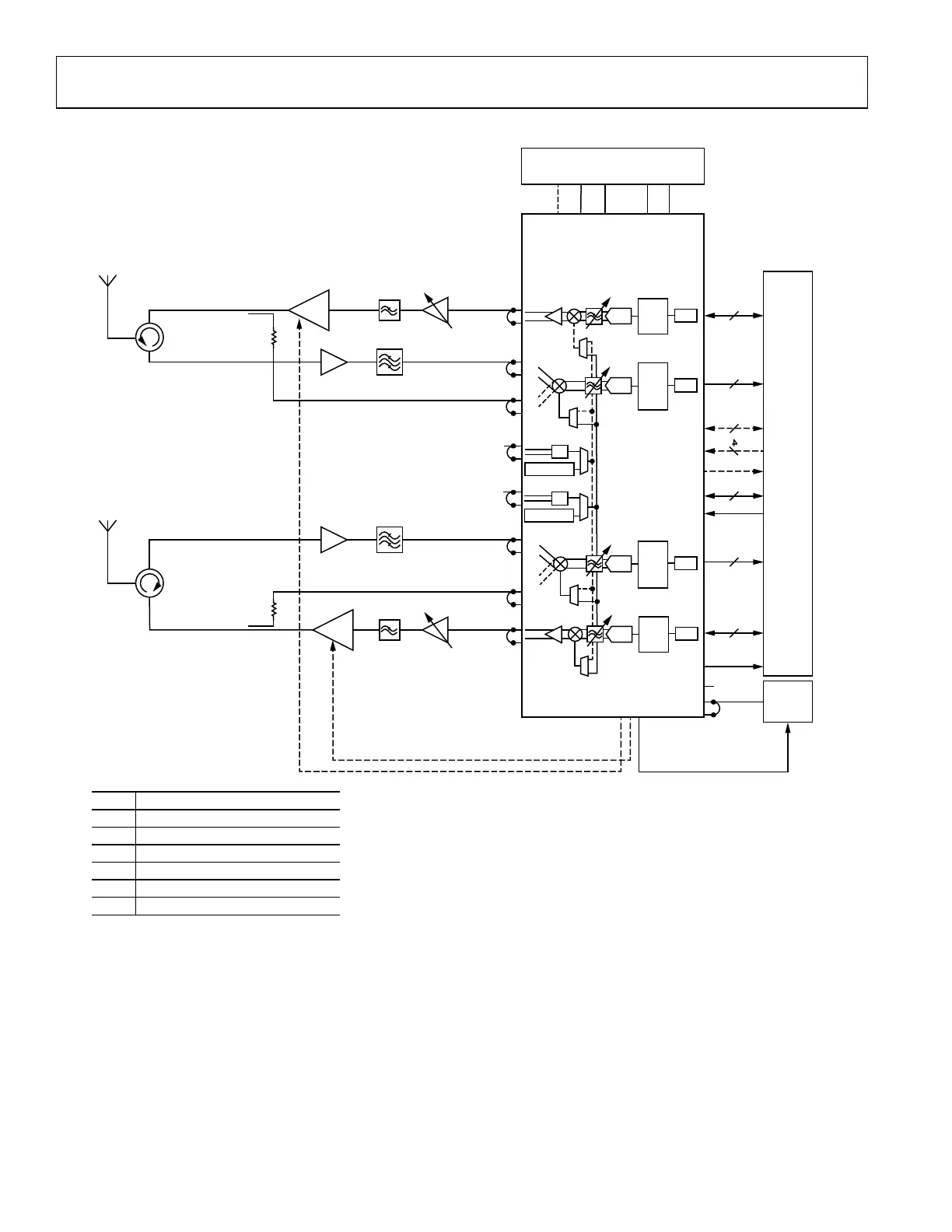

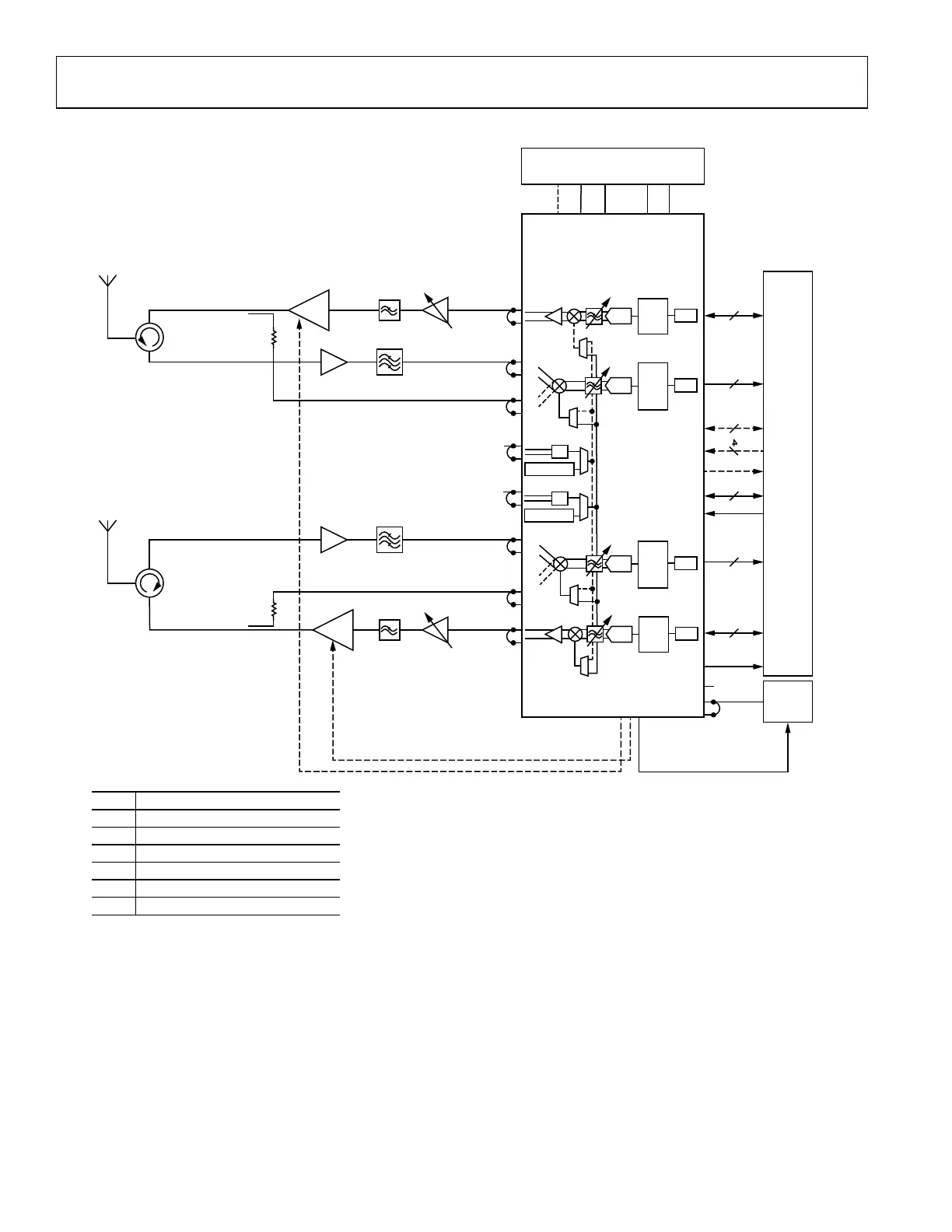

ADRV9001 IN TDD TYPE REPEATER APPLICATION

SPI

RESET

DEV_CLKL_OUT

MCS

DEV_CLK

DGPIOs

Rx/Tx_ENABLE

GP_INT

BPF FILTER

LNA

ATTENUATOR

COUPLER

ANTENNA A

VCXO

BALUN

BALUN

BALUN

BALUN

BALUN

POWER IC

BALUN

BALUN

/2

SSI

DAC

BALUN

BALUN

VGA

PA

LPF

FUNCTIONALITY

RECEPTION FROM ANTENNA A

USED BY Tx1 DPD AND CALIBRATIONS

RECEPTION FROM ANTENNA B

USED BY Tx2 DPD AND CALIBRATIONS

TRANSMISSION ON ANTENNA A

TRANSMISSION ON ANTENNA B

RF I/O

Rx1A

Rx1B

Rx2A

Rx2B

Tx1

Tx2

ADRV9001

FPGA

OR

BBIC

VDDA_1P0

VDDA_1P3

VDDA_1P8

VDD_1P0

VDD_1P8

RF PLL2

RF PLL1

/2

EXT LO2

EXT LO1

Tx1

Rx1A

Rx1B

Rx2A

Rx2B

Tx2

INT

QEC

LOL

Tx1

DATA

ADC

DDC

DEC

QEC

DC

SSI

Rx1

DATA

ADC

DDC

DEC

QEC

DC

SSI

Rx2

DATA

SSI

DAC

INT

QEC

LOL

Tx2

DATA

AuxDACAuxADCAGPIOs

3/4/6/7/8/10

3/6/8

12/16

3/4

3/6/8

3/4/6/7/8/10

BPF FILTER

LNA

ATTENUATOR

COUPLER

ANTENNA B

PA

LPF

VGA

CIRCULATOR

CIRCULATOR

24159-01

1

Figure 11. ADRV9001 in TDD Type Repeater Application with Baseband Processor Analyzing Traffic Data

TDD Type Repeater Overview

With a minimum number of external components, the ADRV9001 transceiver can be used to build complete RF-to-bits signal chain that

can serve as RF front end in TDD type repeater or frequency translator applications. In TDD type applications, internal DPD block can

be used to linearize external power amplifier and improve overall system efficiency. ADRV9001 internal AGC can be used to

autonomously monitor and set appropriate gain level for Rx signal chains. FPGA or baseband processor is responsible for appropriate

time alignment of Rx and Tx time slots. Control of the ADRV9001 Rx and Tx signal chains can be done by toggling control lines.

ADRV9001 can provide power amplifier bias voltage by utilizing AuxDAC outputs.

Loading...

Loading...