Preliminary Technical Data UG-1828

Rev. PrB | Page 191 of 277

GENERAL-PURPOSE INPUT/OUTPUT AND INTERRUPT CONFIGURATION

ADRV9001 provides user with number of software configurable General-Purpose Input/Output (GPIO) pins. By utilizing API functions,

user can configure GPIO pins to operate with a variety of control or monitoring functions. ADRV9001 has two types of GPIO:

• 16 digital GPIO pins

• referenced to VIOCTRL_1P8 supply

• designated DGPIO_0 through DGPIO_15

• 12 analog GPIO pins

• referenced to VAGPIO_1P8 supply

• designated AGPIO_0 through AGPIO_11

The Digital and Analog GPIO pins can be used as real-time status signals that provide device status information from ADRV9001 to the

baseband processor when the GPIO pins are configured as outputs, with respect to ADRV9001. When set as inputs, the GPIO pins can

be used as real-time control signals that can alter the device state. The API functions related to GPIO configuration give the user the

ability to configure pins as inputs or outputs and assign functionality to specific pins.

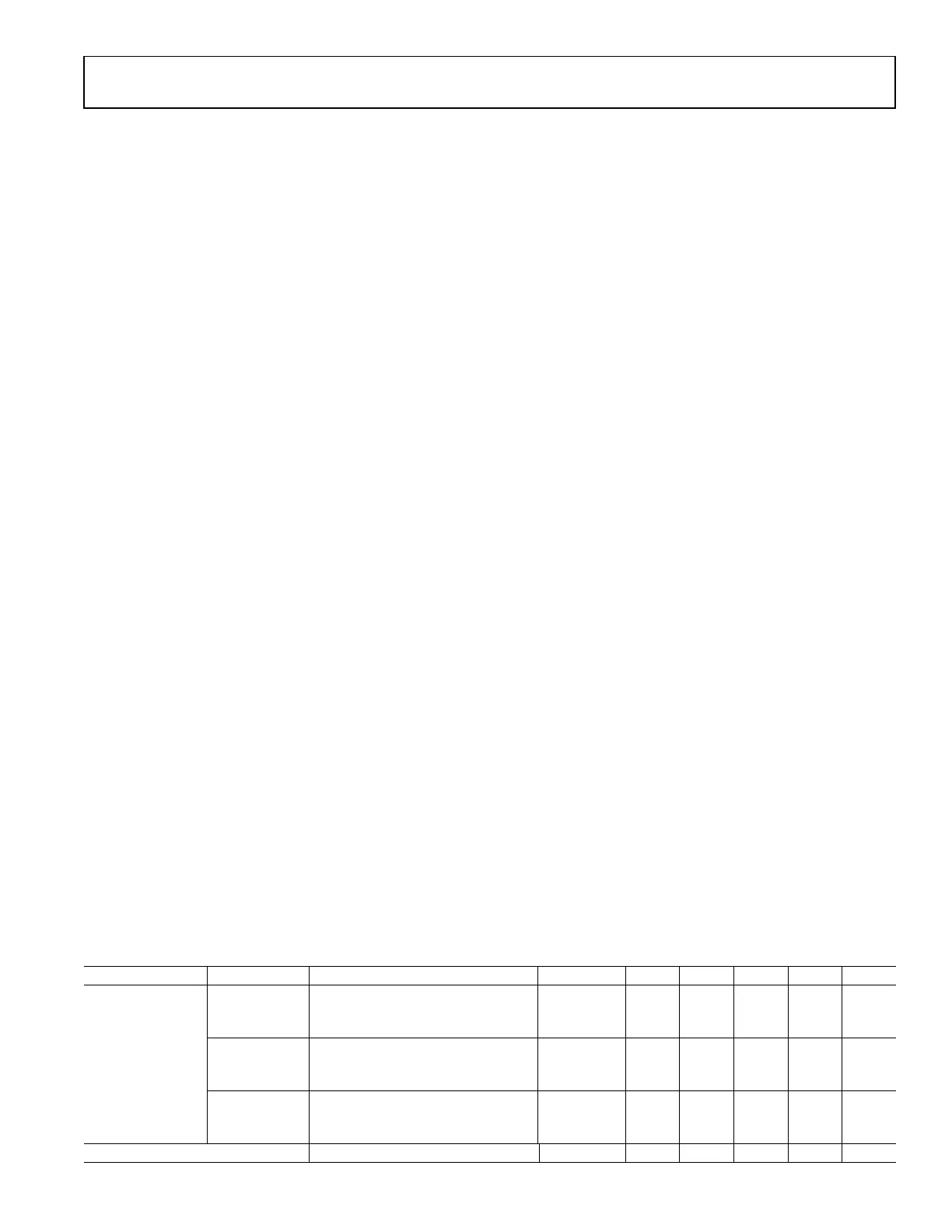

Figure 183, Figure 184 illustrates the different functionalities that can be enabled in the device and then controlled using the Digital

GPIO pins and Analog GPIO pins, not all functionalities can be enabled at the same time.

DGPIO 15

DGPIO 14

DGPIO 13

DGPIO 12

DGPIO 11

DGPIO 10

DGPIO 9

DGPIO 8

DGPIO 7

DGPIO 6

DGPIO 5

DGPIO 4

DGPIO 3

DGPIO 2

DGPIO 1

DGPIO 0

MANUAL PIN TOGGLE

I/O

BUFFER

I/O

CROSS

Tx SSI REFERENCE CLOCK OUTPUT

MONITOR WAKEUP IRQ

CONTROL OUTPUT

ORx ENABLE CONTROL

Rx GAIN CONTROL

Tx ATTENUATION CONTROL

PA RAMP CONTROL

MONITOR MODE CONTROL

HOPPING MODE CONTROL

AGC OVERLOAD INDICATOR

24159-156

Figure 184. Digital GPIO Features Overview

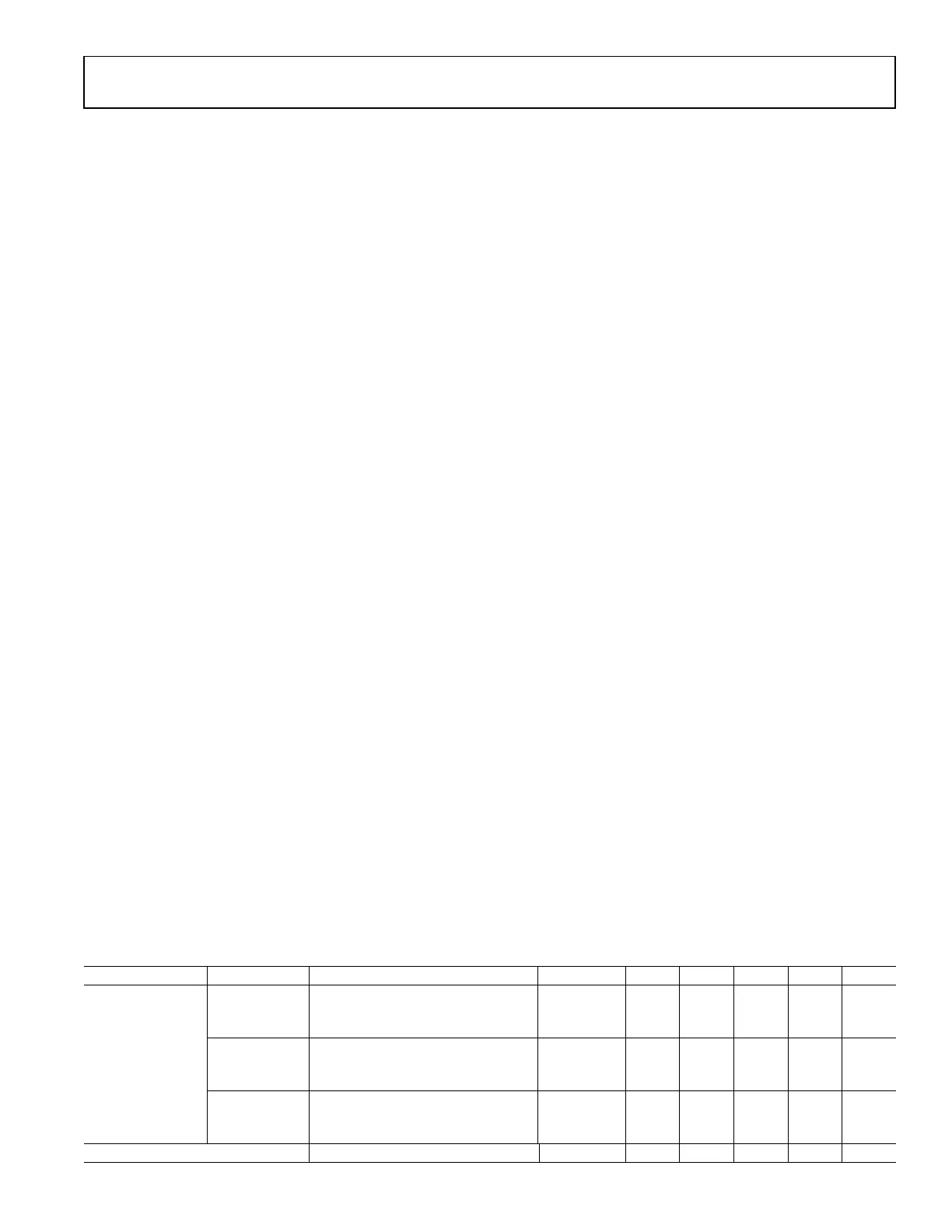

I/O

BUFFER

I/O

CROSS

AGPIO 11

AGPIO 10

AGPIO 9

AGPIO 8

AGPIO 7

AGPIO 6

AGPIO 5

AGPIO 4

AGPIO 3

AGPIO 2

AGPIO 1

AGPIO 0

Rx EXTERNAL GAIN CONTROL

RF FRONT END CONTROL

MANUAL PIN TOGGLE

AUXDAC

24159-157

Figure 185. Analog GPIO Feature Overview

In configuring the GPIO, the two major factors to consider are the GPIO output enable control and the GPIO source control.

The output enable determines the direction of the pin, if a pin is set as output, then the GPIO I/O buffer is configured as an output. The

GPIO CMOS output drive strength can be increased for capacitive loads bigger than 10 pF to increase the edge rate of output signal

during transitional period.

The GPIO source control determines the functionality of the pin. The Digital GPIO source control is assigned in groups of 2, this means

that DGPIO_0 to DGPIO_1 share a single source control, DGPIO_2 to DGPIO_3 share a single source control, and so on The Analog

GPIO source control is assigned in groups of 4, that means that AGPIO_0 to AGPIO_3 share a single source control, AGPIO_4 to

DGPIO_7 share a single source control, and so on

Loading...

Loading...