UG-1828 Preliminary Technical Data

Rev. PrB | Page 66 of 277

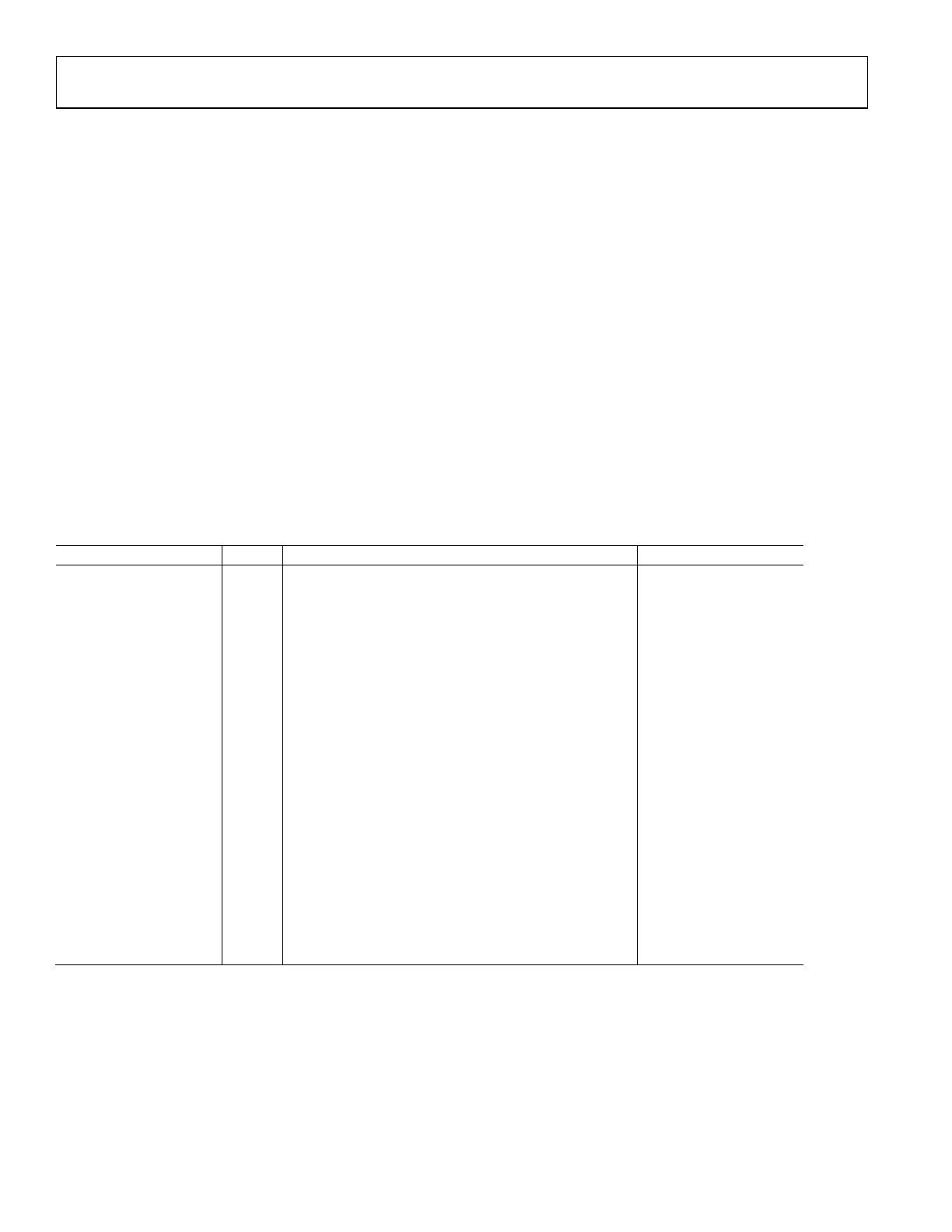

Delay Description

Provided

By

Bounds Comments

propagationDelay

(t

RxPD

)

Propagation delay from

antenna to Rx interface.

Helper

Parameter

Min: N/A

Max: N/A

This parameter should be measured

by user and it is profile dependent

and board layout dependent. It

does not need to provide to

ADRV9001, however, it can be used

to derive values for other

parameters required by ADRV9001.

enableRiseToAnalogOnDelay

(t

RxEnaRise2AnaOn

)

Delay between RX_ENABLE

rising edge to start of Rx

analog power up.

User

Parameter

Min: 0

Max: duration of power

up tasks in power

savings or frequency

hopping modes.

Will only be set to non-zero values if

using power savings or frequency

hopping. See later sections to

determine how to choose a non-

zero value.

enableRiseToOnDelay

(t

RxEnaRise2On

)

Delay between RX_ENABLE

rising edge and LNA power

up.

If ADRV9001 does not

controlling LNA power, this

parameter is not needed.

User

Parameter

Min: t

RxEnaRise2AnaOn

Typ: t

RxEnaRise2AnaOn

+

t

RxEnaSetup

Max: None. Must be

optimized to be

minimal.

If set to t

RxEnaRise2AnaOn

, the actual

delay is t

RxEnaRise2AnaOn

+ t

RxEnaSetup

.

enableGuardDelay

(t

RxGT

)

Guard time of the Rx frame.

Reserved for future use.

Should set to 0 currently.

User

Parameter

Min: TBD

Max: TBD

TBD

enableFallToOffDelay

(t

RxEnaFall2Off

)

Delay between RX_ENABLE

falling edge and the

powering down the LNA.

(If ADRV9001 not

controlling LNA power, this

parameter can still be used

to delay analog power

down. ADRV9001 forces it

to 0 currently. LNA is

disabled at the same time

when Rx is disabled.)

User

Parameter

Min: 0

Max: None. Must be

optimized to be

minimal.

Ideally, RX_ENABLE falling edge

arrives when the last valid data is

received over the air. By setting this

value greater than 0, ADRV9001 can

continue receiving guard symbols,

while signaling to certain

algorithms or other systems that

the valid data for the frame has

already been received.

enableHoldDelay

(t

RxEnaHold

)

Delay between RX_ENABLE

falling edge and masking

off datapath data sent over

interface.

User

Parameter

Min: t

RxEnaFall2Off

Max: None. Must be

optimized to be

minimal.

(Recommended Max:

t

RxEnaFall2Off

+ t

RxPD

Note

t

RxEnaFall2Off

is forced to 0

currently.)

The interface is disabled only after

analog power down has completed.

@ min bound: Some of the data

received at the antenna may not

make it over the interface.

@ max bound: Digital datapath and

Rx SSI interface remains enabled

until last received data is

propagated to the interface.

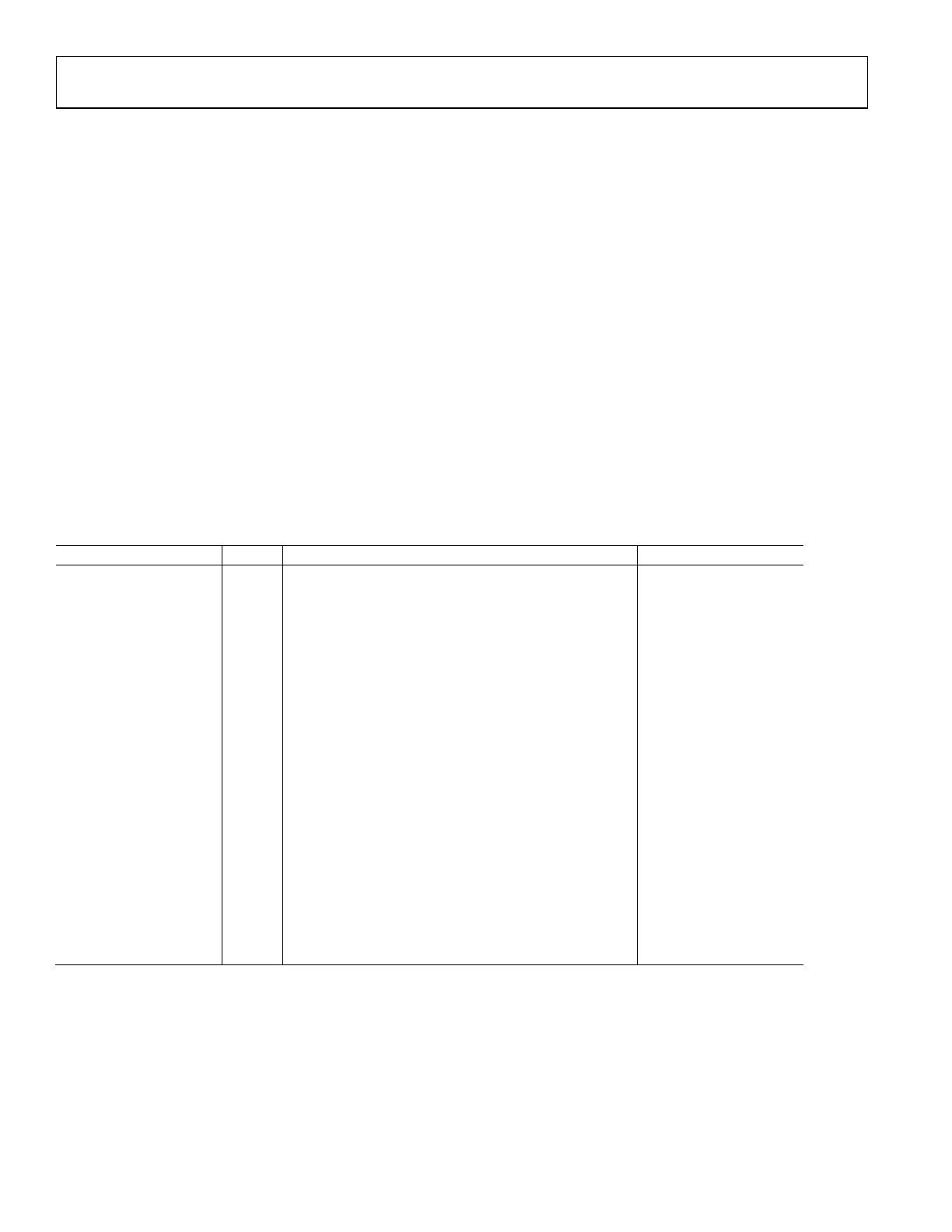

Design Strategy for Receive Timing Parameters

As described in Table 23, ADRV9001 provides user enableSetupDelay which is the time required to power up the receiver front end. By

knowing that, user could set the RX_ENABLE pin high at least enableRiseToOnDelay in advance as shown in Figure 56. In regular TDD

mode, that is, no power savings or frequency hopping, enableRiseToAnalogOnDelay should always be set to 0, so that analog power up

begins immediately after receive enable rising edge (Note Figure 56 describes receive timing parameters in a general case with

enableRiseToAnalogOnDelay not equal to 0.). The parameter enableRiseToOnDelay could also be set to 0, in this case, the LNA is

powered up as soon as analog power up completes. For a more deterministic delay between RX_ENABLE rising edge and LNA power up

time, enableRiseToOnDelay can be set to a value greater than or equal to

enableRiseToAnalogOnDelay + enableSetupDelay

Once timing on air is established, the user may choose to raise RX_ENABLE, sometime before the start of the actual frame. As soon as

the Rx analog power up completes, the digital interface turns on, however, if the path has a long propagation delay, the initial data

coming off the interface are not the data received over the air.

When the frame ends, users may wish to continue receiving for a while, however, ADRV9001 may wish to stop all the tracking

algorithms to avoid any performance degradation. This can be achieved by bringing the RX_ENABLE signal low as soon as the frame

Loading...

Loading...