UG-1828 Preliminary Technical Data

Rev. PrB | Page 76 of 277

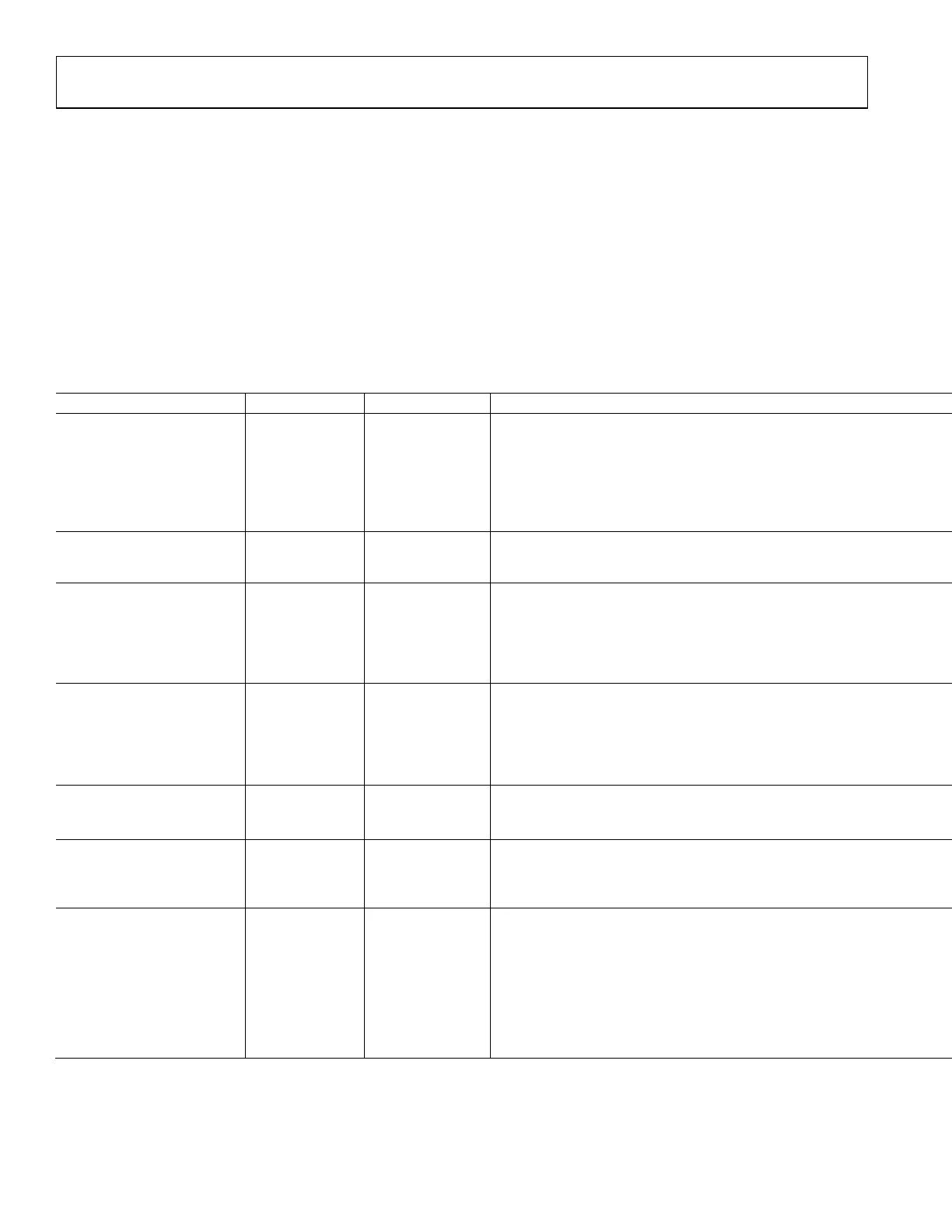

Table 29. Supported Data Lane Rate By LP CLKPLL

Standard Serialization Factor Per Data Lane Data Lane Rate

DMR/P25 Direct Modulation 2 9.60E +03

P25 Direct Modulation 2 1.20E +04

FM Direct Modulation 16 1.28E +05

DMR I/Q 32 7.68E + 05

8 1.92E + 05

16 3.84E + 05

FM Direct Modulation 16 1.54E + 06

TETRA 32 4.61E + 06

8 1.15E + 06

16 2.30E + 06

TETRA 32 9.22E + 06

8 2.30E + 06

16 4.61E + 06

LTE 1.5 32 6.14E + 07

8 1.54E + 07

16 3.07E + 07

LTE 3 8 3.07E + 07

16 6.14E + 07

LTE 5 8 6.14E + 07

16 1.23E + 08

LTE 10 16 2.46E + 08

LTE 15 16 3.69E + 08

LTE 20 16 4.92E + 08

LTE 40 @12 bits 12 7.37E +08

Arbitrary Sample Rate

With a programmable frequency range of both HP CLK PLL and LP CLK PLL as mentioned previously, ADRV9001 supports arbitrary

sample rate (ASR) mode, which provides user a great flexibility to configure the desired sample rates in their applications. ASR mode

supports an almost continuous range of rates from 24 kHz to 61.44 MHz with a list of dead zones due to CLK PLL limitations. The

following table summarizes the current dead zone frequency ranges:

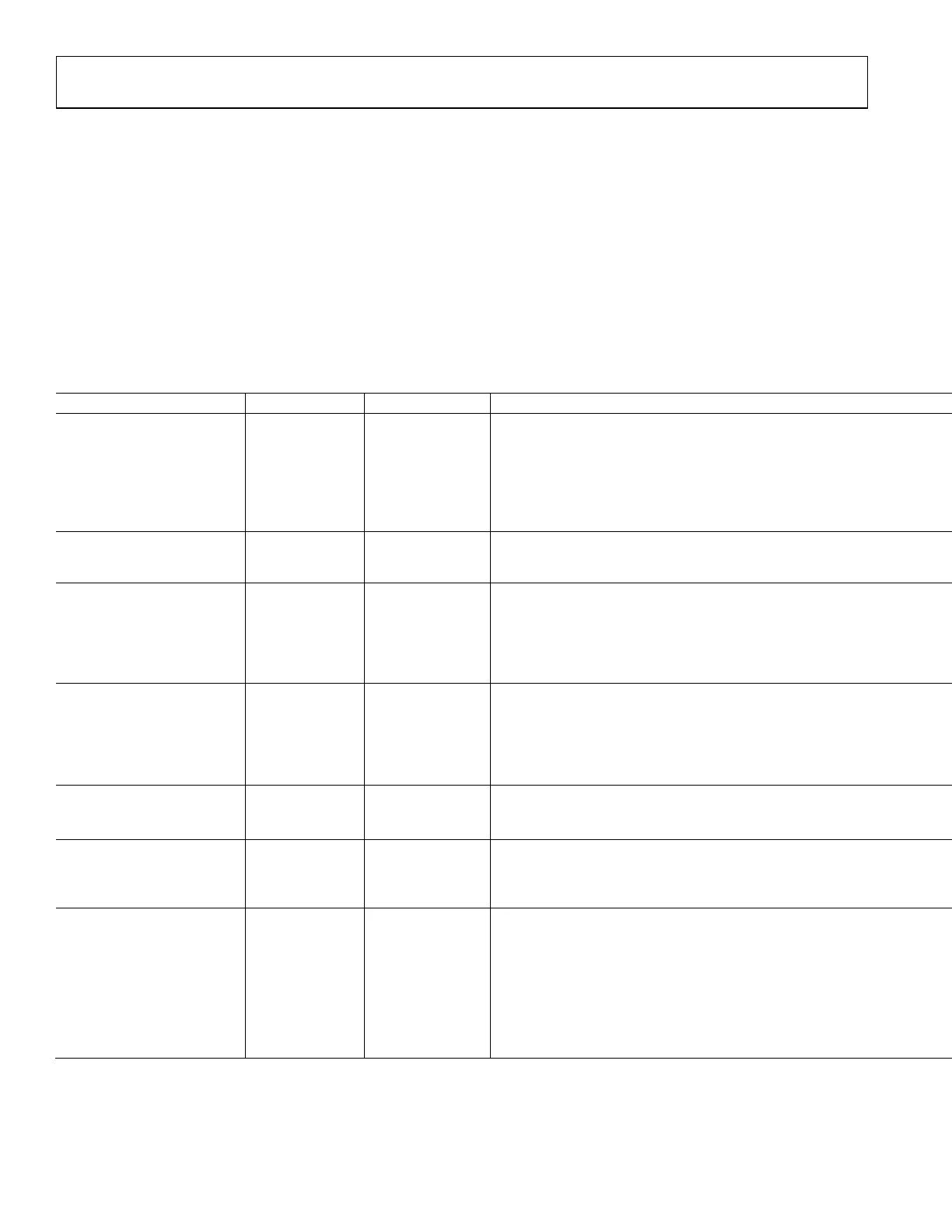

Table 30. Dead Zone Frequency Ranges

Dead Zone (CLK PLL Limitation) Lower Bound (MHz) Upper Bound

1 50 160/3

2 100/3 40

3 25 80/3

4 50/3 20

5 12.5 40/3

6 25/3 10

7 6.25 20/3

8 25/6 5

9 3.125 10/3

10 25/12 2.5

11 1.5625 5/3

12 25/24 1.25

Note that there are a total of 12 different dead zones. For each one, the sample rates user cannot configure are between the lower bound

and upper bound with lower bound frequency and upper bound frequency excluded, which means dead zone = (lower bound, upper

bound).

When sample rate is greater than 160/3 MHz, HP CLK PLL should always be used. Due to the complexity of data path, user does not

have the freedom to select their own CLK PLL clock frequencies and datapath configurations. The user should only provide their desired

sample rate, and the API will determine the appropriate ADRV9001 profile.

Loading...

Loading...