GR740-UM-DS, Nov 2017, Version 1.7 175 www.cobham.com/gaisler

GR740

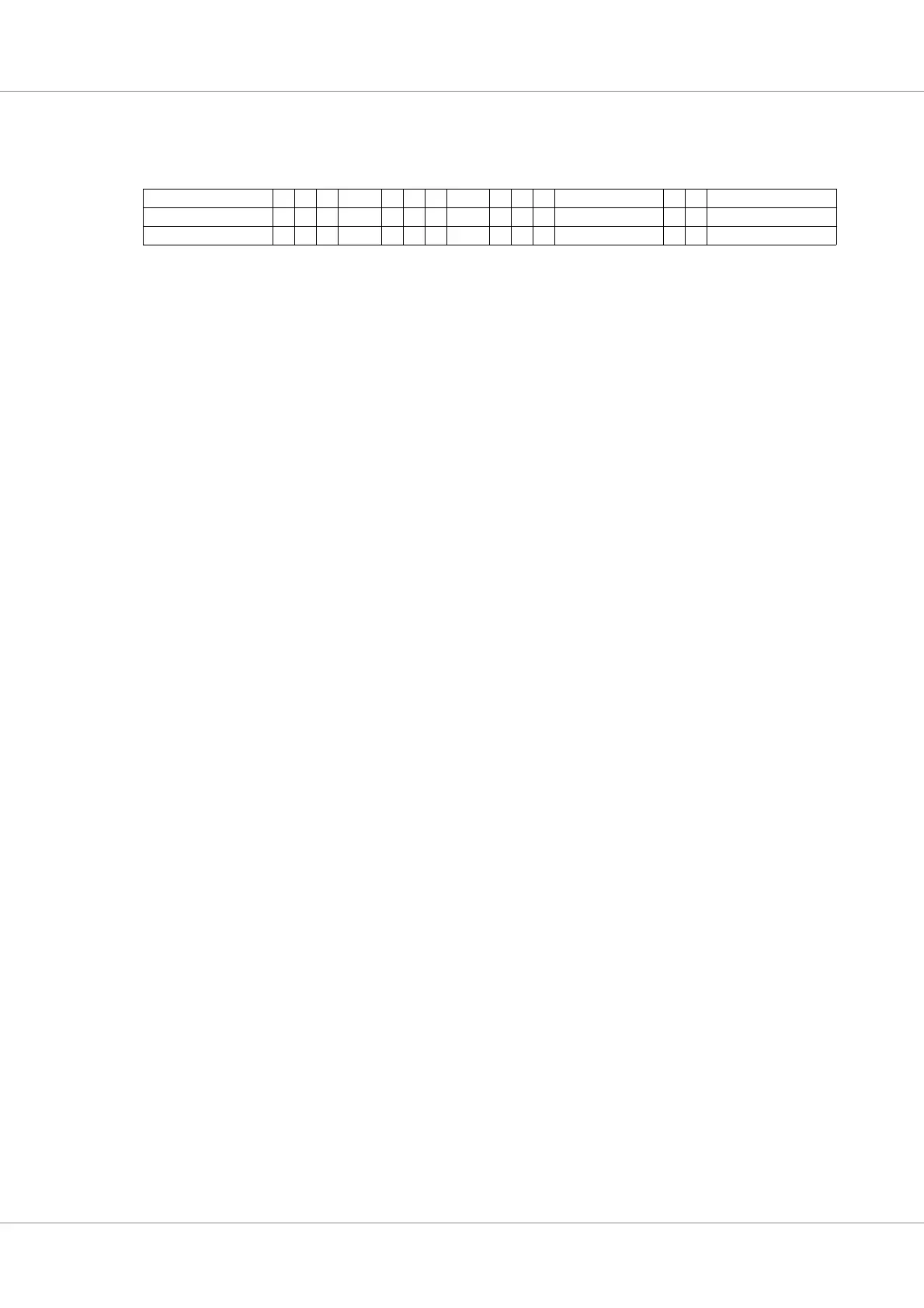

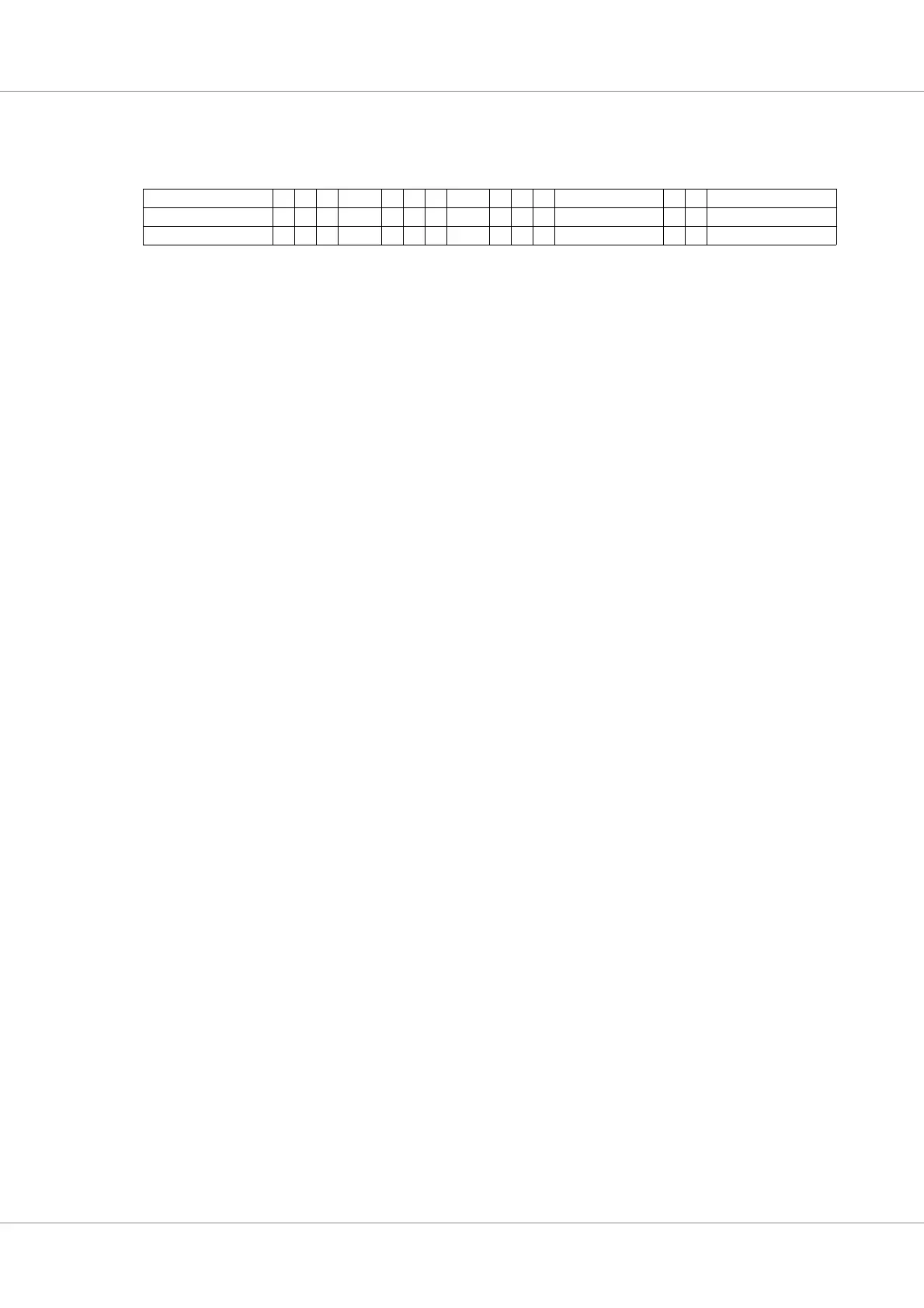

Table 165. 0xA0 - RTR.AMBAINTCTRL - AMBA port Distributed interrupt control

31 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 8 7 6 5 0

INTNUM R EE IA RES TQ AQ IQ RES AA AT IT RESERVED ID II TXINT

0x00 0 0 0 0x0 0 0 0 0x0 0 1 1 0x00 0 0 0x00

rw r rw rw r rw rw rw r rw rw rw r wc rw* rw

31: 26 Interrupt number (INTNUM) - The interrupt-number used when sending an interrupt code that was gener-

ated due to any of the events maskable by the RTR.AMBAINCTRL.ER and RTR.AMBAINTCTRL.IA bits.

Note that when RTR.RTRCFG.EE = 0 (interrupt with acknowledgement mode), this field must no be set to a

value greater than 31.

25 RESERVED

24 Interrupt transmit on early EOP/EEP (EE) - If set to 1, a distributed interrupt code with the interrupt number

specified in the RTR.AMBAINTCTRL.INTNUM field is sent each time an event occurs such that the

STS.EE bit is set to 1 (even if the bit was already set when the event occurred).

23 Interrupt transmit on invalid address (IA) - If set to 1, a distributed interrupt code with the interrupt number

specified in the RTR.AMBAINTCTRL.INTNUM field is sent each time an event occurs such that the

STS.IA bit is set to 1 (even if the bit was already set when the event occurred).

22: 21 RESERVED

20 Interrupt timeout IRQ enable (TQ) - When set to 1, an AMBA interrupt is generated when a bit in the

RTR.AMBAINTTO0 or RTR.AMBAINTTO1 registers is set. Note that the RTR.AMBACTRL.IE bit also

must be set for this bit to have any effect.

19 Interrupt acknowledgment / extended interrupt receive IRQ enable (AQ) - When set to 1, an AMBA inter-

rupt is generated when an interrupt acknowledgment code or extended interrupt code is received such that a

bit in the RTR.AMBAACKRX register is set to 1 (even if the bit was already set when the code was

received).

18 Interrupt-code receive IRQ enable (IQ) - When set to 1, an AMBA interrupt is generated when an interrupt

code is received such that a bit in the RTR.AMBAINTRX register is set to 1 (even if the bit was already set

when the code was received).

17: 16 RESERVED

15 Handle all interrupt acknowledgment codes (AA) - Is set to 0, only those received interrupt acknowledgment

codes that match an interrupt code sent by software are handled. If set to 1, all received interrupt acknowl-

edgment codes are handled.

14 Interrupt acknowledgment / extended interrupt tickout enable (AT) - When set to 1, the internal tickout sig-

nal from this AMBA port is set when an interrupt acknowledgment code or extended interrupt code is

received such that a bit in the RTR.AMBAACKRX register is set to 1 (even if the bit was already set when

the code was received). The internal tickout signal is connected to the timer units as described in section 5.9

and in the LATCHCFG register description in section 20.3.

13 Interrupt tickout enable (IT) - When set to 1, the internal tickout signal from this AMBA port is set when an

interrupt code is received such that a bit in the RTR.AMBAINTRX register is set to 1 (even if the bit was

already set when the code was received). The internal tickout signal is connected to the timer units as

described in section 5.9 and in the LATCHCFG register description in section 20.3.

12: 8 RESERVED

7 Interrupt discarded (ID) - This bit is set to 1 when a distributed interrupt code that software tried to send by

writing the RTR.AMBAINTCTRL.II bit was discarded by the routers switch matrix. There is a maximum of

ten clock cycle delay between the RTR.AMBAINTCTRL.II bit being written and this bit being set.

6 Interrupt-code tick-in (II) - When this field is written to 1 the distributed interrupt code specified by the

RTR.AMBAINTCTRL.TXINT field will be sent out from the AMBA port to the routers switch matrix. This

bit is automatically cleared and always reads ‘0’. Writing a ‘0’ has no effect.

5: 0 Transmit distributed interrupt code (TXINT) - The distributed interrupt code that will be sent when the reg-

ister RTR.AMBAINTCTRL.II is written with 1.

Loading...

Loading...