GR740-UM-DS, Nov 2017, Version 1.7 86 www.cobham.com/gaisler

GR740

9 Level 2 Cache controller

9.1 Overview

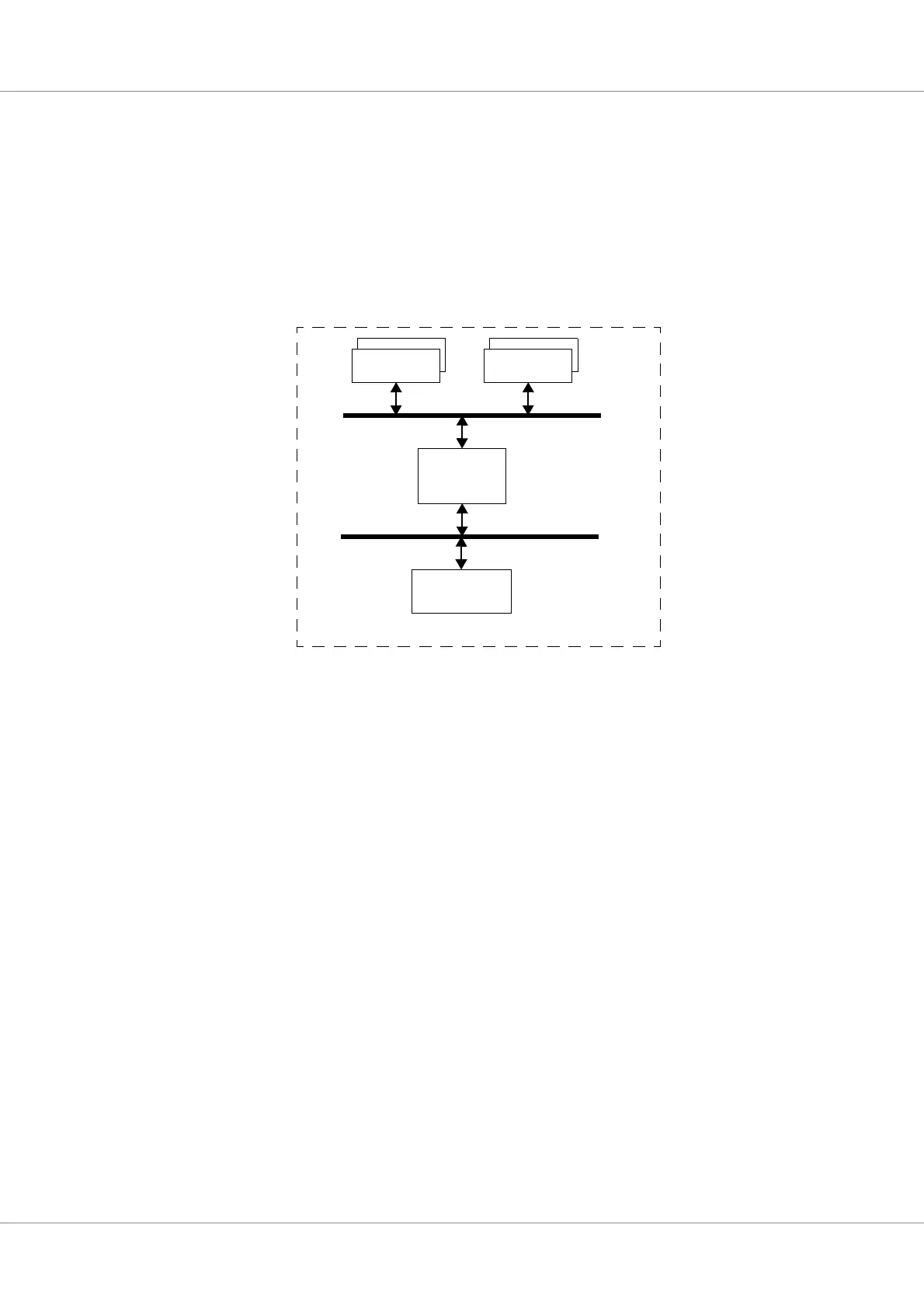

The L2 cache works as an AHB to AHB bridge, caching the data that is read or written via the bridge.

The cache is a unified cache and data may exist in both the processor Level-1 caches and the Level-2

cache, or only in a Level-1 or the Level-2 cache. A front-side AHB interface is connected to the Pro-

cessor AHB bus, while a backend AHB interface is connected to the Memory AHB bus. Figure 8

shows a system block diagram for the cache controller.

Note that the L2 cache is disabled after reset and should be enabled by boot software.

9.2 Operation

The Level-2 cache is implemented as a multi-way cache with an associativity of four. The replace-

ment policy can be configured as: LRU (least-recently-used), pseudo-random or master-index (where

the way to replace is determine by the master index). The way size is 512 KiB with a line size of 32

bytes.

9.2.1 Replacement policy

The cache supports three different replacement policies: LRU (least-recently-used), (pseudo-) random

and master-index. The reset value for replacement policy is LRU.

With the master-index replacement policy, master 0 would replace way 1, master 1 would replace way

2 and so on. For master indexes corresponding to a way number larger than the number of imple-

mented ways there are two options to determine which way to replace. One option is to map all these

master index to a specific way. This is done by specifying this way in the index-replace field in the

control register and selecting this option in the replacement policy field also located in the control reg-

ister. It is not allowed to select a locked way in the index-replace field. The second option is to replace

way = ((master index) modulus (number of ways)). This option can be selected in the replacement

policy field.

9.2.2 Write policy

The cache can be configured to operate as write-through or copy-back cache. Before changing the

write policy to write-through, the cache has to be disabled and flushed (to write back dirty cache lines

to memory). This can be done by setting the Cache disable bit when issue a flush all command. The

Figure 8. Block diagram

CPU

Memory

L2C

CPU

Controller

Memory AHB bus

Processor AHB bus

Loading...

Loading...