GR740-UM-DS, Nov 2017, Version 1.7 112 www.cobham.com/gaisler

GR740

11 Memory Scrubber and AHB Status Register

11.1 Overview

The memory scrubber monitors the Memory AHB bus for accesses triggering an AMBA ERROR

response, and for correctable errors signaled from fault tolerant memory controllers on the same bus.

The memory scrubber can be programmed to scrub a memory area by reading through the memory

and writing back the contents using a locked read-write cycle whenever a correctable error is detected.

It can also be programmed to initialize a memory area to known values.

The memory scrubber register interface is largely backward compatible with the AHB status register.

11.2 Operation

11.2.1 Errors

All AMBA AHB bus transactions are monitored and current HADDR, HWRITE, HMASTER and

HSIZE values are stored internally. When an error response (HRESP = “01”) is detected, an internal

counter is increased. When the counter exceeds a user-selected threshold, the status and address regis-

ter contents are frozen and the New Error (NE) bit is set to one. At the same time an interrupt is gen-

erated, as described hereunder.

The default threshold is zero and enabled on reset so the first error on the bus will generate an inter-

rupt.

The fault-tolerant memory controllers signal an un-correctable error as an AMBA error response, so

that it can be detected by the processor as described above.

11.2.2 Correctable errors

Not only AMBA ERROR responses on the AHB bus can be detected. The memory controllers on the

Memory AHB bus have a correctable error signal that is asserted each time a correctable error is

detected. When such an error is detected, the effect will be the same as for an AHB error response.

The only difference is that the Correctable Error (CE) bit in the status register is set to one when a cor-

rectable error is detected. Correctable and uncorrectable errors use separate counters and threshold

values.

When the CE bit is set, the interrupt routine can acquire the address containing the correctable error

from the failing address register and correct it. When it is finished it resets the CE bit and the monitor-

ing becomes active again. Interrupt handling is described in detail hereunder.

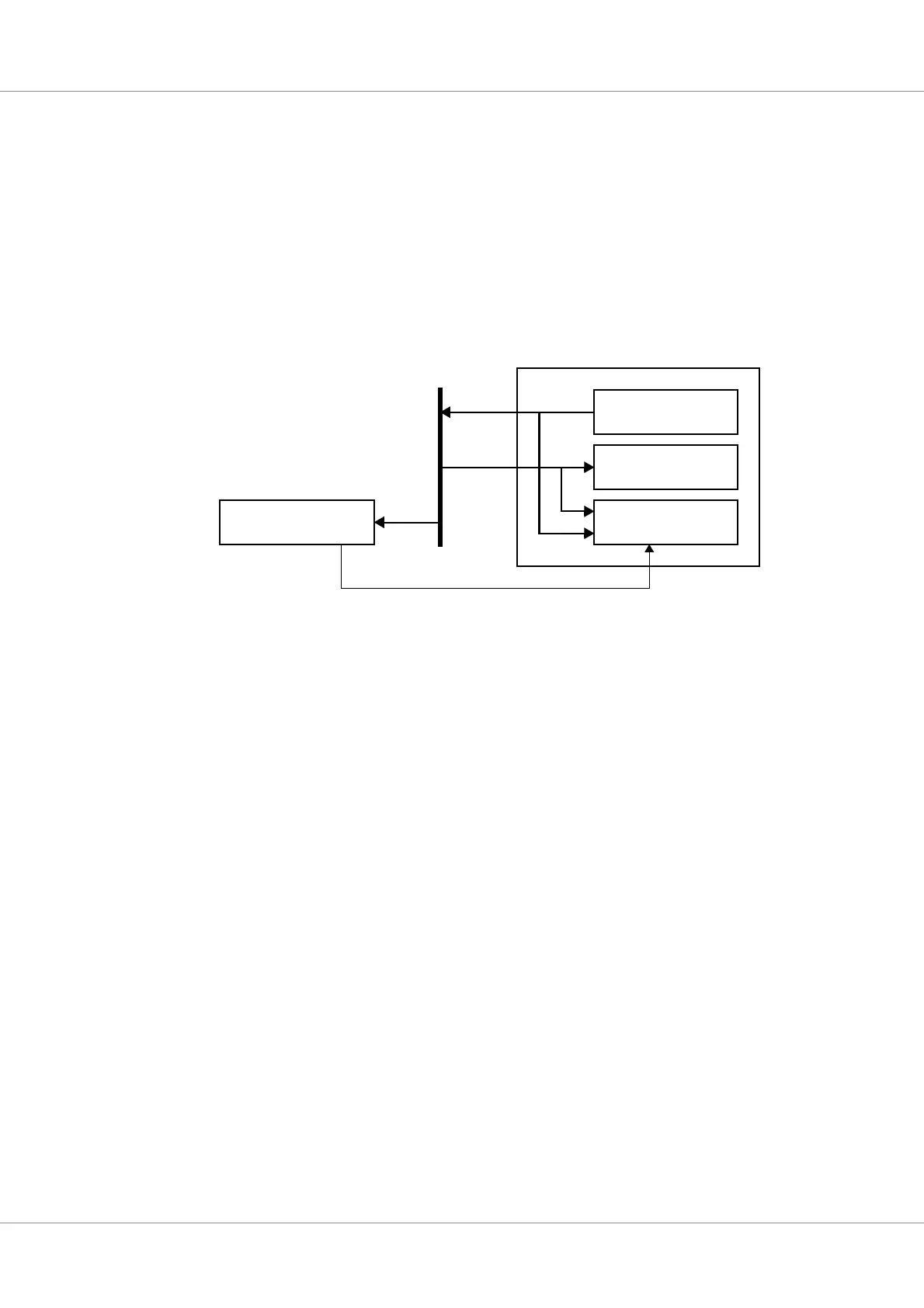

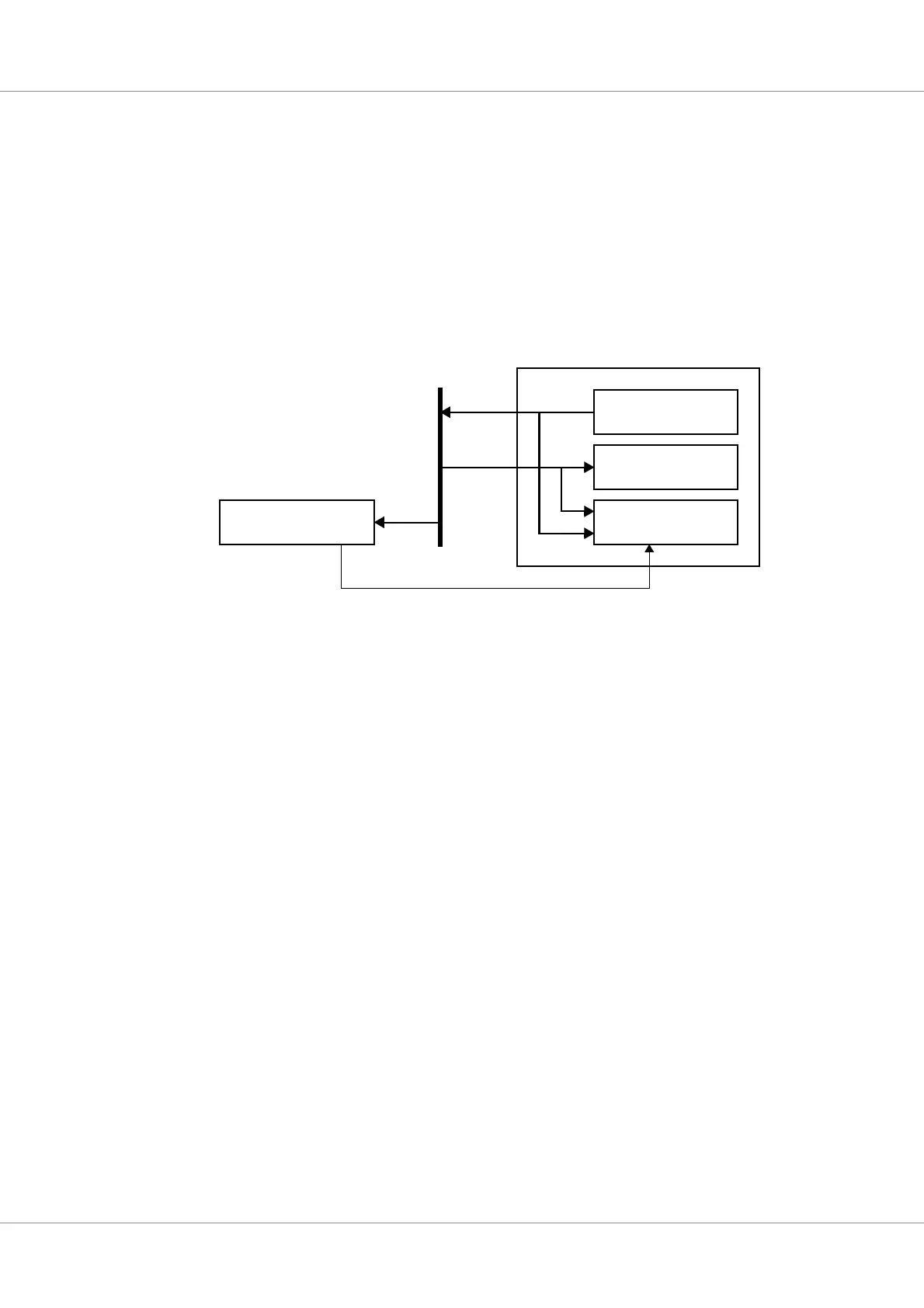

Scrubber DMA

Registers

AHB Error monitorMemory with EDAC

ce

AMBA AHB

Figure 10. Memory scrubber block diagram

Loading...

Loading...