GR740-UM-DS, Nov 2017, Version 1.7 61 www.cobham.com/gaisler

GR740

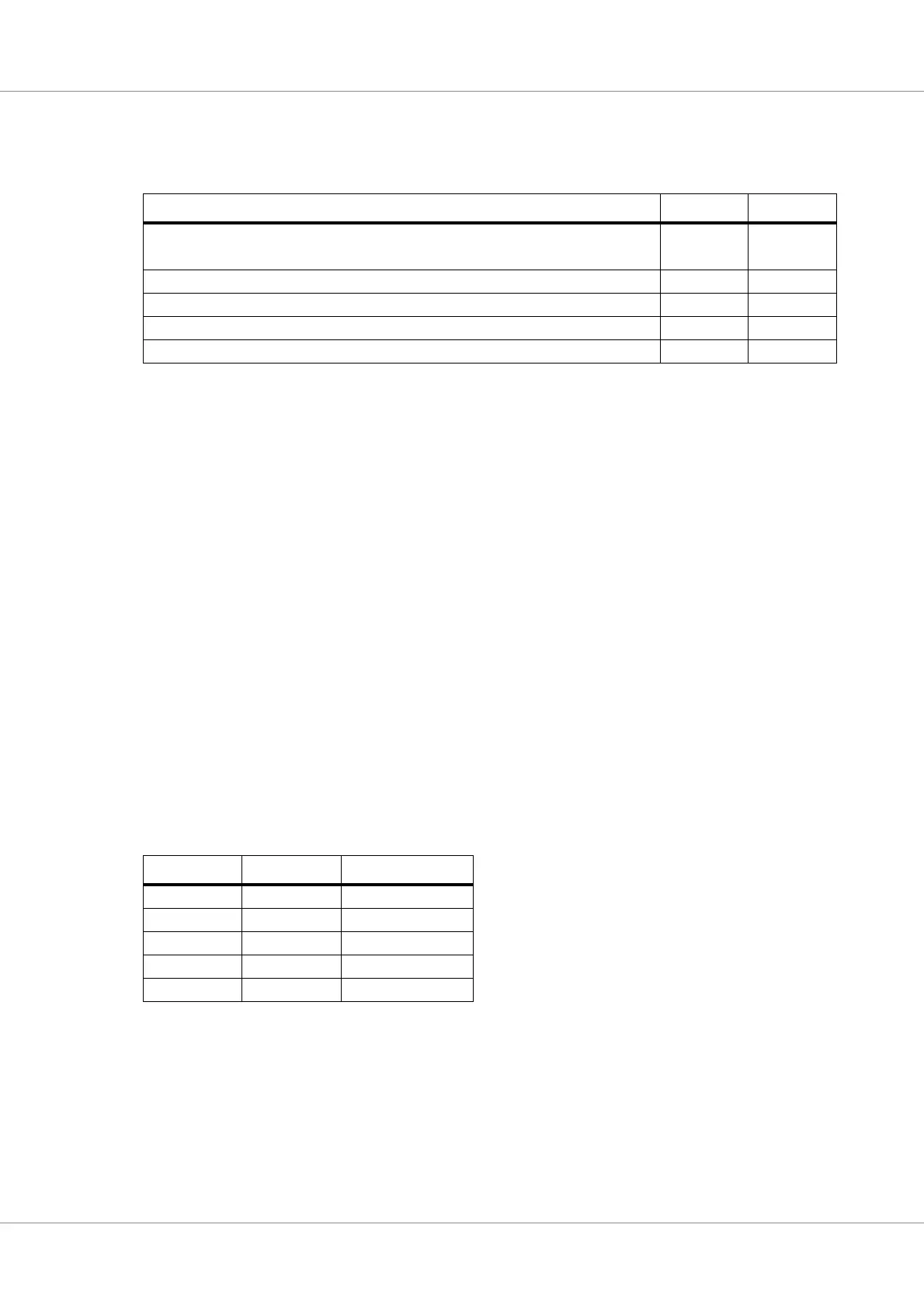

latency of four clock cycles at instruction level. The table below shows the GRFPU instruction timing

when used together with GRFPC:

The GRFPC controller implements the SPARC deferred trap model, and the FPU trap queue (FQ) can

contain up to 7 queued instructions when an FPU exception is taken. The version field in %fsr has the

value of 2 to signal that the processor is implemented with the GRFPU.

The GRFPU does not handle denormalized numbers as inputs and will in that case cause an fp_excep-

tion with the FPU trap type set to unfinised_FPOP (tt=2). There is a non-standard mode in the FPU

that will instead replace the denormalized inputs with zero and thus never create this condition.

6.6 Co-processor interface

The coprocessor interface is unused and disabled in this device.

6.7 AMBA interface

6.7.1 Overview

The LEON4 processor has one AHB master interface. The types of AMBA accesses supported and

performed by the processor depend on the accessed memory area’s cachability, if the corresponding

cache is enabled, and if the accessed memory area has been marked as being on the wide bus.

Cacheable instructions are fetched with a burst of two 128-bit accesses.

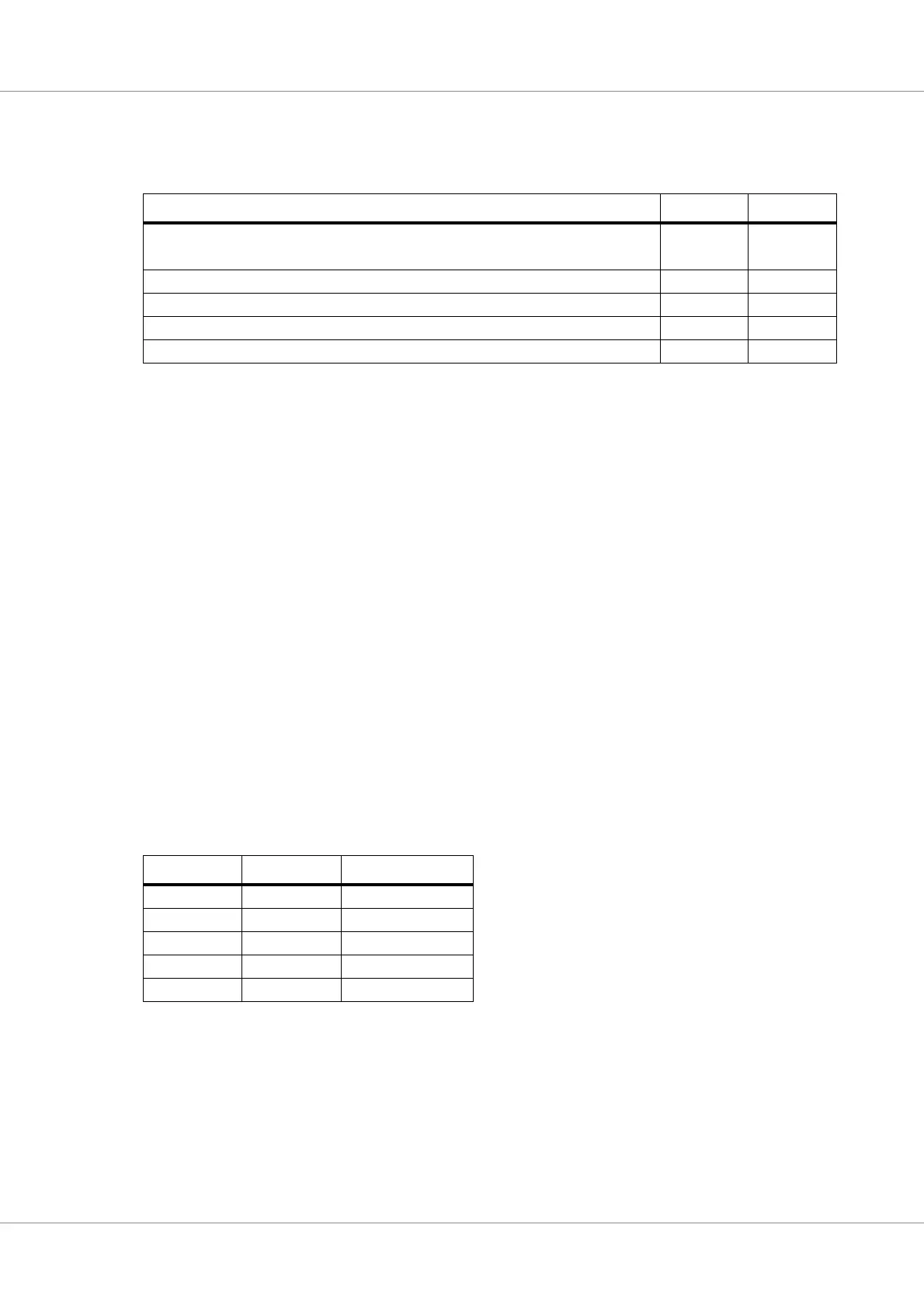

The HPROT signals of the AHB bus are driven to indicate if the accesses is instruction or data, and if

it is a user or supervisor access.

In case of atomic accesses, a locked access will be made on the AMBA bus to guarantee atomicity as

seen from other masters on the bus.

6.7.2 Cachability

The processor treats the memory areas 0x00000000 - 0x7FFFFFFF and 0xC0000000 - 0xCFFFFFFF

as cacheable. The test of the physical address space is treated as uncached.

Table 41. GRFPU instruction timing with GRFPC

Instruction Throughput Latency

FADDS, FADDD, FSUBS, FSUBD,FMULS, FMULD, FSMULD, FITOS, FITOD,

FSTOI, FDTOI, FSTOD, FDTOS, FCMPS, FCMPD, FCMPES. FCMPED

14

FDIVS 14 16

FDIVD 15 17

FSQRTS 22 24

FSQRTD 23 25

Table 42. HPROT values

Type of access User/Super HPROT

Instruction User 1100

Instruction Super 1110

Data User 1101

Data Super 1111

MMU Any 1101

Loading...

Loading...