GR740-UM-DS, Nov 2017, Version 1.7 132 www.cobham.com/gaisler

GR740

12.9 Registers

The core is programmed through registers mapped into AHB I/O address space. All accesses to regis-

ter address space must be made with word (32-bit) accesses.

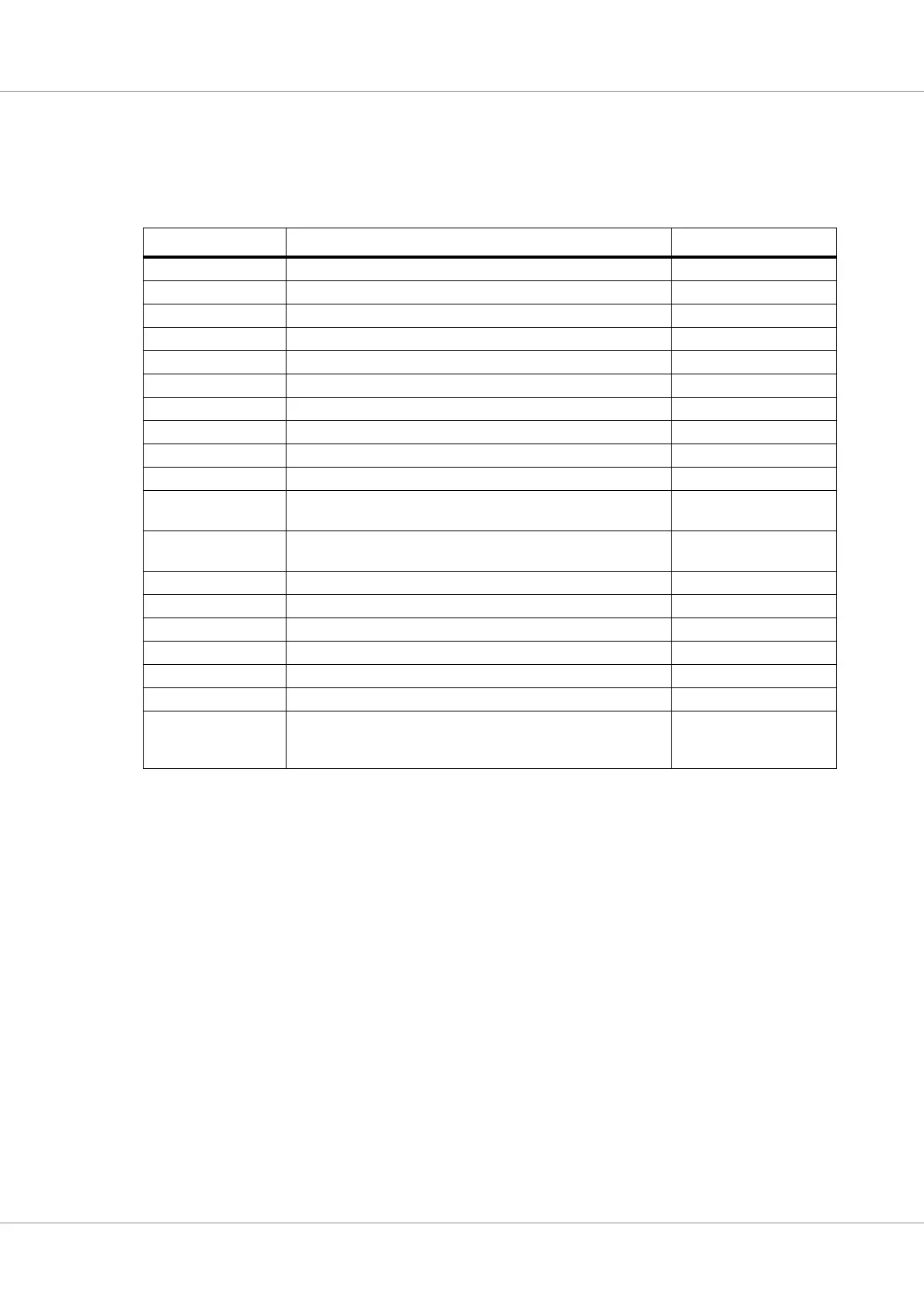

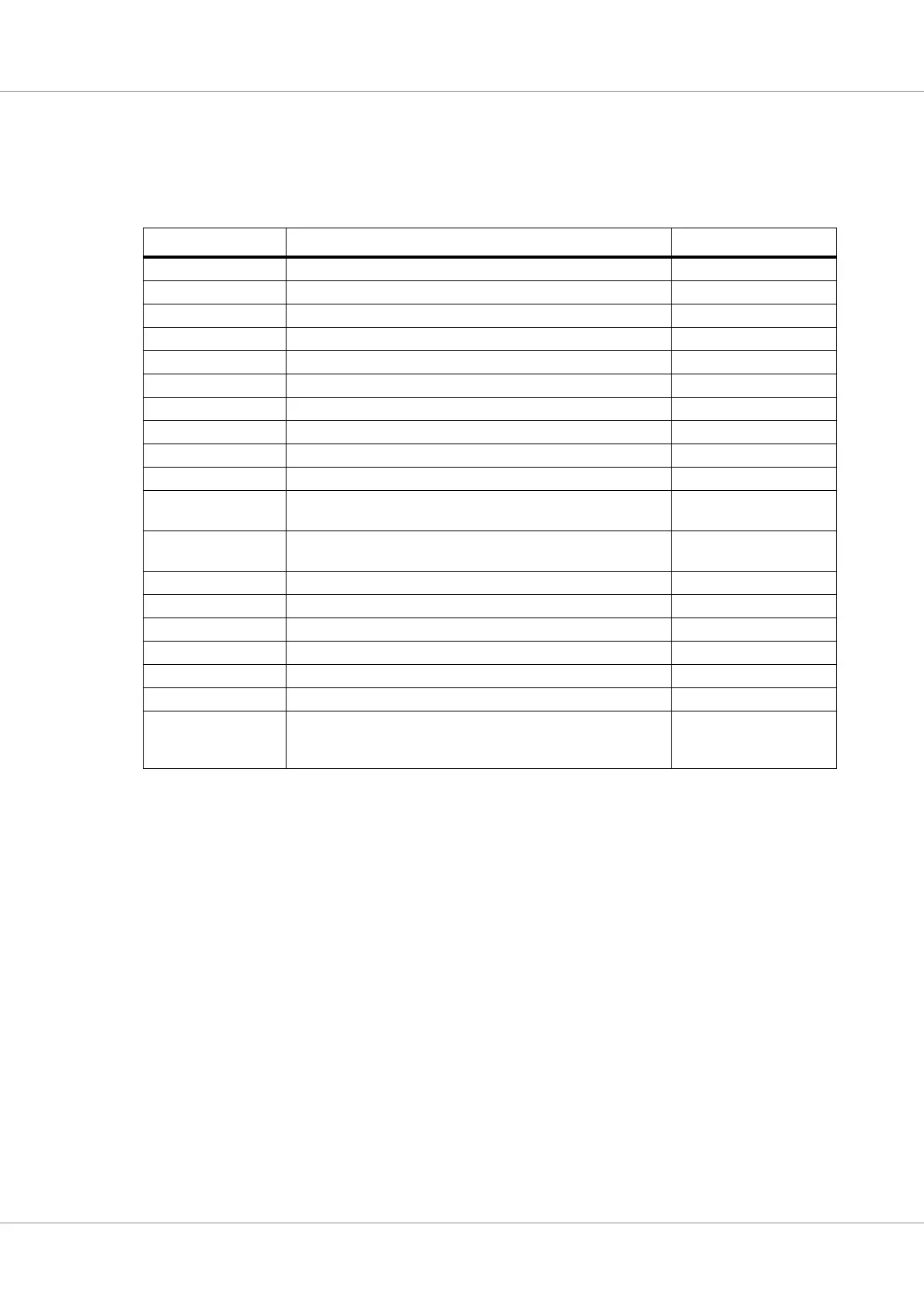

Table 129.GRIOMMU registers

AHB address offset Register Writable in ASMP block

0x00 Capability register 0 No

0x04 Capability register 1 No

0x08 Capability register 2 No

0x0C Reserved -

0x10 Control register No

0x14 TLB/cache flush register Yes, protected*

0x18 Status register Yes, protected*

0x1C Interrupt mask register Yes, protected*

0x20 AHB Failing Access register No

0x24 - 0x3C Reserved, must not be accessed -

0x40 - 0x7C Master configuration registers.

Master n configuration register is located at offset 0x40 + n*0x4.

No

0x80-0xBC Group control registers.

Group n’s control register is located at offset 0x80 + n*0x4.

Yes, protected*

0xC0 Diagnostic cache access register No

0xC4 - 0xE0 Diagnostic cache access data registers 0 - 7 No

0xE4 Diagnostic cache access tag register No

0xE8 Data RAM error injection register No

0xEC Tag RAM error injection register No

0xF0 - 0xFF Reserved, must not be accessed No

0x100 - 0x10C ASMP access control registers.

The control register for ASMP block n is located at offset

0x100+n*0x4.

No

* Register is duplicated in ASMP register block at offset 0x1000 + register offset. The number of ASMP register blocks is

four. ASMP register block n starts at offset n*0x1000. Register is only writable if allowed by the corresponding ASMP

access control register field.

Loading...

Loading...