GR740-UM-DS, Nov 2017, Version 1.7 288 www.cobham.com/gaisler

GR740

19.3 Memory mapped IO

Accesses to IO have similar timing as PROM accesses. The IO select (IO_SN) and output enable

(PROMIO_OEN) signals are delayed one clock to provide stable address before IO_SN is asserted.

All accesses are performed as non-consecutive accesses as shown in figure 28. The data2 phase is

extended when waitstates are added.

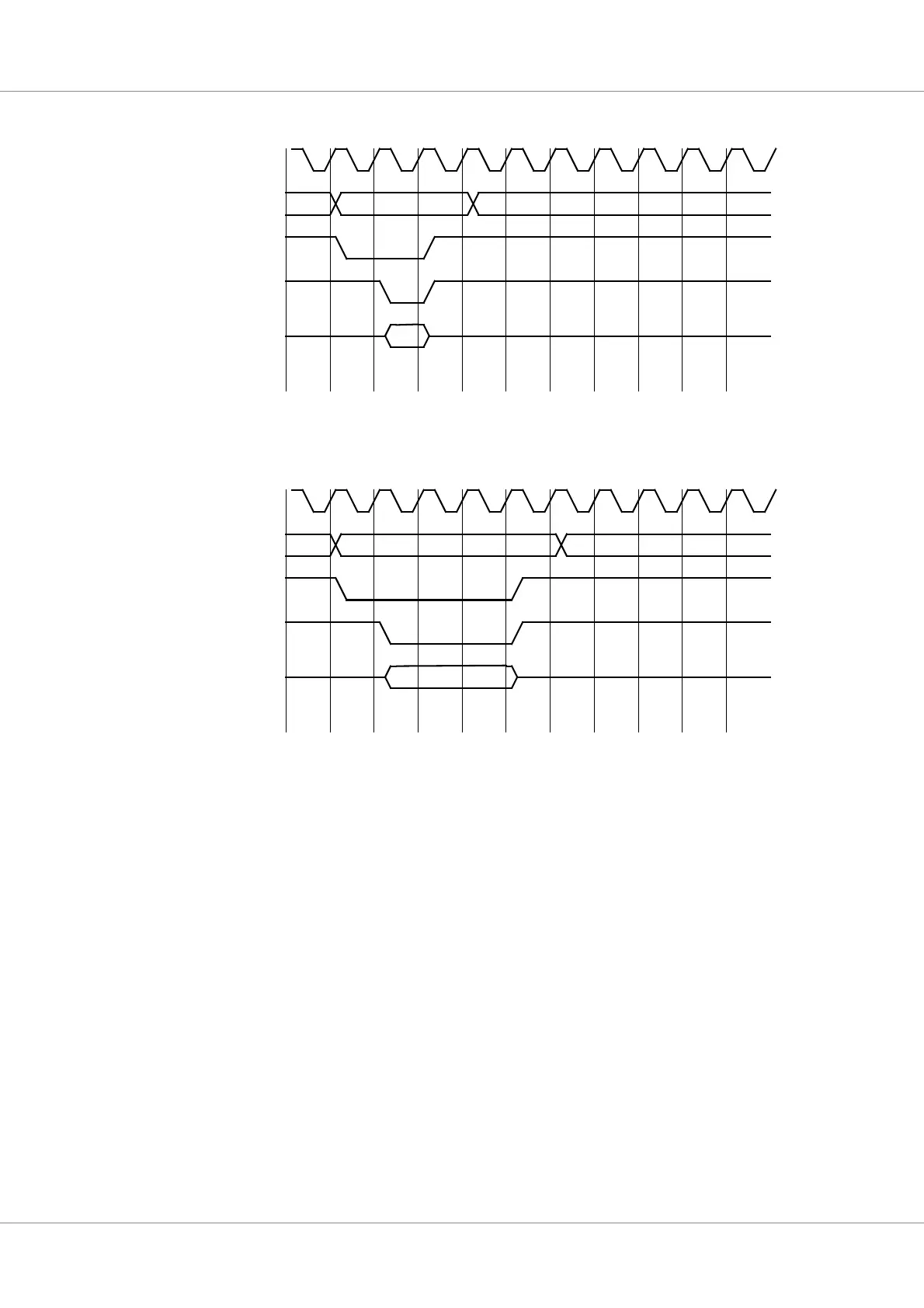

Figure 26. Prom write cycle (0-waitstates)

data

promio_addr

prom_cen

promio_data

promio_wen

lead-out

clk

A1

D1

lead-in

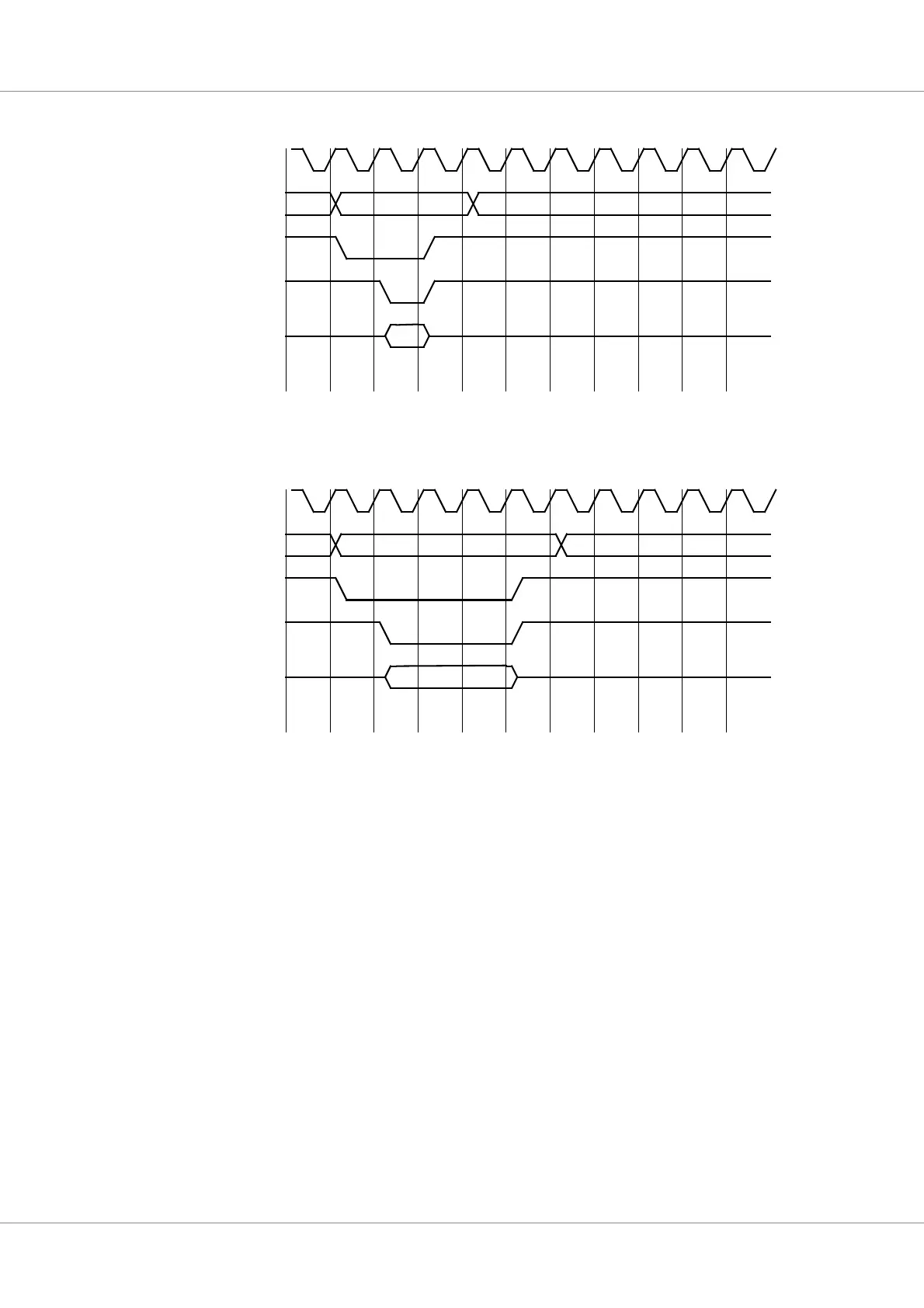

Figure 27. Prom write cycle (2-waitstates)

data

promio_addr

prom_cen

promio_data

promio_wen

lead-out

clk

A1

D1

lead-in data

data

Loading...

Loading...