GR740-UM-DS, Nov 2017, Version 1.7 253 www.cobham.com/gaisler

GR740

MHz. A propagation delay of up to one codec clock cycle (50 ns) can be tolerated in each clock-

domain crossing signal.

Both clock domains are reset via the SYS_RESETN input, as described in section 4.3. Care must be

taken so that the GR1553B_CLK is active and toggling before SYS_RESETN is deasserted.

16.8 Registers

The core is programmed through registers mapped into APB address space.

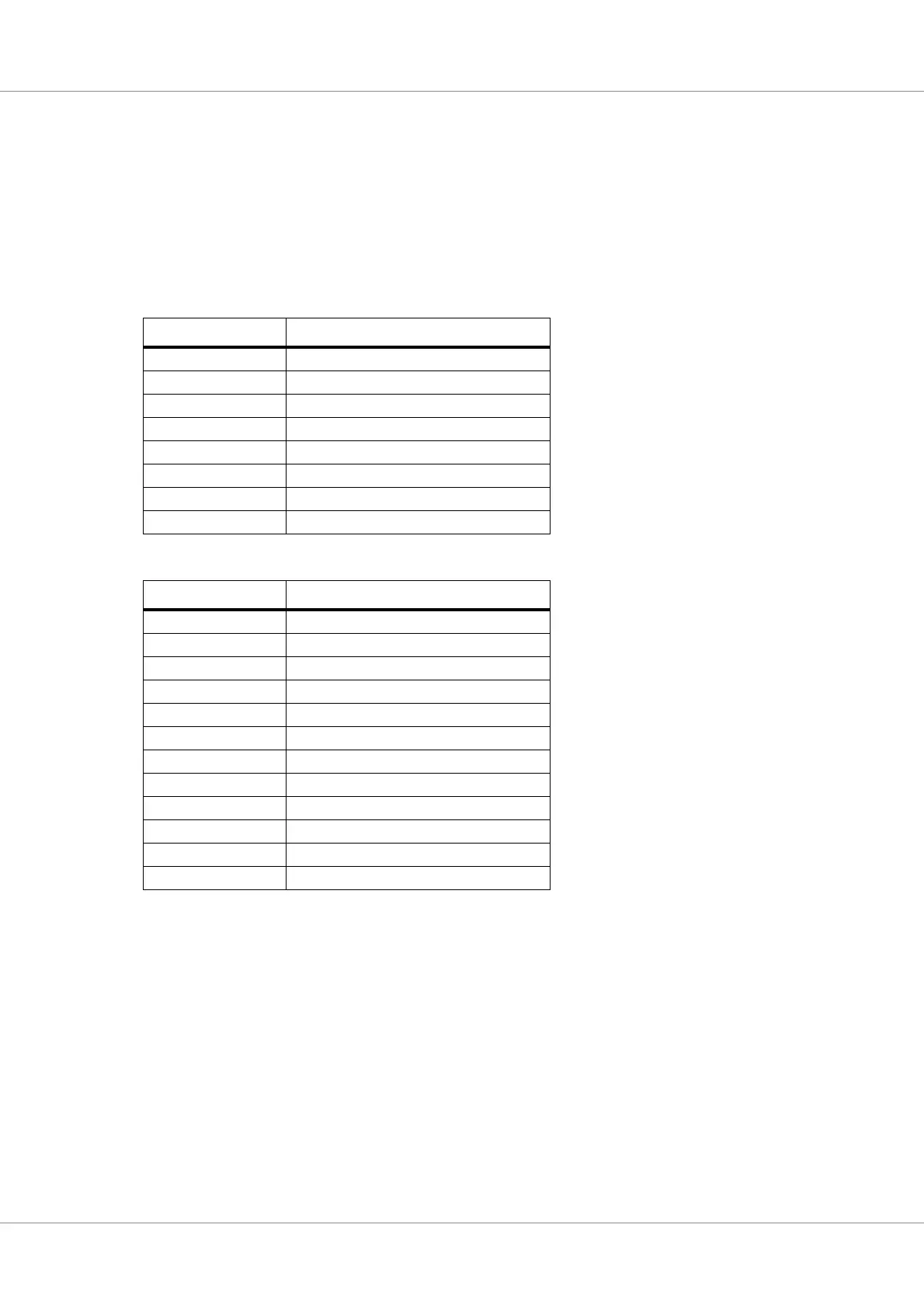

Table 303.MIL-STD-1553B interface registers

APB address offset Register

0x00 IRQ Register

0x04 IRQ Enable

0x08...0x0F (Reserved)

0x10 Hardware config register

0x14...0x3F (Reserved)

0x40...0x7F BC Register area (see table 304)

0x80...0xBF RT Register area (see table 305)

0xC0...0xFF BM Register area (see table 306)

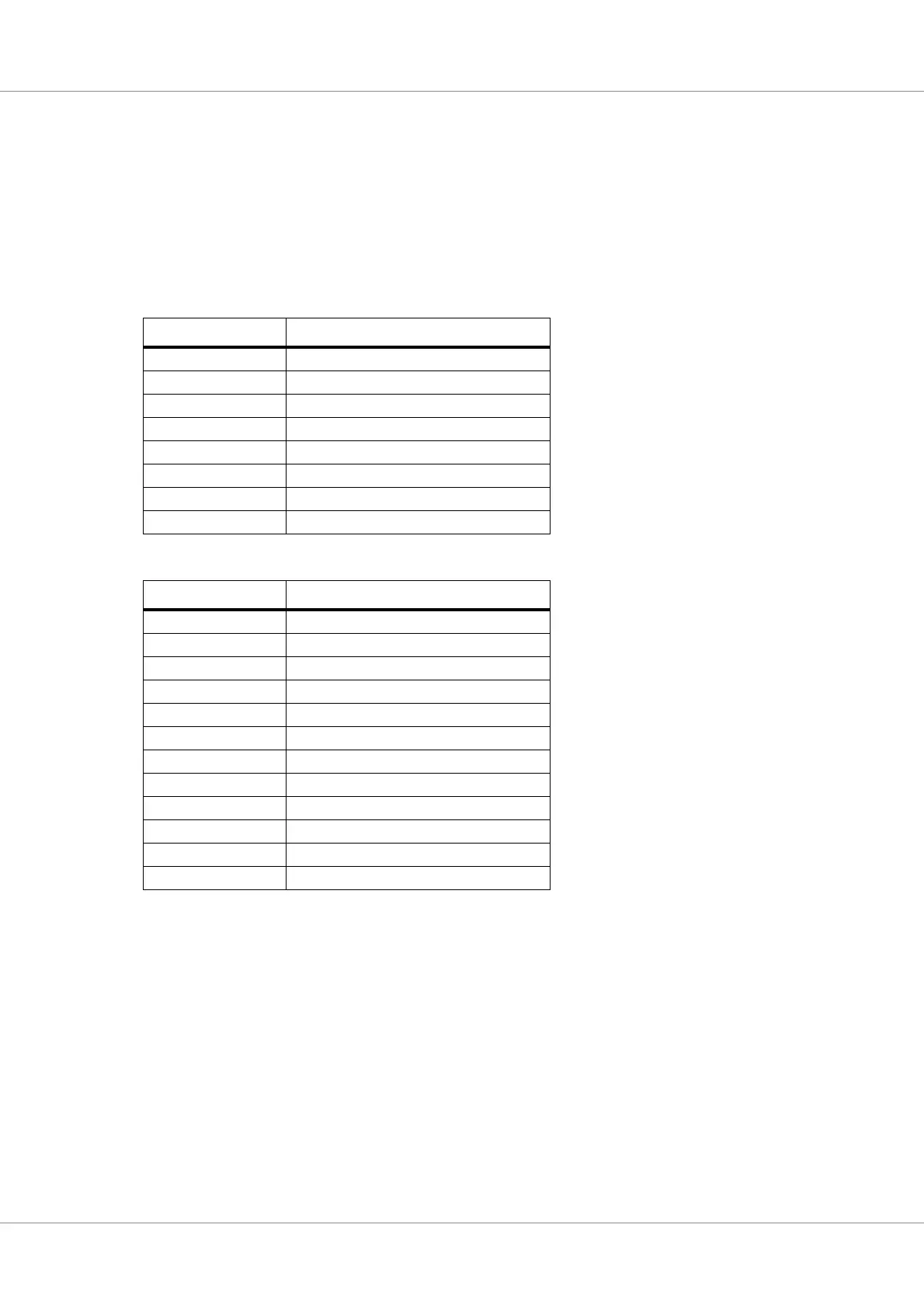

Table 304.MIL-STD-1553B interface BC-specific registers

APB address offset Register

0x40 BC Status and Config register

0x44 BC Action register

0x48 BC Transfer list next pointer

0x4C BC Asynchronous list next pointer

0x50 BC Timer register

0x54 (Reserved)

0x58 BC Transfer-triggered IRQ ring position

0x5C BC Per-RT bus swap register

0x60...0x67 (Reserved)

0x68 BC Transfer list current slot pointer

0x6C BC Asynchronous list current slot pointer

0x70...0x7F (Reserved)

Loading...

Loading...