GR740-UM-DS, Nov 2017, Version 1.7 351 www.cobham.com/gaisler

GR740

28 Register for bootstrap signals

28.1 Overview

This interface provides a programmable register that controls the internal values of bootstrap signals

in the design.

28.2 Operation

The core contains one register of 20 bits that is mapped into APB address space. The value in bits 15:0

of this register is propagated to other peripherals in the design. The reset value of the register is taken

from the GPIO signals and from the bootstrap signals PLL_IGNLOCK, PCIMODE_ENABLE,

MEM_CLKSEL and MEM_IFWIDTH. The value of the GPIO and other bootstrap signal is latched

when the device’s internal reset signal is deasserted.

28.3 Registers

The peripheral provides one register mapped into APB address space.

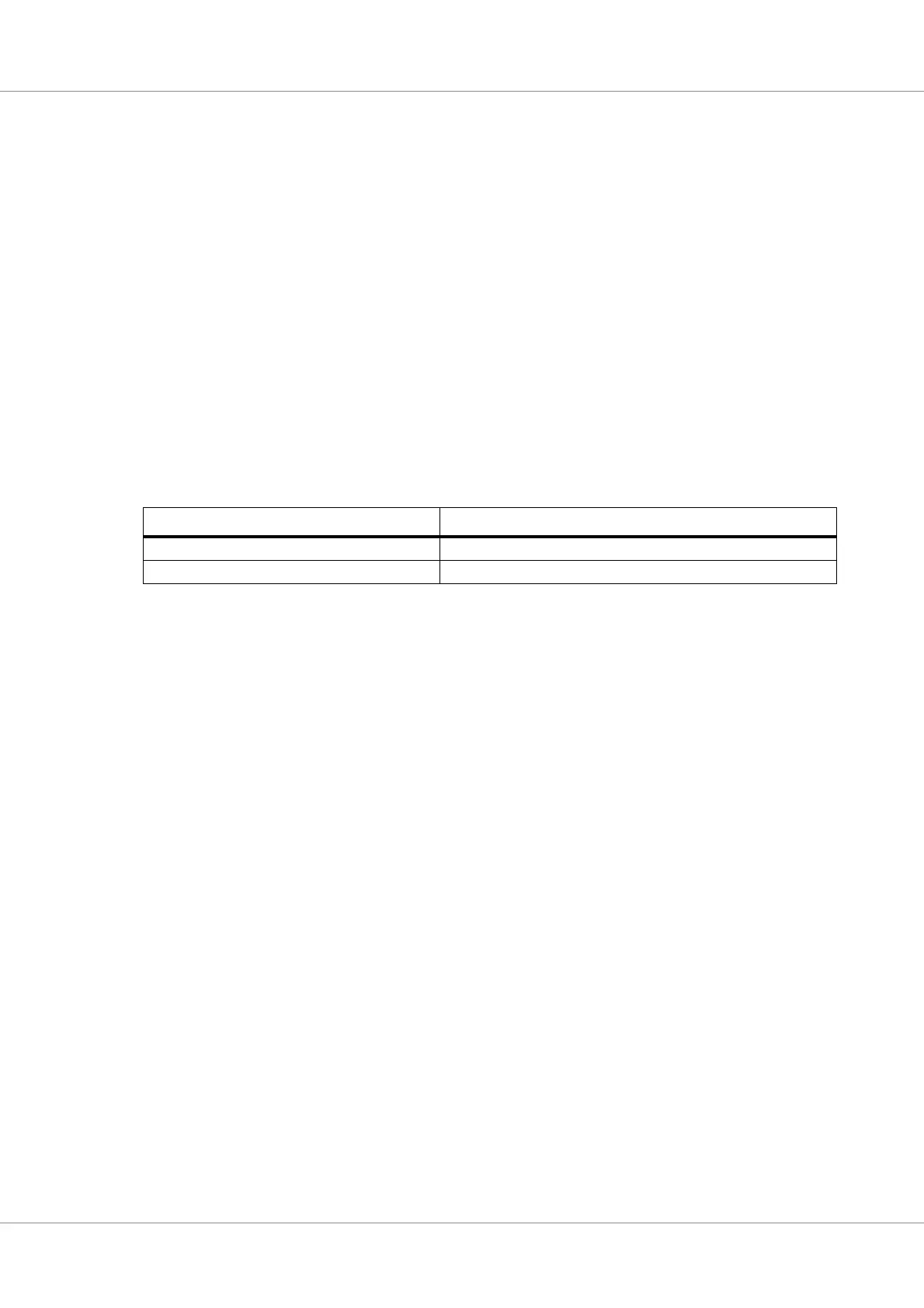

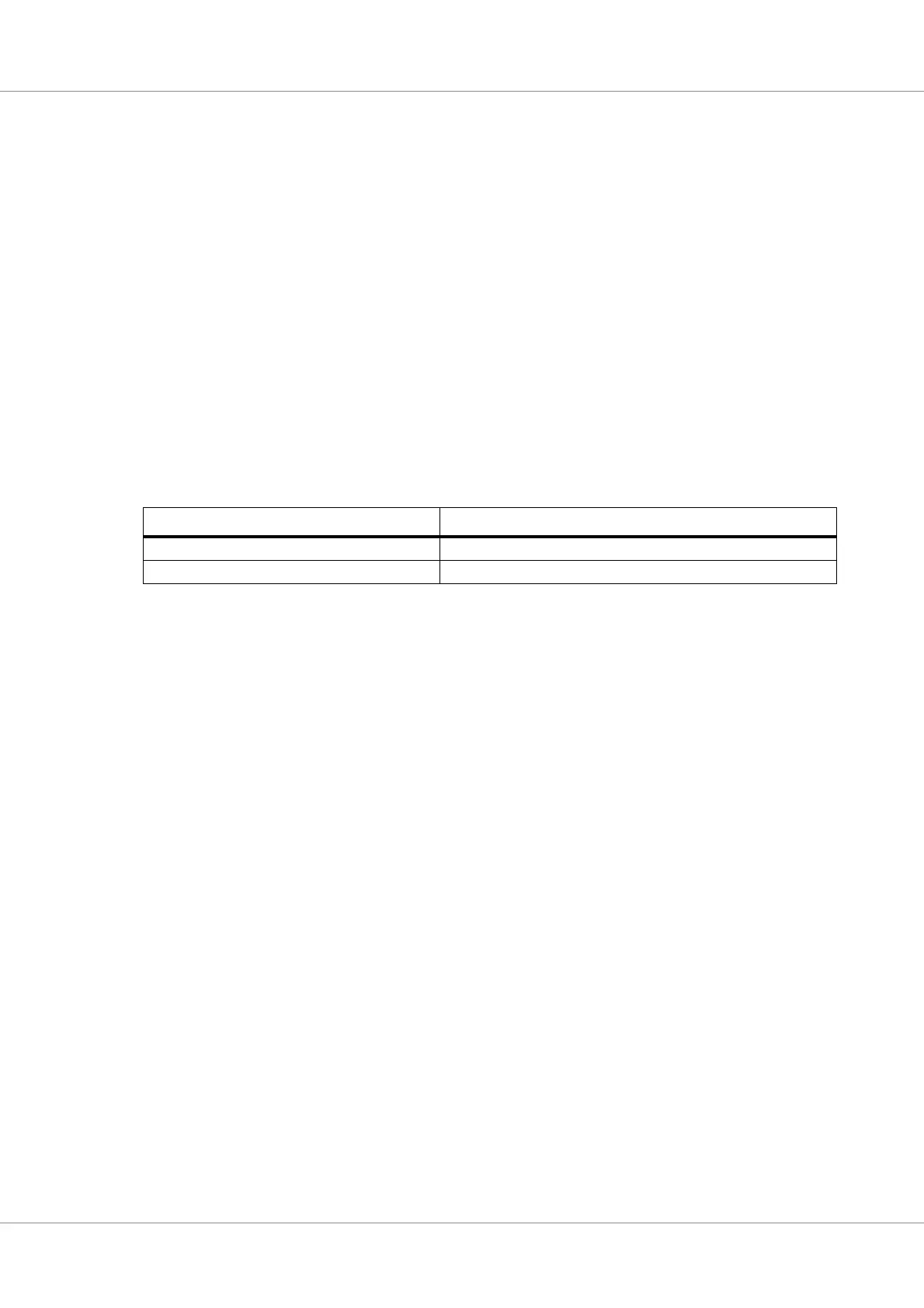

Table 444.General purpose register registers

APB address offset Register

0x00 Bootstrap register

0x04 - 0xFF RESERVED (first register is aliased in all words in this area)

Loading...

Loading...