GR740-UM-DS, Nov 2017, Version 1.7 92 www.cobham.com/gaisler

GR740

9.4 Registers

The cache is configured via registers mapped into the AHB memory address space.

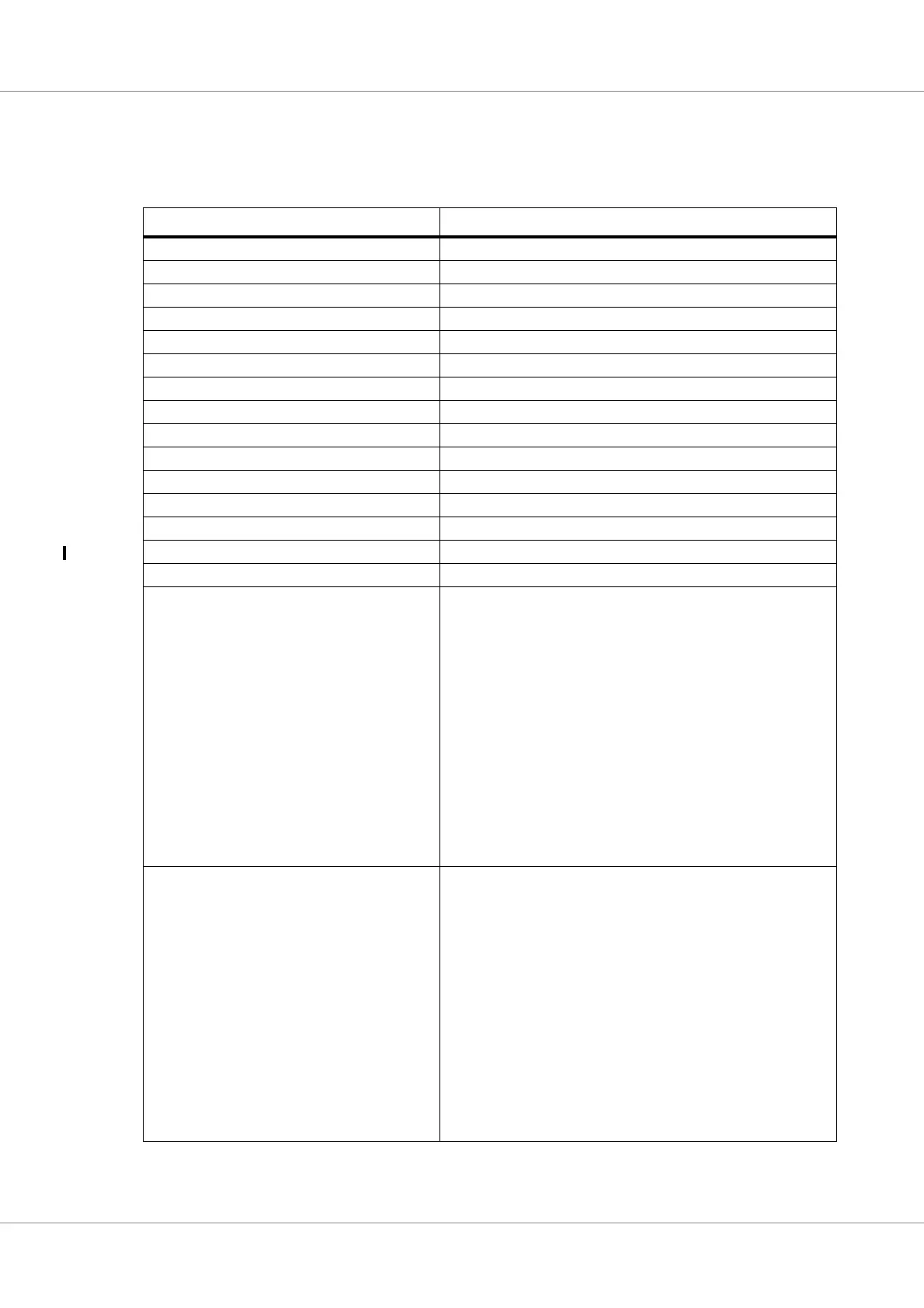

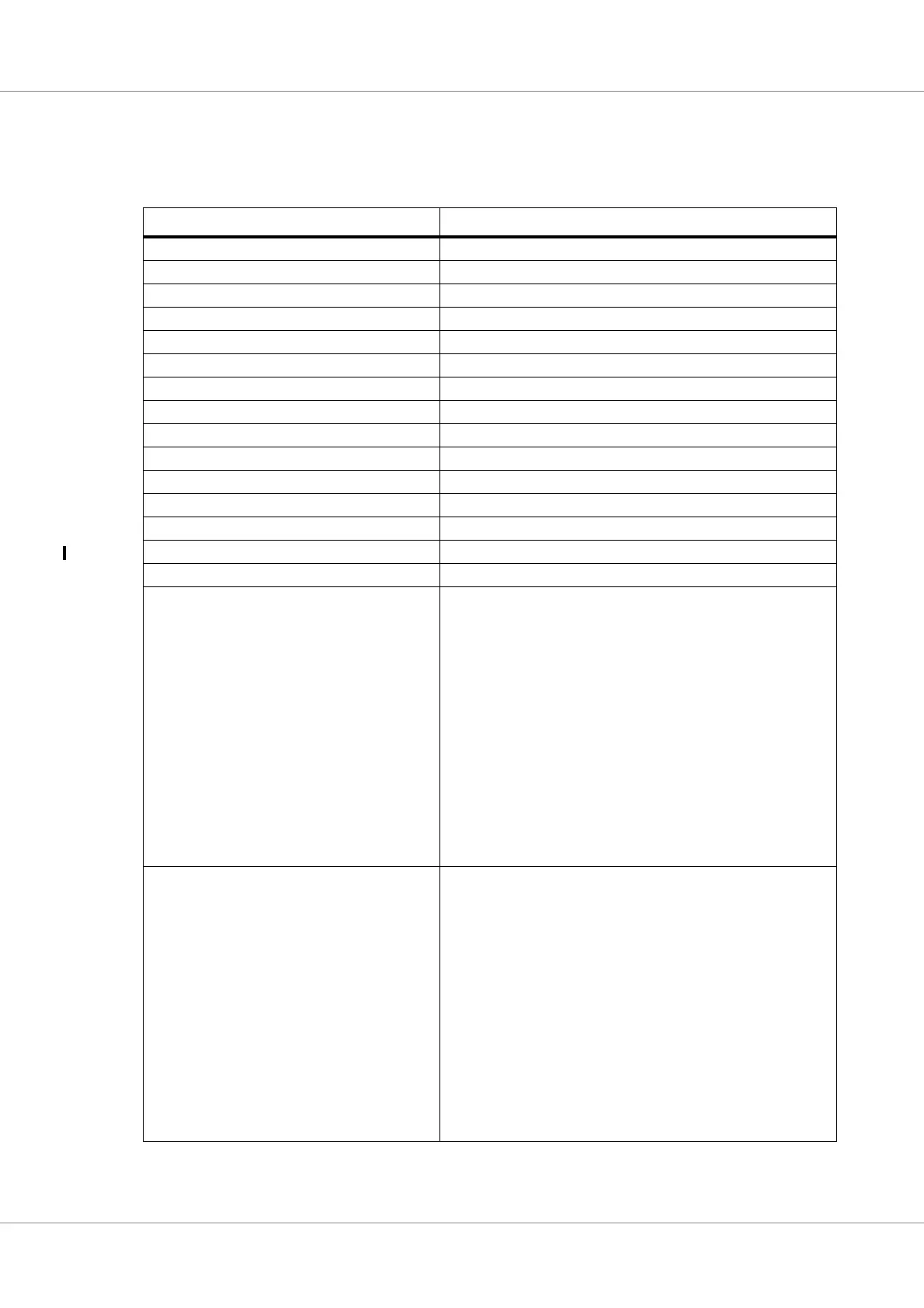

Table 68. L2C: AHB registers

AHB address offset Register

0x00 Control register

0x04 Status register

0x08 Flush (Memory address)

0x0C Flush (set, index)

0x10 - 0x1C Reserved

0x20 Error status/control

0x24 Error address

0x28 TAG-check-bit

0x2C Data-check-bit

0x30 Scrub Control/Status

0x34 Scrub Delay

0x38 Error injection

0x3C Access control

0x50 Error handling / injection configuration

0x80 - 0xFC MTRR registers

0x80000 - 0x8FFFC Diagnostic interface (Tag)

0x80000: Tag 1, way-1

0x80004: Tag 1, way-2

0x80008: Tag 1, way-3

0x8000C: Tag 1, way-4

0x80010: Tag check-bits way-0,1,2,3 (Read only)

bit[31] = RESERVED

bit[30:24] = check-bits for way-1.

bit[23] = RESERVED

bit[22:16] = check-bits for way-2.

bit[15] = RESERVED

bit[14:8] = check-bits for way-3.

bit[7] = RESERVED

bit[6:0] = check-bits for way-4.

0x80020: Tag 2, way-1

0x80024: ...

0x200000 - 0x3FFFFC Diagnostic interface (Data)

0x200000 - 0x27FFFC: Data or check-bits way-1

0x280000 - 0x2FFFFF: Data or check-bits way-2

0x300000 - 0x27FFFC: Data or check-bits way-3

0x380000 - 0x3FFFFF: Data or check-bits way-4

When check-bits are read out:

Only 32-word at offset 0x0, 0x10, 0x20,... are valid check-bits.

bit[31] = RESERVED

bit[30:24] = check-bits for data word at offset 0x0.

bit[23] = RESERVED

bit[22:16] = check-bits for data word at offset 0x4.

bit[15] = RESERVED

bit[14:8] = check-bits for data word at offset 0x8.

bit[7] = RESERVED

bit[6:0] = check-bits for data word at offset 0xc.

Loading...

Loading...