GR740-UM-DS, Nov 2017, Version 1.7 93 www.cobham.com/gaisler

GR740

9.4.1

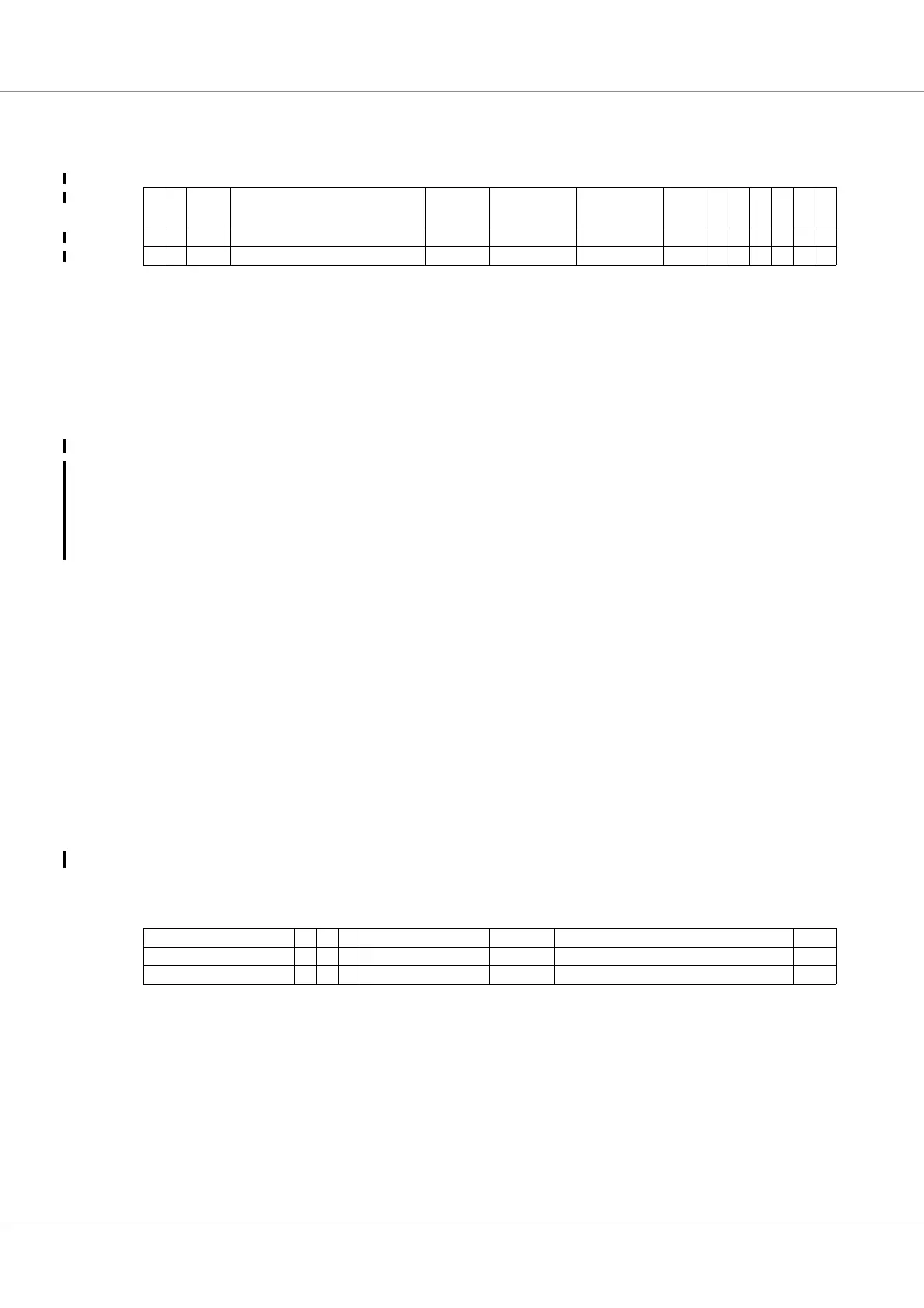

Table 69. 0x00 - L2CC - L2C Control register

Control register

9.4.2 Status register

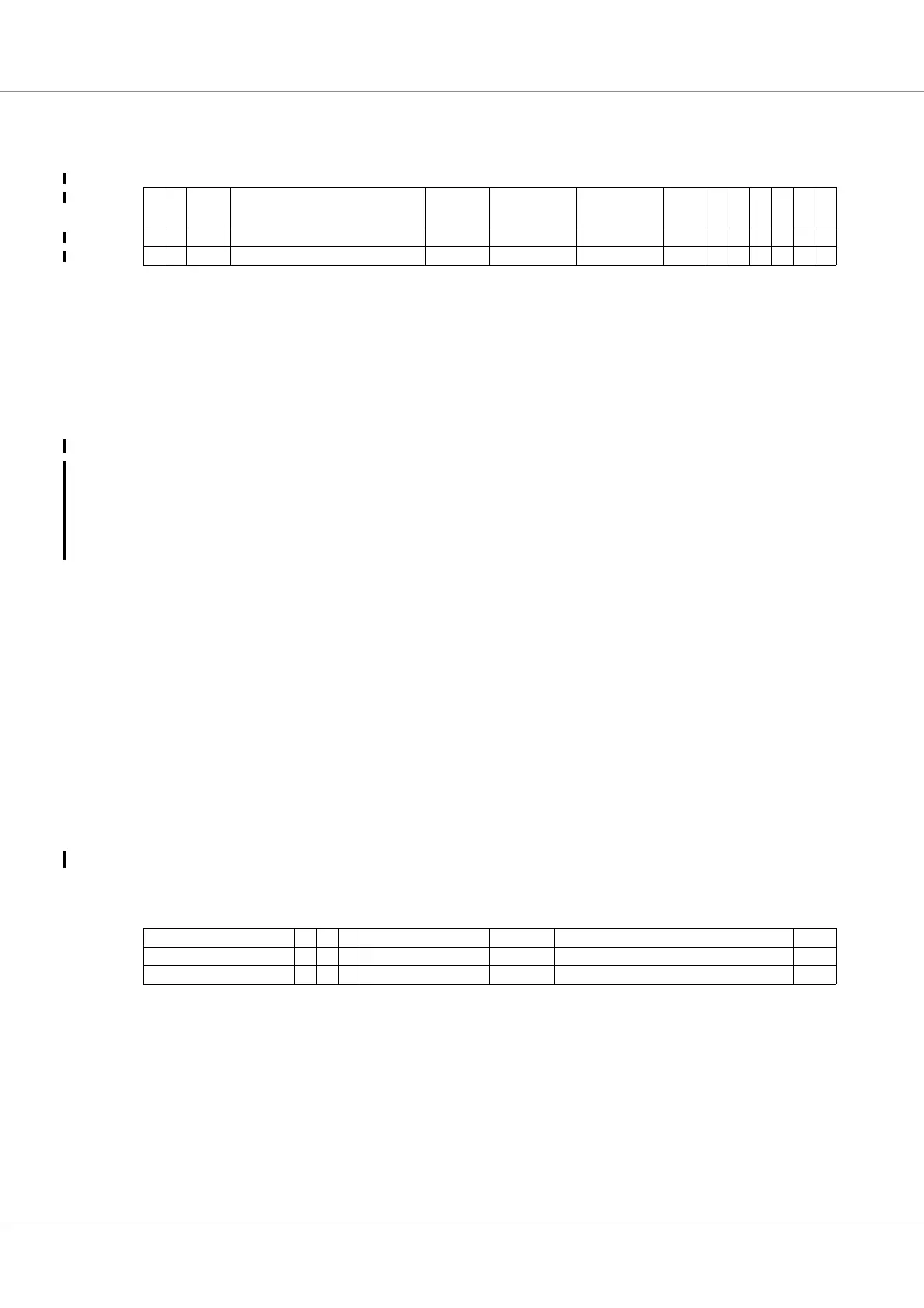

Table 70. 0x04 - L2CS - L2C Status register

31 29 28 27 19 18 16 15 12 11 8 7 6 5 4 3 2 1 0

EN ED

AC

REPL RESERVED BBS INDEX-WAY LOCK RES HP

RH

B

HP

B

UC HC WP HP

0 0 0 0 0b100 0 0 0 0 0 0 0 0 0

rw rw rw r rw rw rw r rw rw rw rw rw rw

31 Cache enable (EN) - When set, the cache controller is enabled. When disabled, the cache is

bypassed.

30 EDAC enable (EDAC)

29: 28 Replacement policy (REPL) -

00: LRU

01: (pseudo-) random

10: Master-index using index-replace field

11: Master-index using the modulus function

27: 19 RESERVED

18: 16 Backend bus size configuration (BBS) -

“100”: Configure backend bus size to 128-bit.

“011”: Configure backend bus size to 64-bit.

“010”: Configure backend bus size to 32-bit.

“000”: No configuration update is done.

Other values: not supported.

15: 12 Master-index replacement (INDEX-WAY) - Way to replace when Master-index replacement policy

and master index is larger than number of ways in the cache.

11: 8 Locked ways (LOCK) - Number of locked ways.

7: 6 RESERVED

5 HPROT read hit bypass (HPRHB) - When set, a non-cacheable and non-bufferable read access will

bypass the cache on a cache hit and return data from memory. Only used with HPROT support.

4 HPROT bufferable (HPB) - When HPROT is used to determine cachability and this bit is set, all

accesses is marked bufferable.

3 Bus usage status mode (UC) - 0 = wrapping mode, 1 = shifting mode.

2 Hit rate status mode (HC) - 0 = wrapping mode, 1 = shifting mode.

1 Write policy (WP) - When set, the cache controller uses the write-through write policy. When not

set, the write policy is copy-back.

0 HPROT enable (HP) - When set, use HPROT to determine cachability.

31 25 24 23 22 21 16 15 13 12 2 1 0

RESERVED LS AT MP MTRR BBUS-W WAY-SIZE WAY

000116 1 * 3

rrrrr r r r

31: 25 RESERVED

24 Cache line size (LS) - 1 = 64 bytes, 0 = 32 bytes.

23 Access time (AT) - Access timing not simulated.

22 Memory protection (MP) - implemented

21: 16 Memory Type Range Registers (MTRR) - Number of MTRR registers implemented (16)

15: 13 Backend bus width (BBUS-W) Set to 1 = 128-bit.

12: 2 Cache way size (WAY-SIZE) - Size in kBytes

1: 0 Multi-Way configuration (WAY)

Set to “11“: 4-way

Loading...

Loading...