GR740-UM-DS, Nov 2017, Version 1.7 94 www.cobham.com/gaisler

GR740

9.4.3

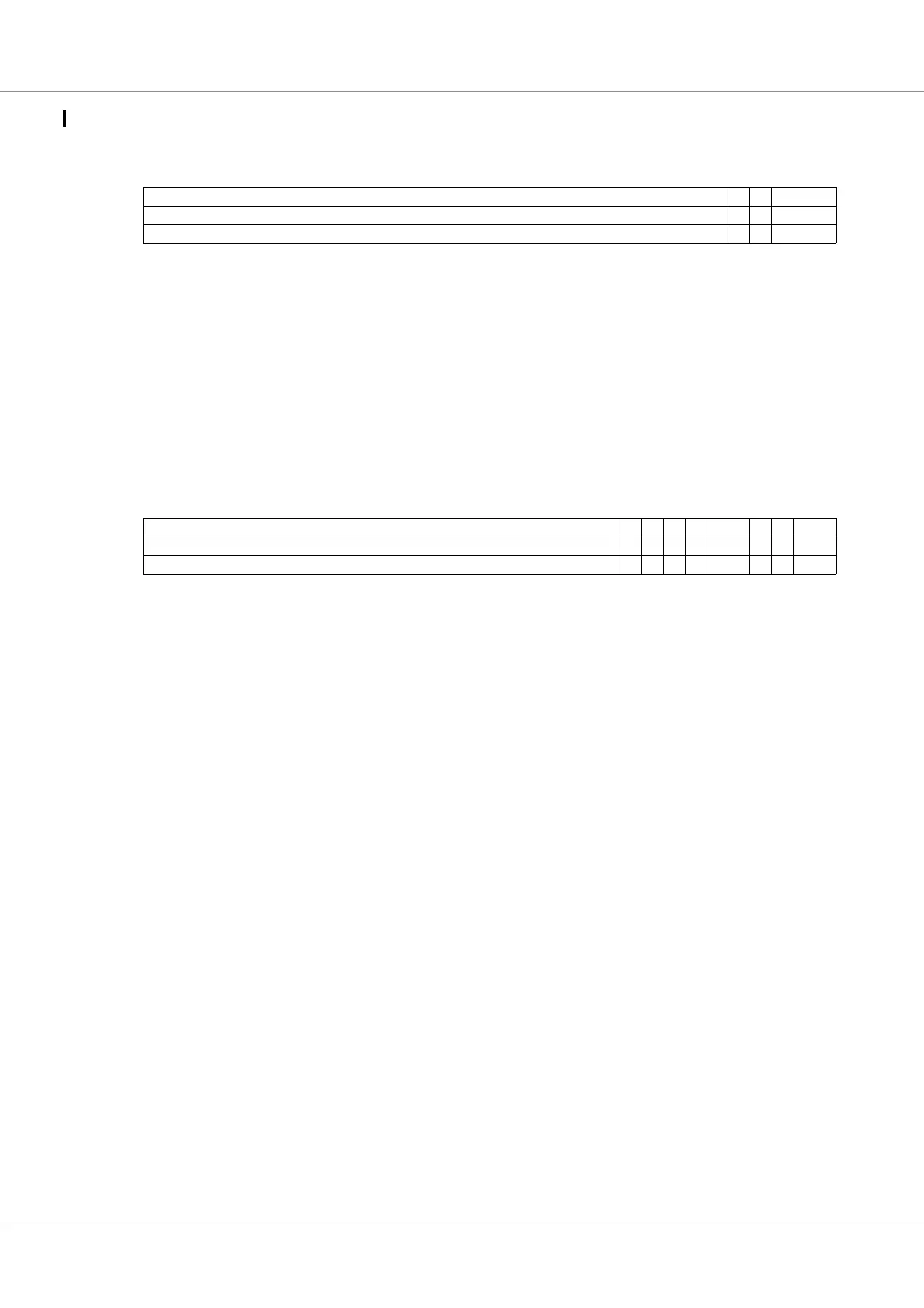

Table 71. 0x08 - L2CFMA - L2C Flush (Memory address) register

Flush memory address register

9.4.4

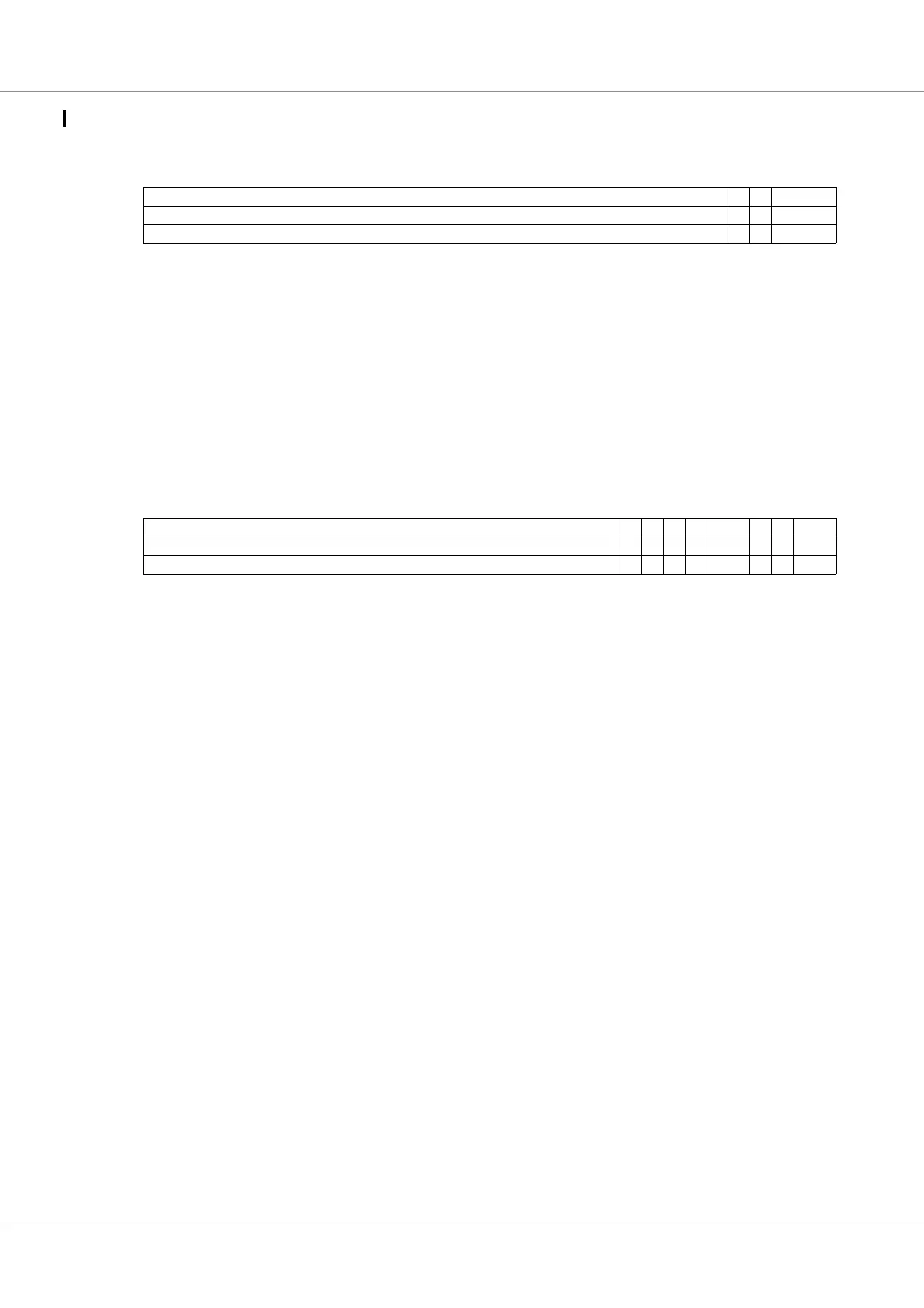

Table 72. 0x0C - L2CFSI - L2C Flush (Set, Index) register

Flush set/index register

31 5432 0

Memory Address (ADDR) R DI FMODE

NR 0 0 0

rw r w rw

31: 5 Memory Address (ADDR) - (For flush all cache lines, this field should be set to zero)

4RESERVED

3 Cache disable (DI) - Setting this bit to ‘1’ is equal to setting the Cache enable bit to ‘0’ in the Cache

Control register

2: 0 Flush mode (FMODE) -

“001“: Invalidate one line, “010”: Write-back one line, “011“: Invalidate & Write-back one line.

“101“: Invalidate all lines, “110”: Write-back all lines, “111“: Invalidate & Write-back all lines.

Only dirty cache lines are written back to memory.

31 16 109876543210

INDEX / TAG FL VB DB R WAY DI WF FMODE

NR 00000000

rw rw rw rw r rw w rw rw

31: 16 Cache line index (INDEX) - used when a specific cache line is flushed

31: 10 (TAG) - used when “way flush” is issued. If a specific cache line is flushed, bit should be set to zero.

When a way flush is issued, the bits in this field will be written to the TAGs for the selected cache

way.

9 Fetch Line (FL) - If set to ‘1’ data is fetched form memory when a “way flush” is issued. If a specific

cache line is flushed, this bit should be set to zero

8 Valid bit (VB) - used when “way flush” is issued. If a specific cache line is flushed, this bit should be

set to zero.

7 Dirty bit (DB) - used when “way flush” is issued. If a specific cache line is flushed, this bit should be

set to zero

6RESERVED

5: 4 Cache way (WAY) -

3 Cache disable (DI) - Setting this bit to ‘1’ is equal to setting the Cache enable bit to ‘0’ in the Cache

Control register.

2 Way-flush (WF) - When set one way is flushed, If a specific cache line should be flushed, this bit

should be set to zero

1: 0 Flush mode (FMODE) -

line flush:

“01“: Invalidate one line

“10”: Write-back one line (if line is dirty)

“11“: Invalidate & Write-back one line (if line is dirty).

way flush:

“01“: Update Valid/Dirty bits according to register bit[8:7] and TAG according to register

bits[31:10]

“10”: Write-back dirty lines to memory

“11“: Update Valid/Dirty bits according to register bits [8:7] and TAG according to register

bits[31:10], and Write-back dirty lines to memory.

Loading...

Loading...