GR740-UM-DS, Nov 2017, Version 1.7 95 www.cobham.com/gaisler

GR740

9.4.5

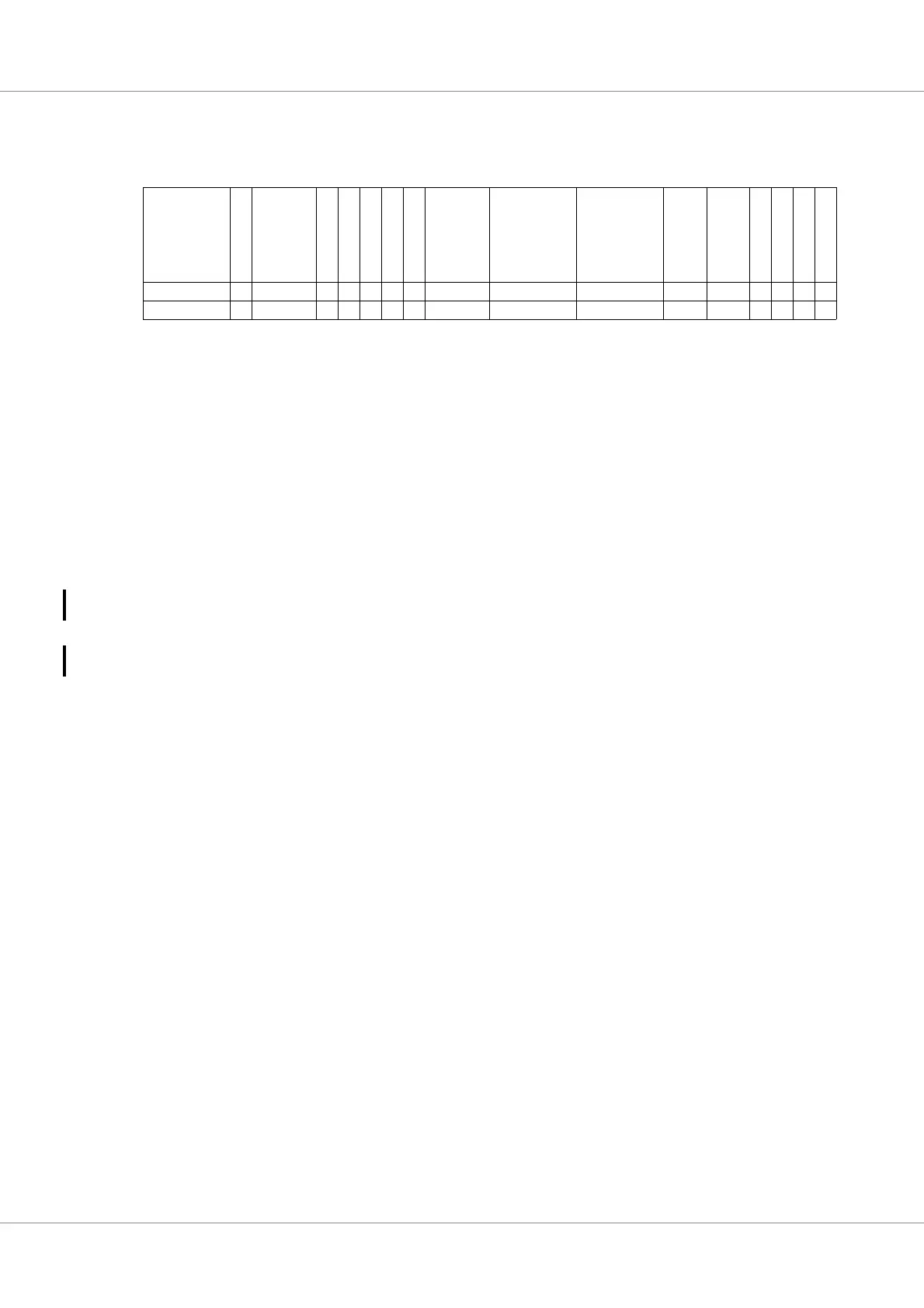

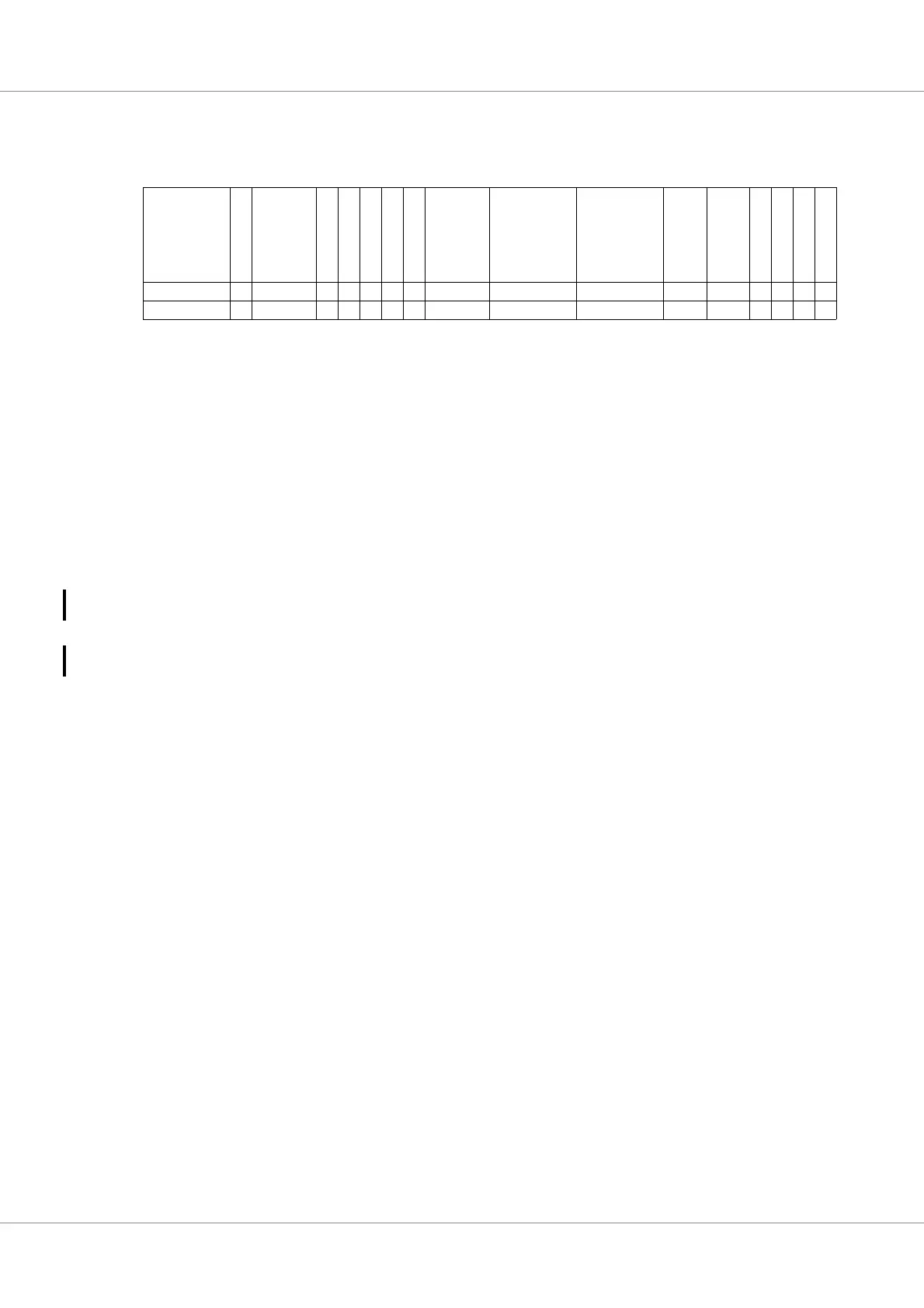

Table 73. 0x20 - L2CERR - L2CError status/control register

Error status/control register

31 28 27 26 24 23 22 21 20 19 18 16 15 12 11 8 7 6 5 4 3 2 1 0

AHB

master

index

S

C

R

U

B

TYPE T

A

G

/

D

A

T

A

C

O

R

/

U

C

O

R

M

U

L

T

I

V

A

L

I

D

D

I

S

E

R

E

S

P

Correctable

error

counter

IRQ

pending

IRQ

mask

Select

CB

Select

TCB

X

C

B

R

C

B

C

O

M

P

R

S

T

NR NR NR NR NR NR NR 0 NR NR 0 0 0 0 0 0 0

r rrrrrrrwr r rw rwrwrwrwrww

31: 28 AHB master that generated the access

27 Scrub error (SCRUB) - Indicates that the error was trigged by the scrubber.

26: 24 Access/Error Type: (TYPE) -

000: cache read, 001: cache write, 010: memory fetch, 011: memory write,

100: Write-protection hit, 101: backend read AHB error, 110: backend write AHB error

23 Tag or data Error - 0 tag error, 1: data error

22 Correctable or uncorrectable error - 0: correctable error, 1: uncorrectable error

21 Multiple error (MULTI) - set when multiple errors has been detected.

20 Error status valid (VALID) - register contains valid error status.

19 Disable error responses for uncorrectable EDAC error (DISERESP).

18: 16 Correctable error counter

15: 12 Interrupt pending

bit3: Backend AHB error bit2: Write-protection hit

bit1: Uncorrectable EDAC error bit0: Correctable EDAC error

11: 8 Interrupt mask (if set this interrupt is unmasked)

bit3: Backend AHB error bit2: Write-protection hit

bit1: Uncorrectable EDAC error bit0: Correctable EDAC error

7: 6 Selects (CB) - data-check-bits for diagnostic data write:

00: use generated check-bits

01: use check-bits in the data-check-bit register

10: XOR check-bits with the data-check-bit register

11: use generated check-bits

Note: If this field is set to "01" or "10" then check-bits are overridden for all accesses. To get con-

trolled error injection, the internal scrubber should be disabled and no accesses should be made to

the Level-2 cache.

5: 4 Selects (TCB) - tag-check-bits for diagnostic tag write:

00: use generated check-bits

01: use check-bits in the tag-check-bit register

10: XOR check-bits with the tag-check-bit register

11: use generated check-bits

Note: If this field is set to "01" or "10" then check-bits are overridden for all accesses. To get con-

trolled error injection, the internal scrubber should be disabled and no accesses should be made to

the Level-2 cache.

3 Xor check-bits (XOR) - If set, the check-bits for the next data write or tag replace will be XOR:ed

withe the check-bit register. Default value is 0.

2 Read check-bits (RCB) - If set, a diagnostic read to the cache data area will return the check-bits

related to that data.When this bit is set, check bits for the data at offset 0x0 - 0xc can be read at offset

0x0, the check bits for data at offset 0x10 - 0x1c can be read at offset 0x10, ...

1 Compare error status (COMP) - If set, a read access matching a uncorrectable error stored in the

error status register will generate a AHB error response. Default value is 0.

0 Resets (RST) - clear the status register to be able to store a new error. After power up the status reg-

ister needs to be cleared before any valid data can be read out.

Loading...

Loading...