GR740-UM-DS, Nov 2017, Version 1.7 388 www.cobham.com/gaisler

GR740

32.3 Registers

The core does not implement any registers accessible over AMBA AHB or APB.

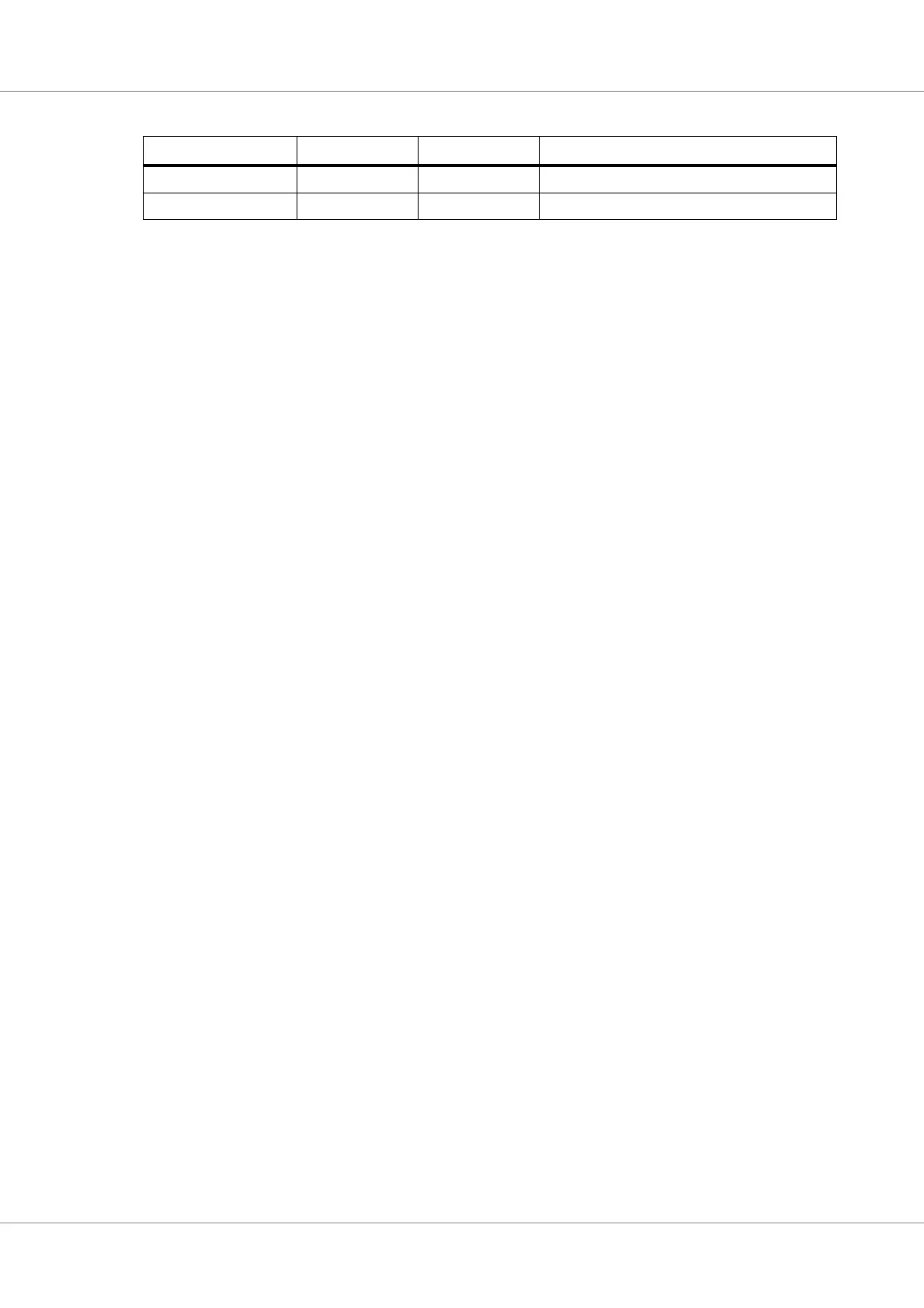

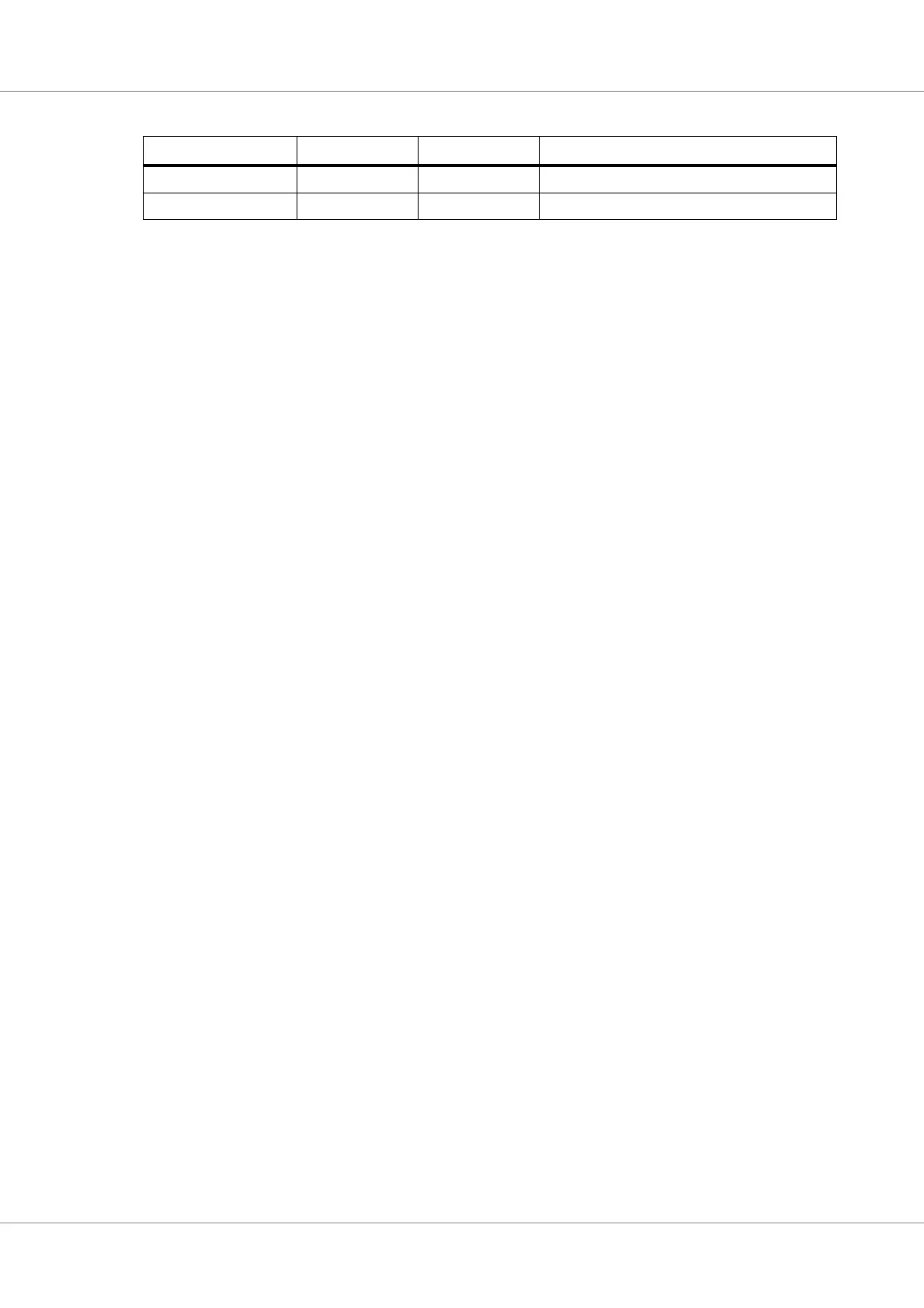

Single write

xx

(2) 0 0

Burst write

xx

(2 + (burst length)) 0 0

x

A prefetch operation ends at the address boundary defined by the prefetch buffer’s size

xx

The core implements posted writes, the number of cycles taken by the master side can only affect the next access.

Table 518.Access latencies

Access Master acc. cycles Slave cycles Delay incurred by performing access over core

Loading...

Loading...