GR740-UM-DS, Nov 2017, Version 1.7 387 www.cobham.com/gaisler

GR740

32.2.5 Core latency

The delay incurred when performing an access over the core depends on several parameters such as

operating frequency of the AMBA buses and memory access patterns. Table 517 below shows core

behavior for a single read operation initiated while the bridge is idle.

While the transitions shown in table 517 are simplified they give an accurate view of the core delay. If

the master interface needs to wait for a bus grant or if the read operation receives wait states, these

cycles must be added to the cycle count in the tables.

Table 518 below lists the delays incurred for single operations that traverse the bridge while the bridge

is in its idle state. The second column shows the number of cycles it takes the master side to perform

the requested access, this column assumes that the master slave gets access to the bus immediately

and that each access is completed with zero wait states. The table only includes the delay incurred by

traversing the core. For instance, when the access initiating master reads the core’s prefetch buffer,

each additional read will consume one clock cycle. However, this delay would also have been present

if the master accessed any other slave.

Write accesses are accepted with zero wait states if the bridge is idle, this means that performing a

write to the idle core does not incur any extra latency. However, the core must complete the write

operation on the master side before it can handle a new access on the slave side. If the core has not

transitioned into its idle state, pending the completion of an earlier access, the delay suffered by an

access be longer than what is shown in the tables in this section.

Since the core has been implemented to use AMBA SPLIT responses there will be an additional delay

where, typically, one cycle is required for the arbiter to react to the assertion of HSPLIT and one clock

cycle for the repetition of the address phase. Also, since the core has support for read and/or write

combining, the number of cycles required for the master will change depending on the access size and

length of the incoming burst access.

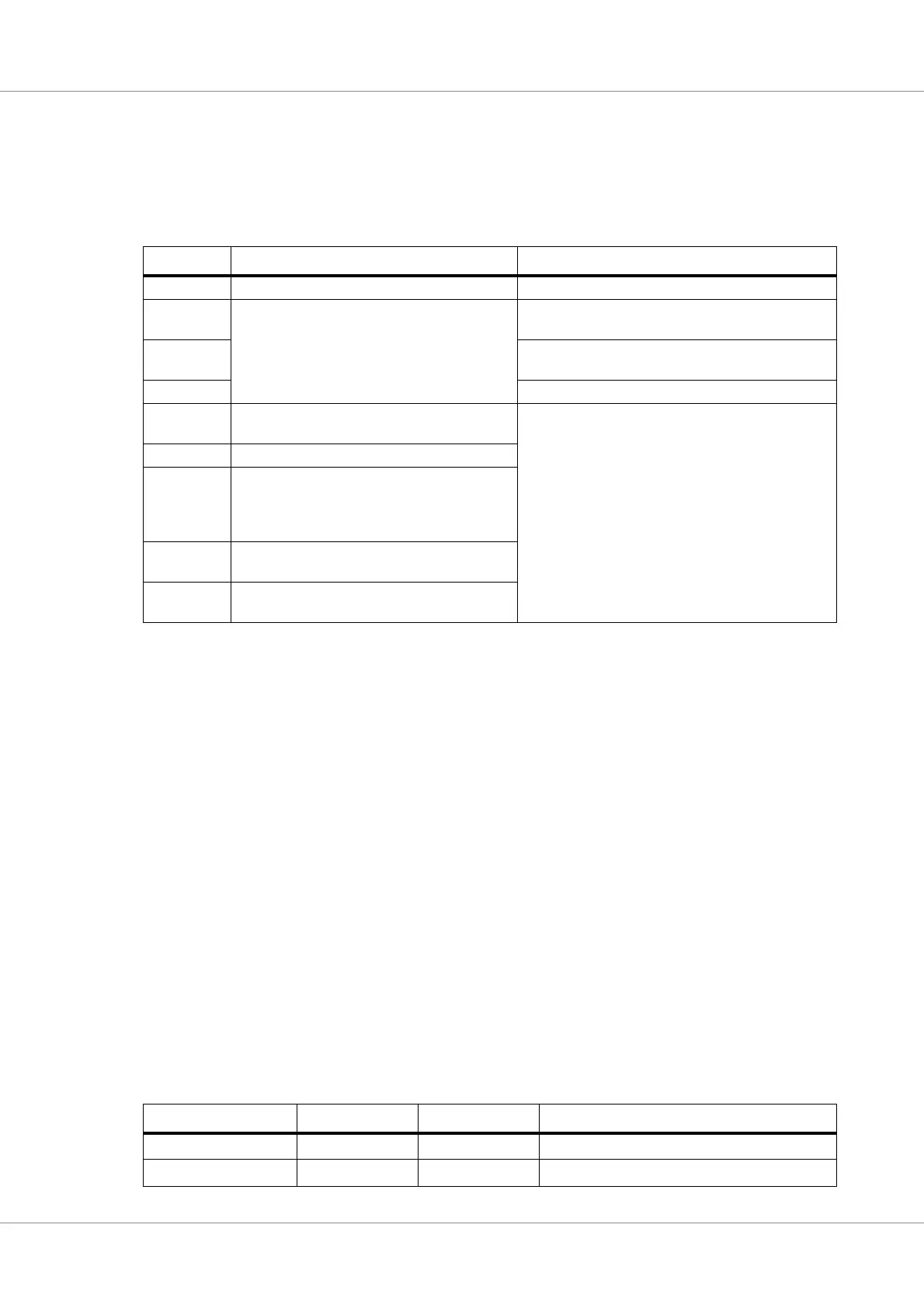

Table 517.Example of single read

Clock cycle Core slave side activity Core master side activity

0 Discovers access and transitions from idle state Idle

1 Slave side waits for master side, SPLIT response

is given to incoming access, any new incoming

accesses also receive SPLIT responses.

Discovers slave side transition. Master interface output

signals are assigned.

2 If bus access is granted, perform address phase. Other-

wise wait for bus grant.

3 Register read data and transition to data ready state.

4 Discovers that read data is ready, assign read

data output and assign SPLIT complete

Idle

5 SPLIT complete output is HIGH

6 Typically a wait cycle for the SPLIT:ed master to

be allowed into arbitration. Core waits for master

to return. Other masters receive SPLIT

responses.

7 Master has been allowed into arbitration and per-

forms address phase. Core keeps HREADY high

8 Access data phase. Core has returned to idle

state.

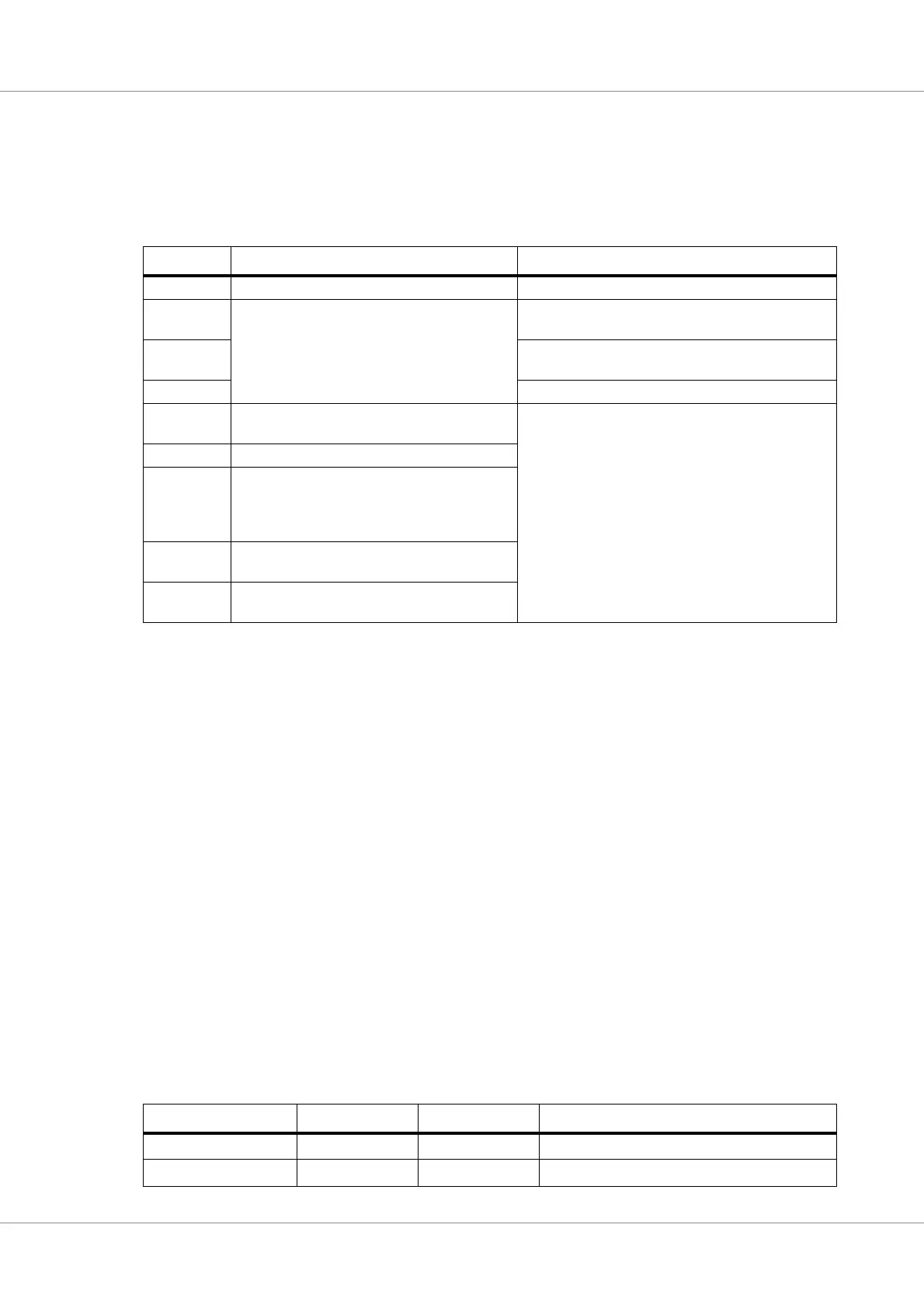

Table 518.Access latencies

Access Master acc. cycles Slave cycles Delay incurred by performing access over core

Single read 3 3 6 * clk

Burst read with prefetch

2 + (burst length)

x

4 (6 + burst length)* clk

Loading...

Loading...