GR740-UM-DS, Nov 2017, Version 1.7 386 www.cobham.com/gaisler

GR740

In case of an ERROR response on the master side the ERROR response will be given for the same

access (address) on the slave side. SPLIT and RETRY responses on the master side are re-attempted

until an OKAY or ERROR response is received.

32.2.3 AHB write transfers

The AHB/AHB bridge implements posted writes. Writes are accepted with zero wait states if the

bridge is idle. During the AHB write transfer on the slave side the data is buffered in the internal write

FIFO and the transfer is completed on the slave side by always giving an OKAY response. The master

interface requests the bus and performs the write transfer when the master bus is granted. If the burst

transfer crosses the 32-byte write burst boundary, a SPLIT response is given. When the bridge has

written the contents of the FIFO out on the master side, the bridge will allow the master on the slave

side to perform the remaining accesses of the write burst transfer.

32.2.4 Read and write combining

Read and write combining allows the bridge to assemble or split AMBA accesses from the Debug

AHB bus into one or several accesses on the Processor AHB bus. This functionality can improve bus

utilization and also allows cores that have differing AMBA access size restrictions to communicate

with each other. The effects of read and write combining is shown in the table below.

Read and write combining is disabled for accesses to the area 0xF0000000 - 0xFFFFFFFF to prevent

accesses wider than 32 bits to register areas.

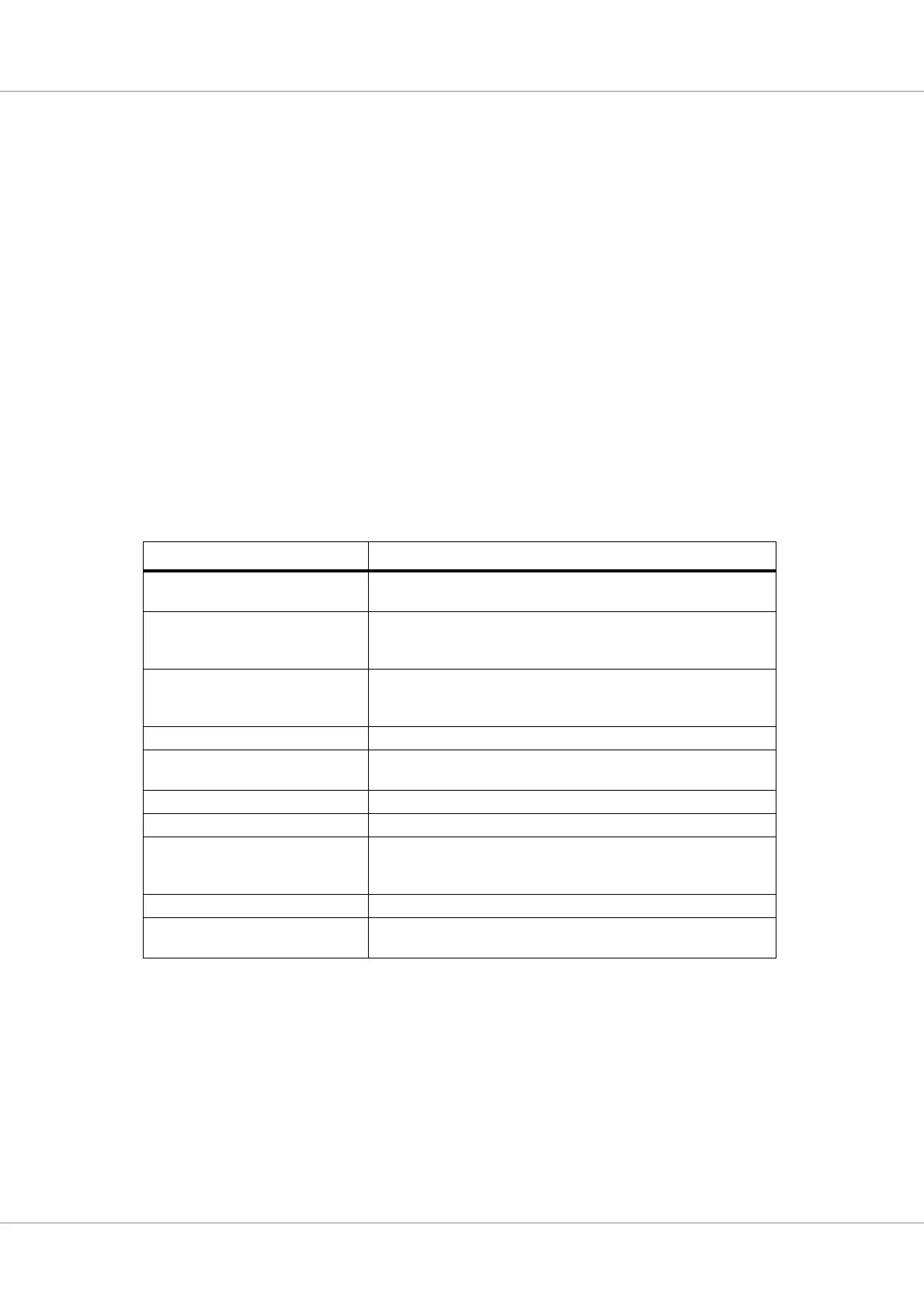

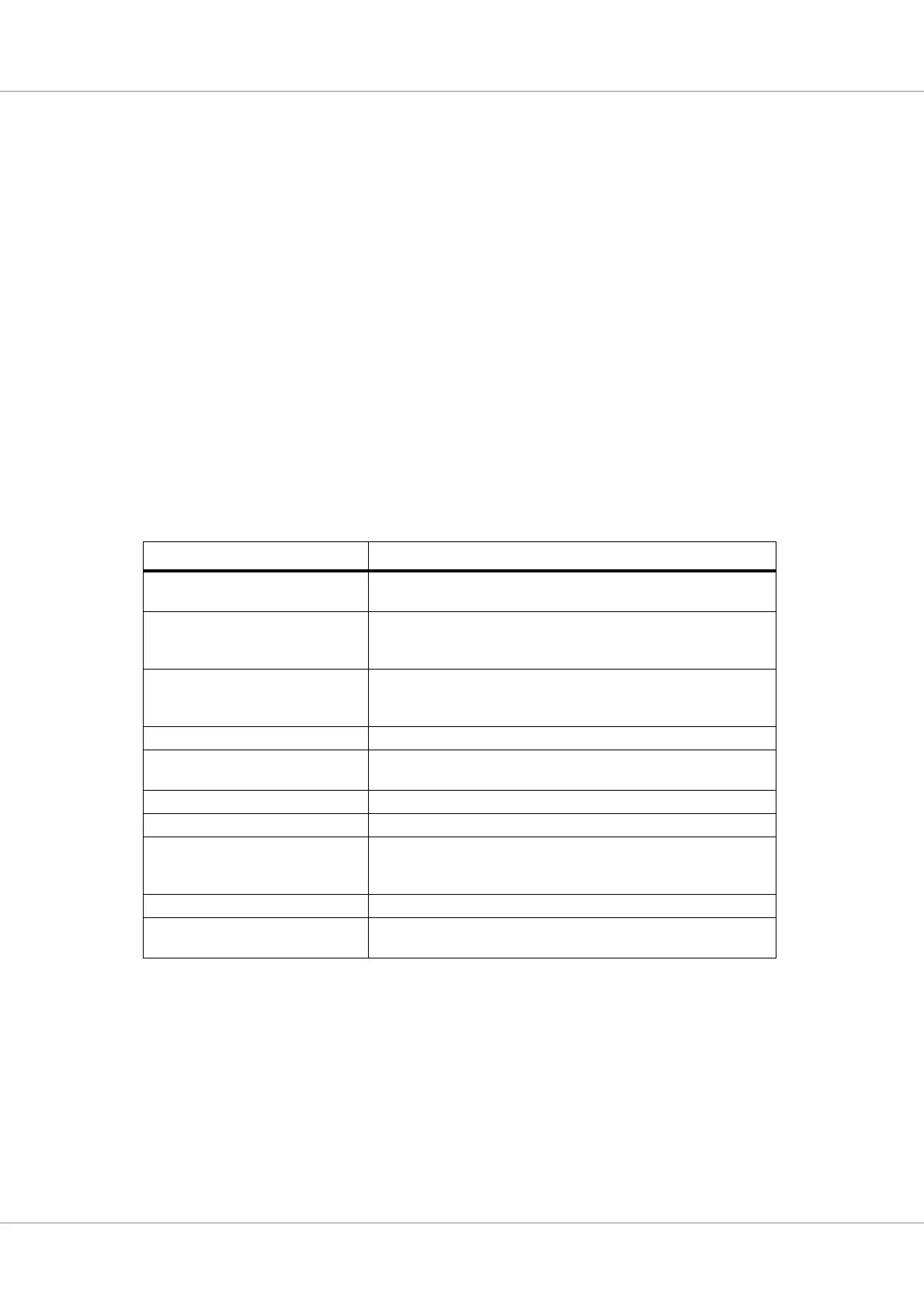

Table 516.Read and write combining

Access on slave interface Resulting access(es) on master interface

BYTE or HALF-WORD single read

access to any area

Single access of same size

BYTE or HALF-WORD read burst to

prefetchable area

Incremental read burst of same access size as on slave interface, the

length is the same as the number of 32-bit words in the read buffer, but

will not cross the read burst boundary.

BYTE or HALF-WORD read burst to

non-prefetchable area

Incremental read burst of same access size as on slave interface, the

length is the same as the length of the incoming burst. The master

interface will insert BUSY cycles between the sequential accesses.

BYTE or HALF-WORD single write Single access of same size

BYTE or HALF-WORD write burst Incremental write burst of same size and length, the maximum length

is the number of 32-bit words in the write FIFO.

Single read access to any area Single access of same size

Read burst to prefetchable area Burst of 128-bit up to 32-byte address boundary.

Read burst to non-prefetchable area Incremental read burst of same access size as on slave interface, the

length is the same as the length of the incoming burst. The master

interface will insert BUSY cycles between the sequential accesses.

Single write Single write access of same size

Write burst Burst write of maximum possible size. The bridge will use the maxi-

mum size (up to 128-bit) that it can use to empty the writebuffer.

Loading...

Loading...