GR740-UM-DS, Nov 2017, Version 1.7 350 www.cobham.com/gaisler

GR740

The extra register set, filtering, and multiple error detection is available in GR740 silicon revision 1.

The status register version in the AMBA plug&play information is also set to 1 in silicon revision 1.

27.3 Registers

The core is programmed through registers mapped into APB address space.

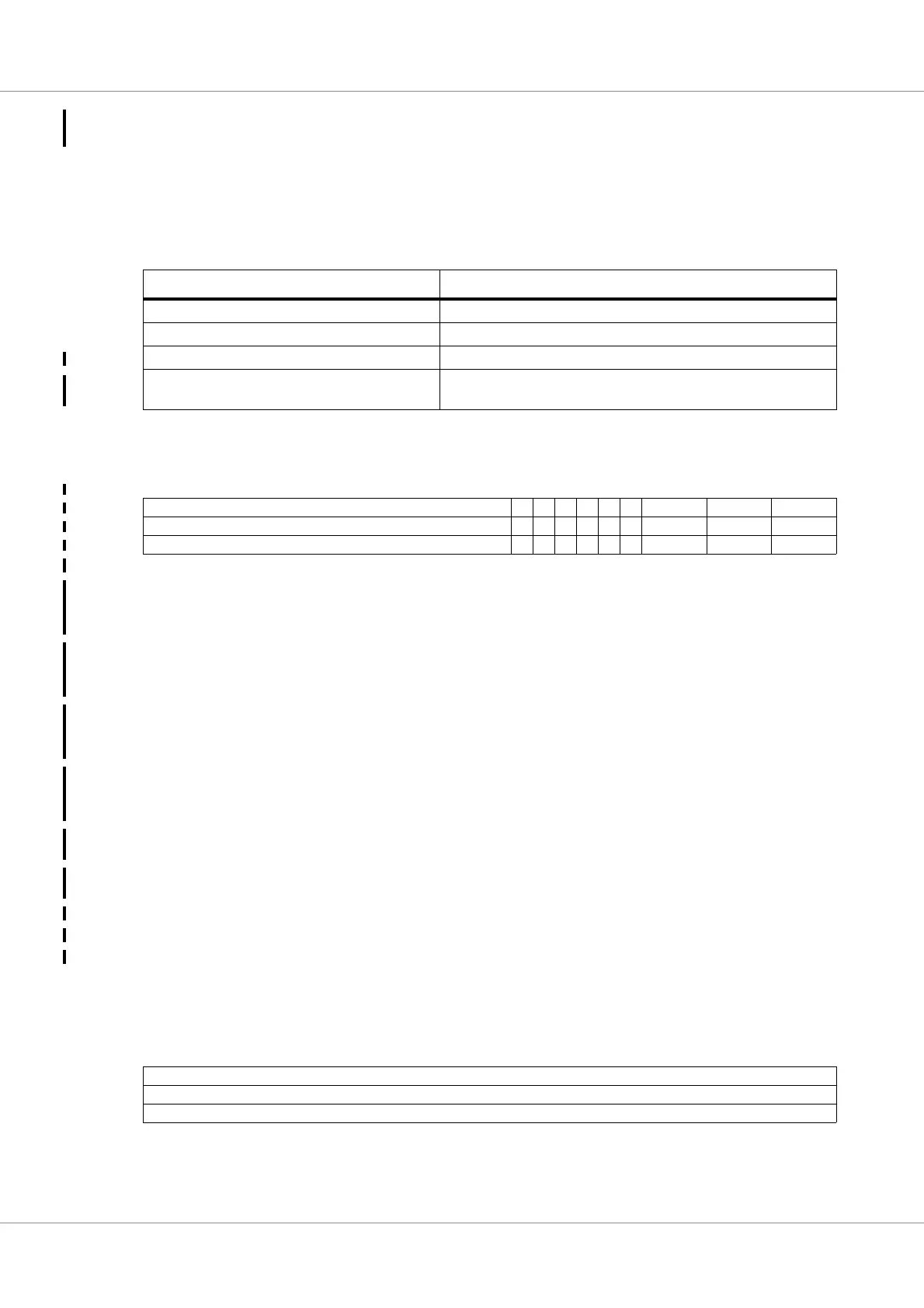

Table 441.AHB Status registers

APB address offset Registers

0x00 AHB Status register

0x04 AHB Failing address register

0x08 AHB Status register 2 (available in GR740 silicon revision 1)

0x0C AHB Failing Address register 2 (available in GR740 silicon revision

1)

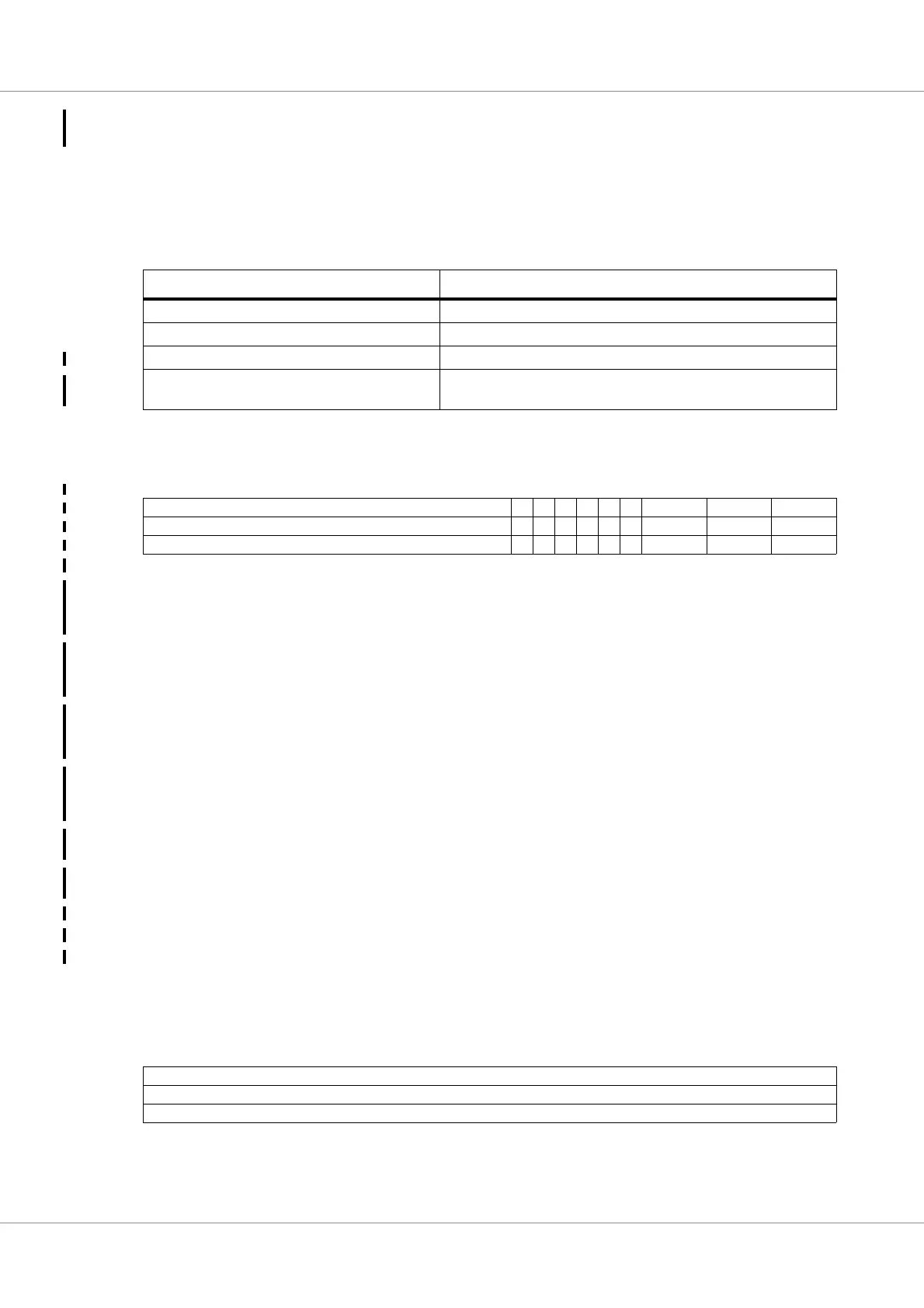

Table 442.0x00 - AHBS - AHB Status register

31 14 13 12 11 10 9 8 7 6 3 2 0

RESERVED ME FW CF AF CE NE HWRITE HMASTER HSIZE

0 000000 NR NR NR

r rw* w* rw* rw* rw rw r r r

31: 14 RESERVED

13 Multiple Error detection (ME) - This field is set to 1 when the New Error bit is set and one more

error is detected. Filtering is considered when setting the ME bit.

This field is only available in GR740 silicon revision 1.

12 Filter Write (FW) - This bit needs to be set to ‘1’ during a write operation for CF and AF fields to be

updated in the same write operation. Always reads as zero.

This field is only available in GR740 silicon revision 1.

11 Correctable Error Filter (CF) - If this bit is set to 1 then this status register will ignore correctable

errors. This field will only be written if the FW bit is set.

This field is only available in GR740 silicon revision 1.

10 AMBA ERROR Filter (AF) - If this bit is set to 1 then this status register will ignore AMBA

ERROR. This field will only be written if the FW bit is set.

This field is only available in GR740 silicon revision 1.

9 Correctable Error (CE) - Set if the detected error was caused by a correctable error and zero other-

wise.

8 New Error (NE) - Deasserted at start-up and after reset. Asserted when an error is detected. Reset by

writing a zero to it.

7 The HWRITE signal of the AHB transaction that caused the error.

6: 3 The HMASTER signal of the AHB transaction that caused the error.

2: 0 The HSIZE signal of the AHB transaction that caused the error

Table 443.0x04 - AHBFAR - AHB Failing address register

31 0

HADDR

N/R

r

31: 0 Failing address (HADDR) - The HADDR value of the AHB transaction that caused the error.

Loading...

Loading...