GR740-UM-DS, Nov 2017, Version 1.7 224 www.cobham.com/gaisler

GR740

15.3 Operation

15.3.1 Access support

The core supports both single and burst accesses on the AMBA AHB bus and on the PCI bus. For

more information on which PCI commands that are supported, see the PCI target section and for burst

limitations see the Burst section.

15.3.2 FIFOs

The core has separate FIFOs for each data path: PCI target read, PCI target write, PCI master read,

PCI master write, DMA AHB-to-PCI, and DMA PCI-to-AHB.

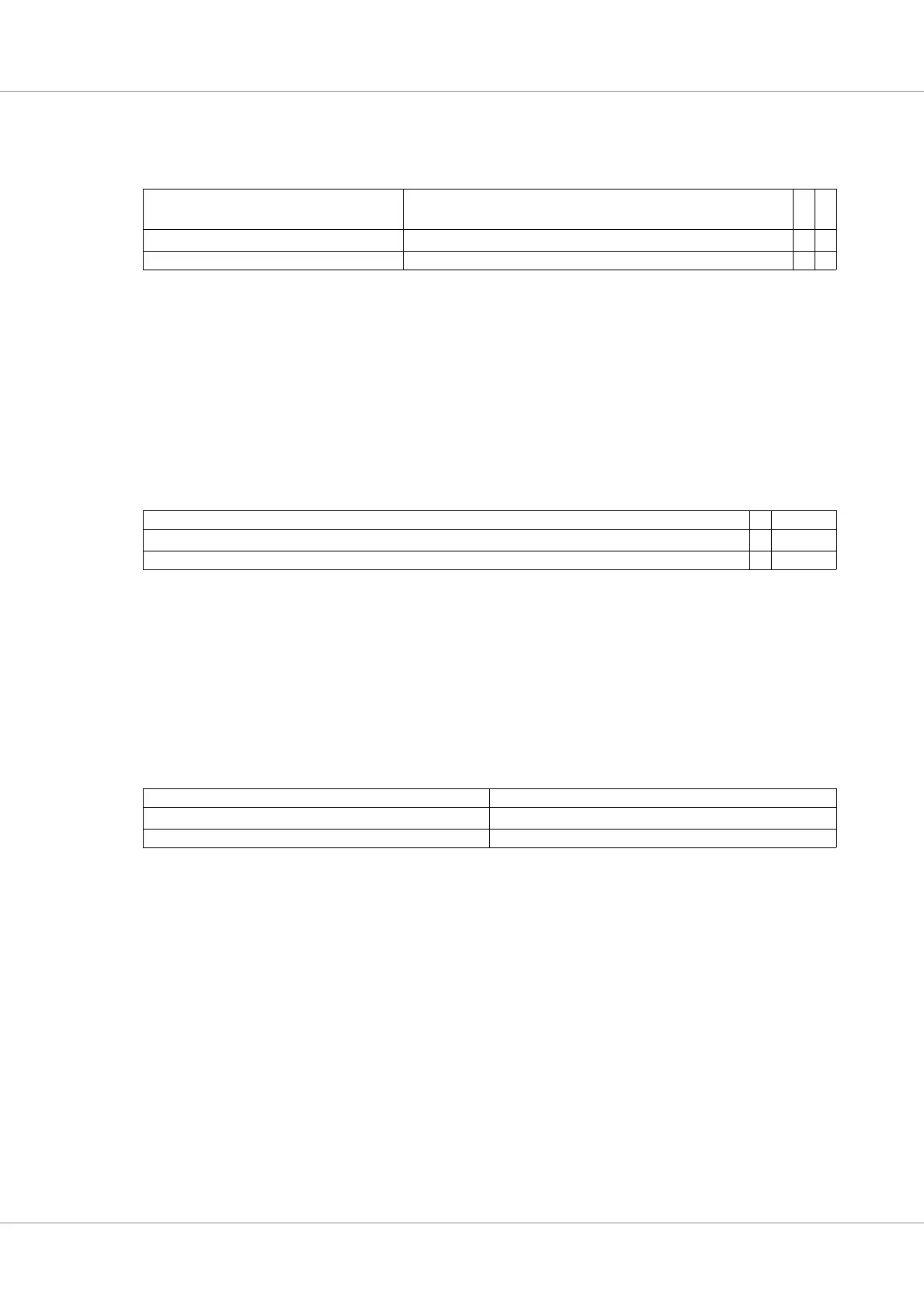

Table 260.0x20 - AHB IO base address and PCI bus config (endianess register)

31 20 19 210

AHB IO base address RESERVED DIS

EN

EN

DIA

N

*

000

r r rw rw

31: 20 Base address of the AHB IO area

19: 2 RESERVED

1 Target access discard time out enable (DISEN) - When set to ‘1’, the target will discard a pending

access if no retry of the access is detected during 2**15 PCI clock cycles.

0 PCI bus endianess switch (ENDIAN) - 1: defines the PCI bus to be little-endian, 0: defines the PCI

bus to be big-endian

Table 261.0x24-0x38 - PCI BAR size and prefetch register

31 432 0

PCI BAR size mask PF RES

*

*0

rw rw r

31: 4 PCI BAR size mask - A size mask register for each PCI BAR. When bit[n] is set to ‘1’ bit[n] in the

PCI BAR register is implemented and can return a non-zero value. All bits from the lowest bit set to

‘1’ up to bit 31 need to be set to ‘1’. When bit 31 is ‘0’, this PCI BAR is disabled.

3 Prefetch bit (PF) - Prefetch bit in PCI BAR register

2: 0 RESERVED

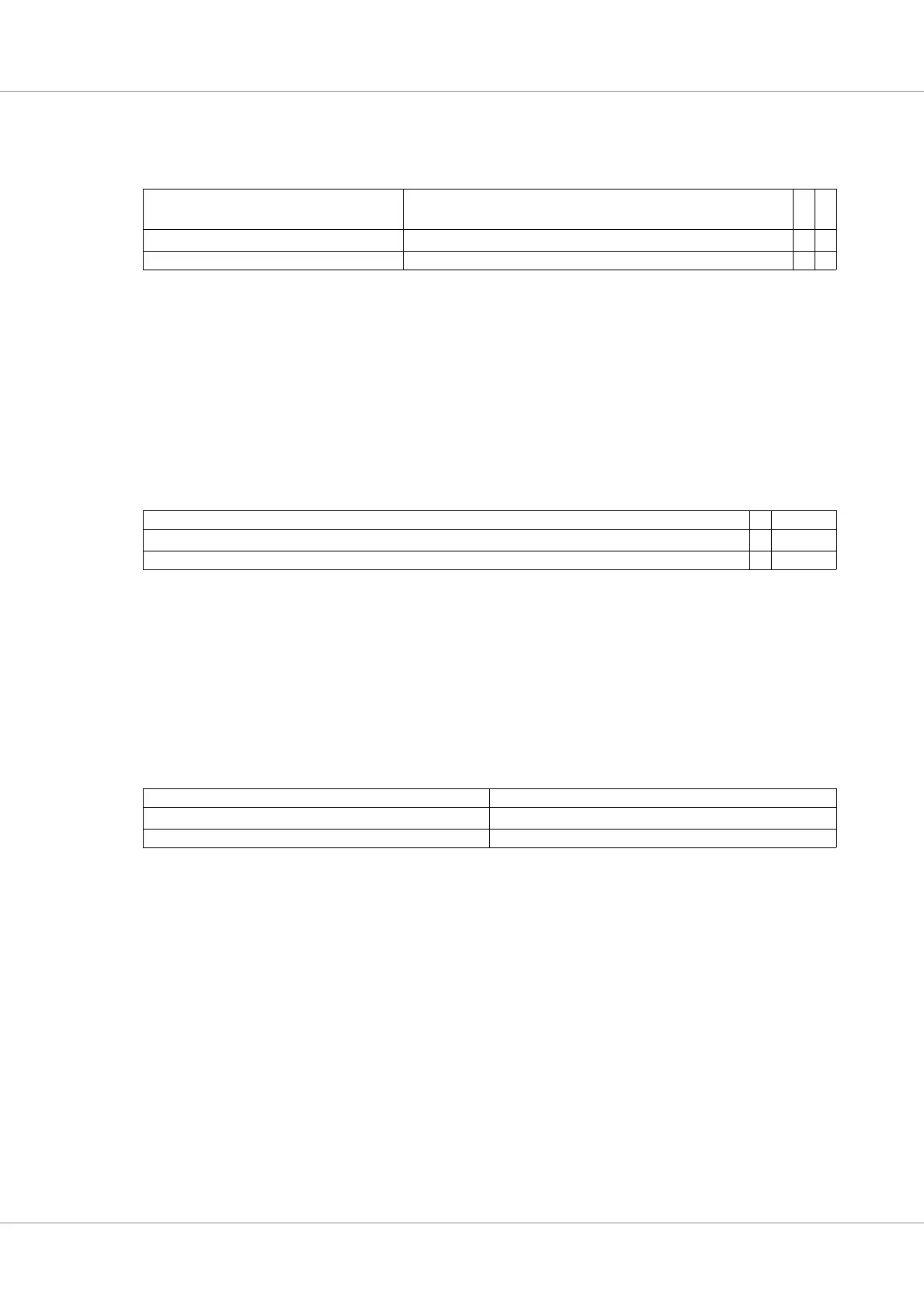

Table 262.0x3C - AHB master burst limit

31 16 15 0

RESERVED Burst length

0 0xFFFF

rrw

31: 16 RESERVED

15: 0 Burst length

- Maximum number of beats - 1 in the burst. (Maximum value is 0xFFFF => 0x10000

beats => 64 KiB address)

Loading...

Loading...