GR740-UM-DS, Nov 2017, Version 1.7 85 www.cobham.com/gaisler

GR740

8.2.6 Non-standard Mode

GRFPU can operate in a non-standard mode where all denormalized operands to arithmetic and con-

version operations are treated as (correctly signed) zeroes. Calculations are performed on zero oper-

ands instead of the denormalized numbers obeying all rules of the floating-point arithmetics including

rounding of the results and detecting exceptions.

8.2.7 NaNs

GRFPU supports handling of Not-a-Numbers (NaNs) as defined in the IEEE-754 standard. Opera-

tions on signaling NaNs (SNaNs) and invalid operations (e.g. inf/inf) generate the Invalid exception

and deliver QNaN_GEN as result. Operations on Quiet NaNs (QNaNs), except for FCMPES and

FCMPED, do not raise any exceptions and propagate QNaNs through the FP operations by delivering

NaN-results according to table 64. QNaN_GEN is 0x7fffe00000000000 for double precision results

and 0x7fff0000 for single precision results.

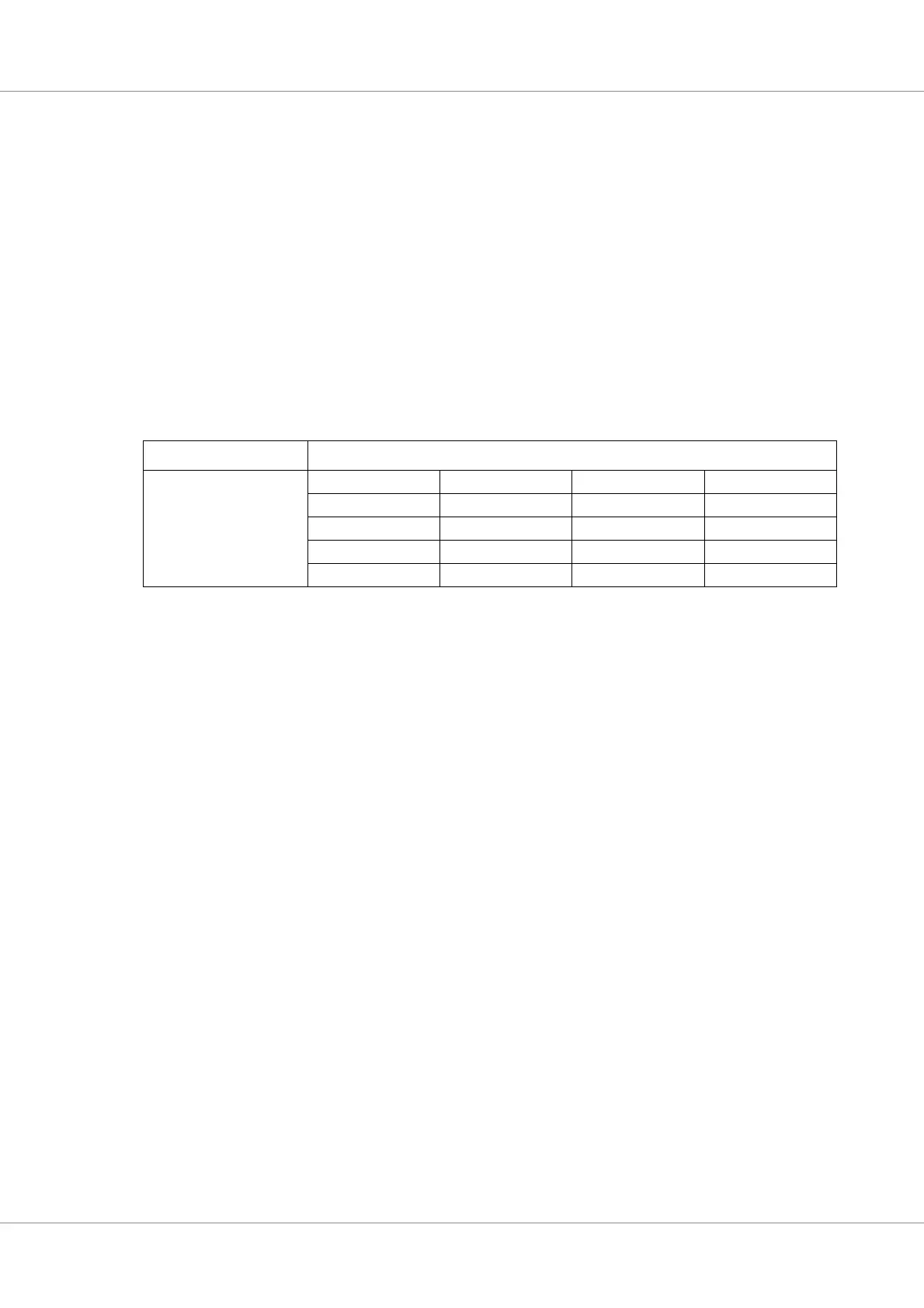

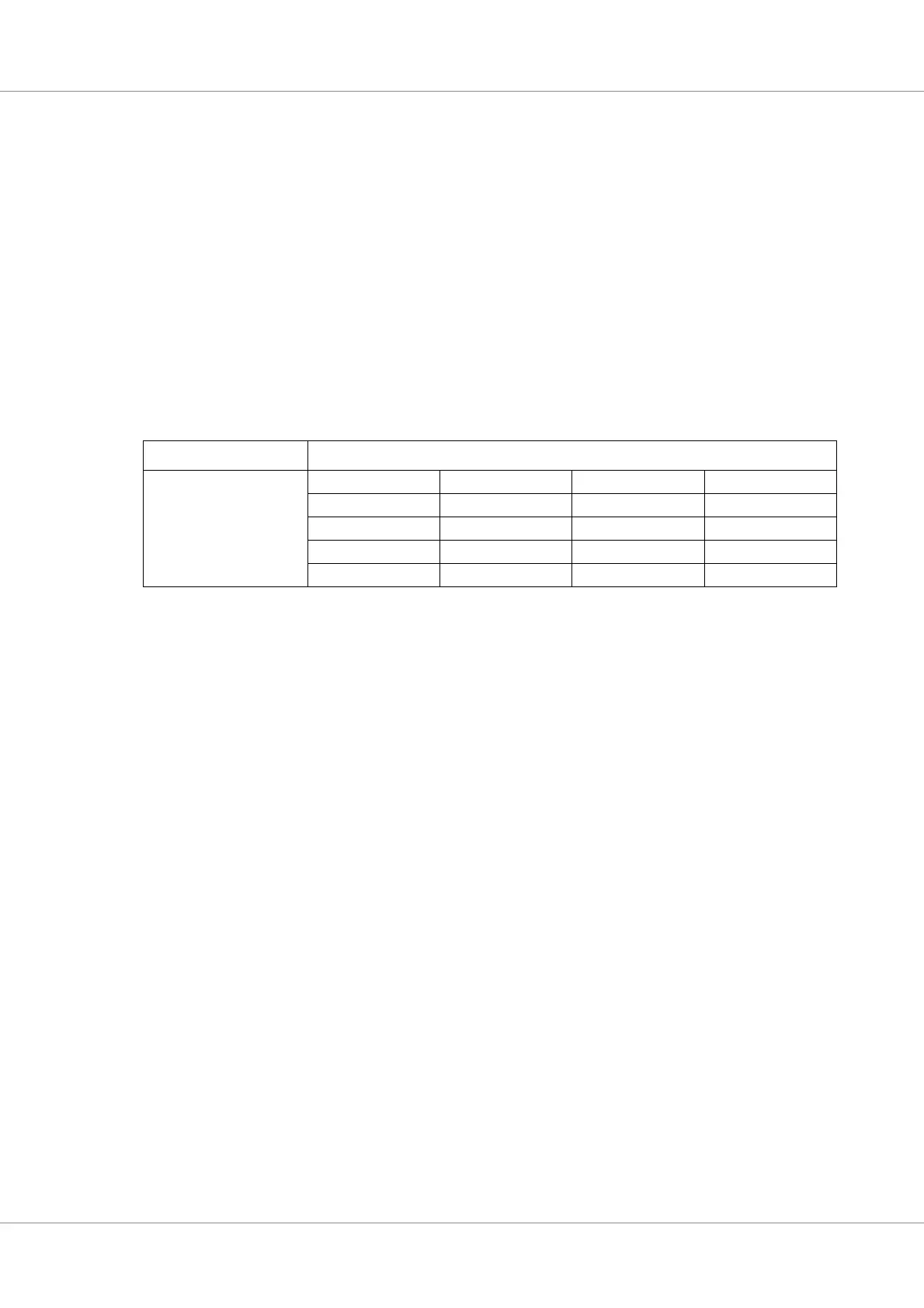

Table 64. : Operations on NaNs

Operand 2

Operand 1

FP QNaN2 SNaN2

none FP QNaN2 QNaN_GEN

FP FP QNaN2 QNaN_GEN

QNaN1 QNaN1 QNaN2 QNaN_GEN

SNaN1 QNaN_GEN QNaN_GEN QNaN_GEN

Loading...

Loading...